mmcm动态配置

XAPP888 MMCM

https://fpga.eetrend.com/files-eetrend-xilinx/download/201307/4239-8635-xapp8887seriesdynamicrecon.pdf

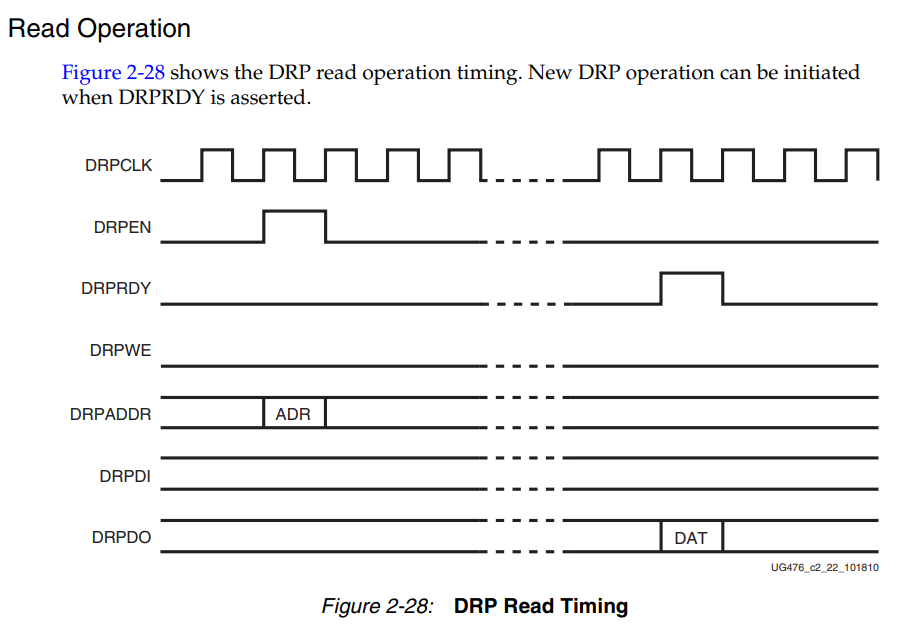

DRP配置时序

UG476

https://docs.amd.com/v/u/en-US/ug476_7Series_Transceivers

“ FPGA设计中,时钟频率、占空比、相位的动态调节不是多么常用的功能,也不是什么很冷门的功能。本文将详细介绍mmcm频率的动态配置,占空比、相位的动态配置与频率类似只是所需配置寄存器的差异。”

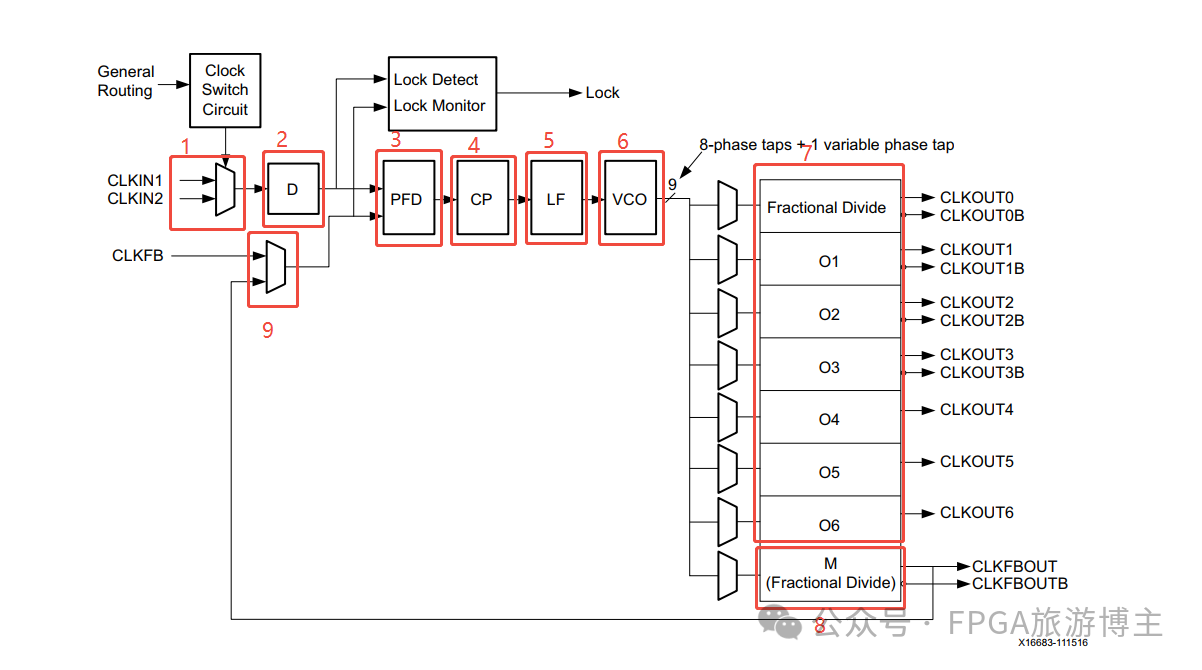

01.mmcm的整体框架

从xilinx给出的框图来看mmcm主要由以下9个部分构成,对应标记出来的阿拉伯数字1~9:

1)、输入时钟选择器。对应源语中的CLKINSEL端口,1bit位宽,值1表示选择clkin1,值0表示选择clkin2。只有mmcm上存在输入时钟选择器,pll上没有;

2)、输入时钟分频器。也叫主时钟分频器,作用是对输入时钟做分频;

3)、相位、频率检测器(phase-frequency detector)。检测reference和feedback时钟频率、相位的差异,生成一个正比于差异的信号去驱动电荷泵;

4)、电荷泵(charge pump)。根据pfd给过来的驱动信号,进行充电、放电,实现电压控制vco的目的。

5)、环路滤波器(loop filter)。对cp给过来的电压信号进行滤波,最终给出到vco。

6)、压控振荡器(voltage-controlled oscillator)。基于电子期间的非线性特性,通过改变输入电压来调整输出信号的频率。顾名思义,可以通过改变电压来改变vco的输出频率;

7)、分频器(divider)。8路输出,对应8个分频器,可独立对vco的输出进行分频,分频器可编程。out0和fbout支持小数倍、整数倍分频,out1- out6只支持整数倍分频。

9)、倍频器(multiplier)。

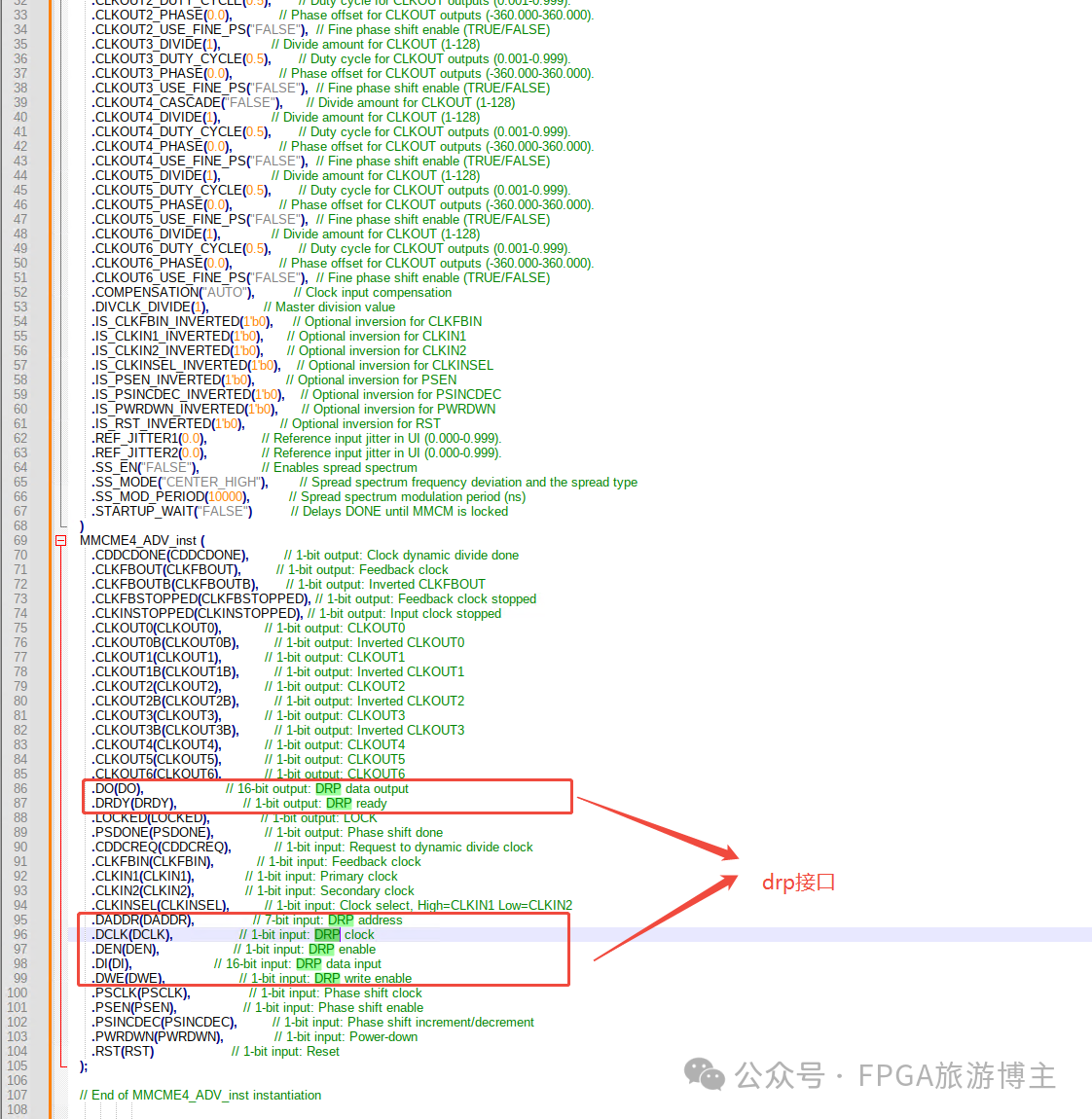

9个主要组成部分当中,某些部分是固定的电路,用户不可编程,例如鉴相鉴频器(也叫相位、频率检测器)PFD、电荷泵CP、环路滤波器LF、压控振荡器VCO等;可配置部分在源语中的对应位置,如下:

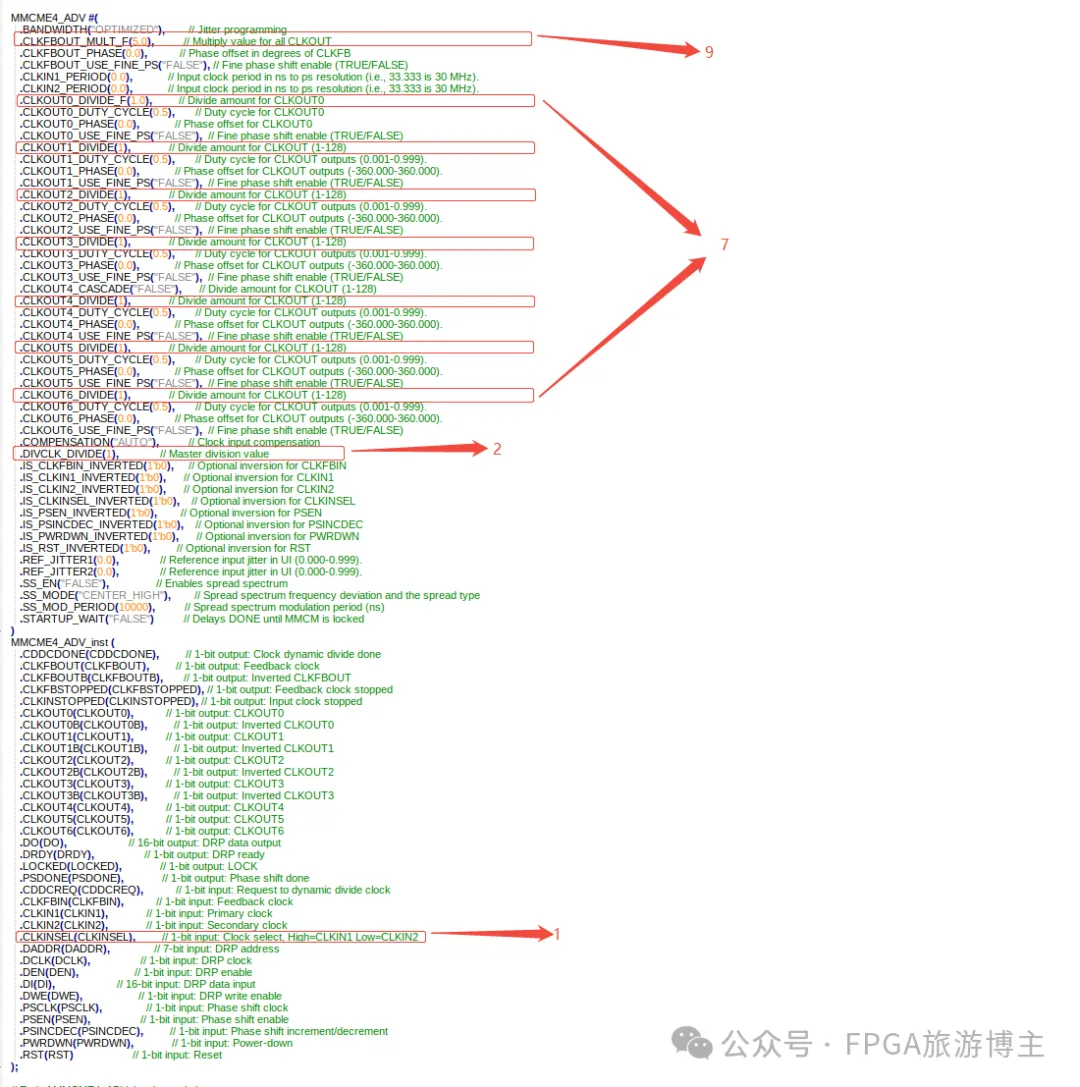

注意:mmcm源于只有高级模式(mmcm_adv)才有动态配置接口drp,基础版本(mmcm_base)没有动态配置接口。

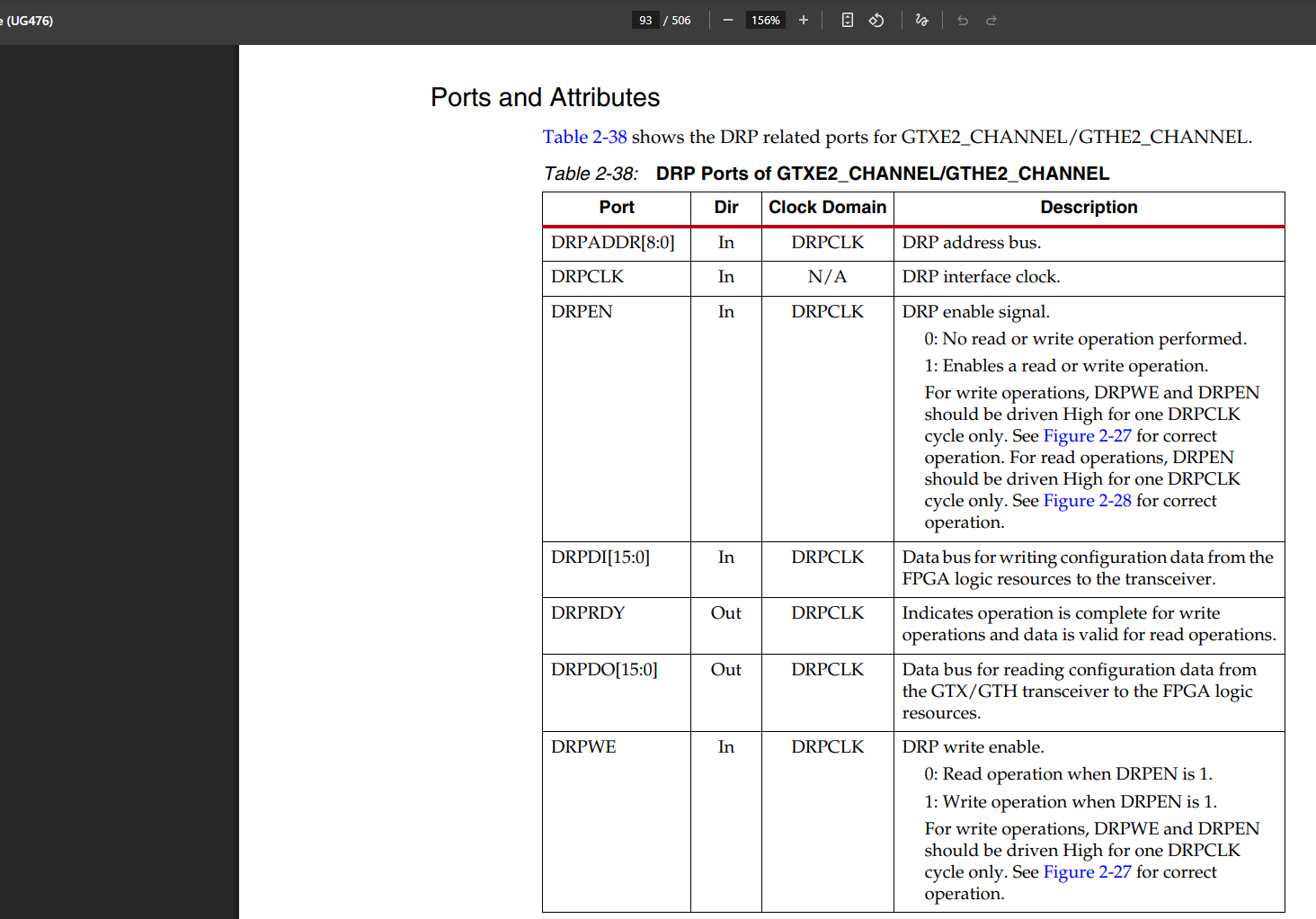

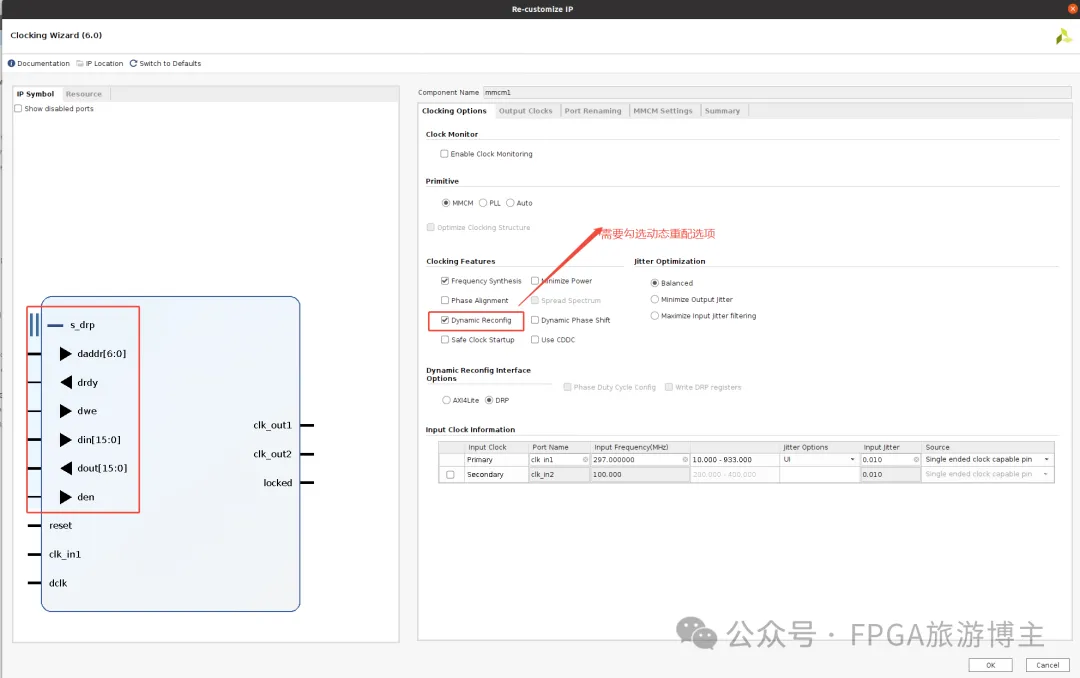

2.动态配置接口

动态重配置接口drp(dynamic reconfiguration port),支持mmcm、pll的相位、频率、占空比动态重配。mmcm、pll的ip模式、源语模式均能调出drp接口。如果使用源语方式,则只有高级模式的源语才能调出drp接口,即mmcm_adv和pll_adv可以有drp接口,mmcm_base和pll_base没有drp接口。

ip模式下的drp接口

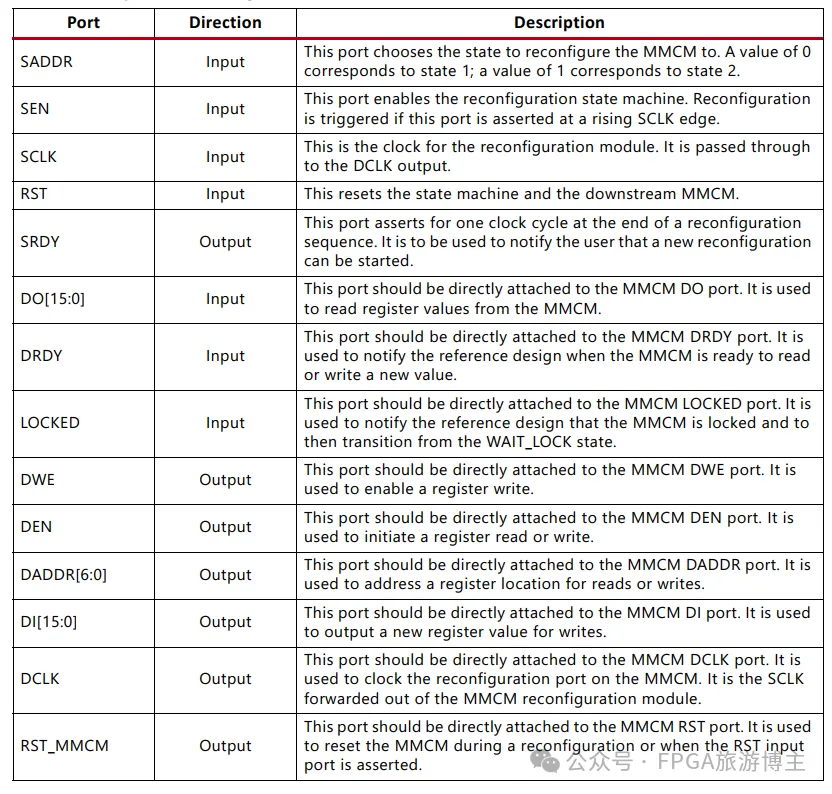

各接口的定义如下:

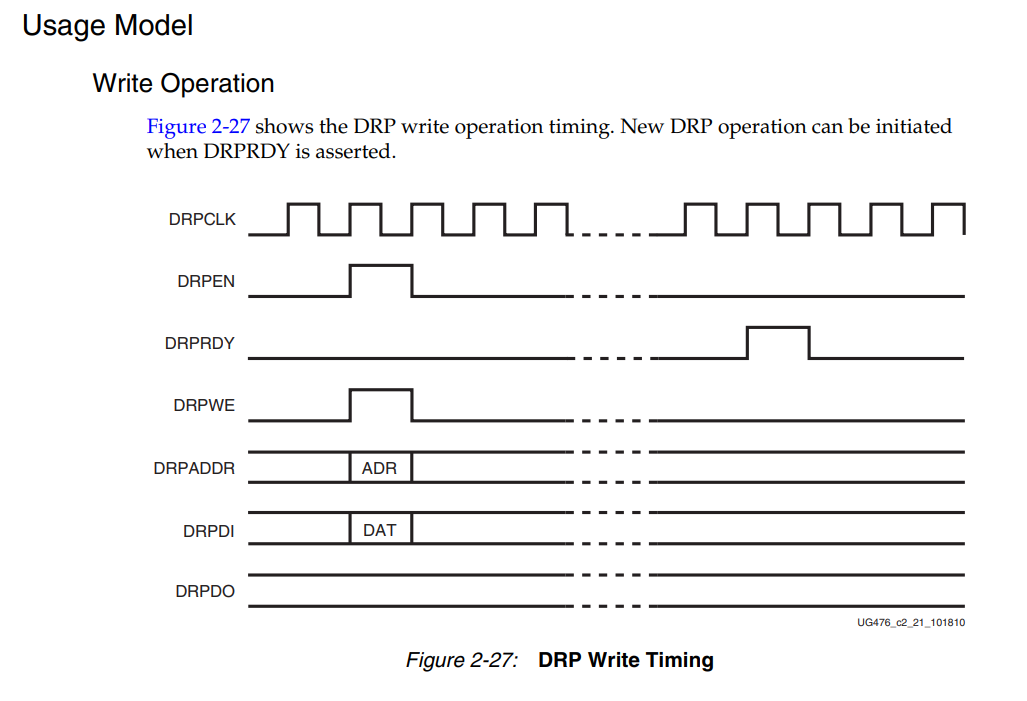

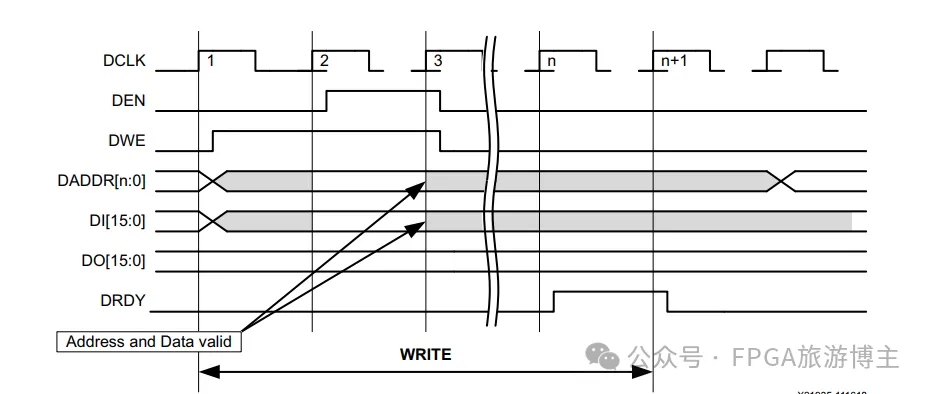

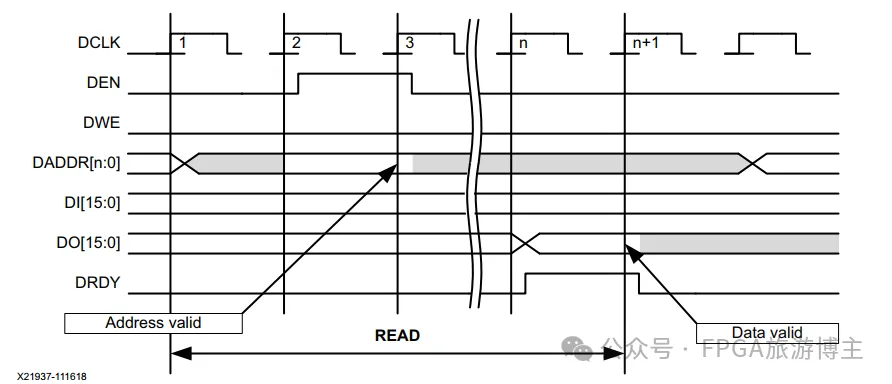

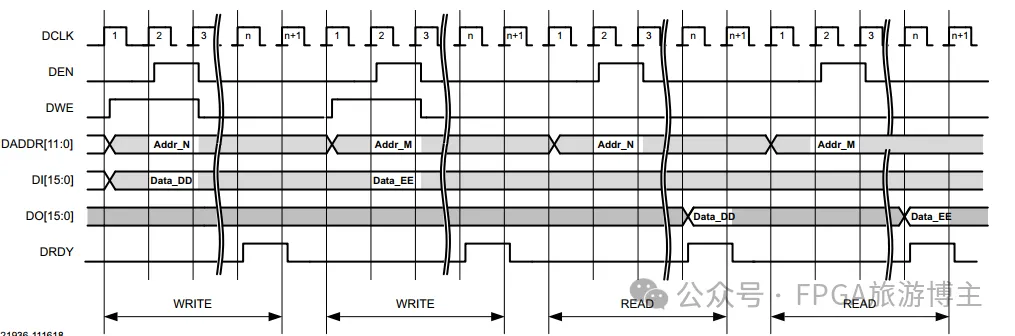

03.drp读写时序

写时序

读时序

读写时序

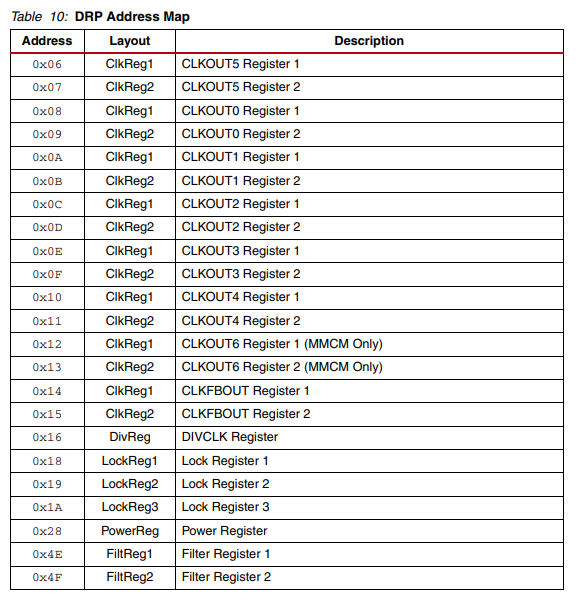

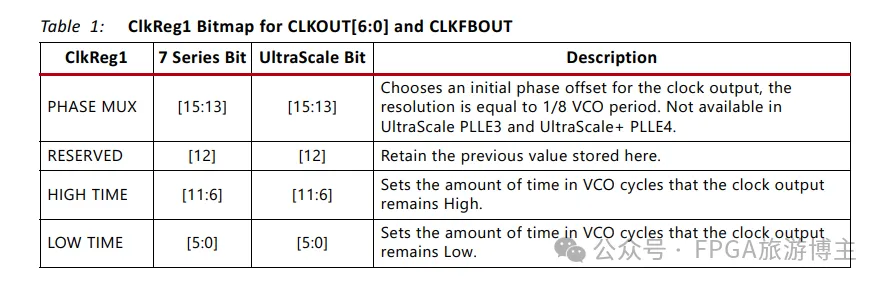

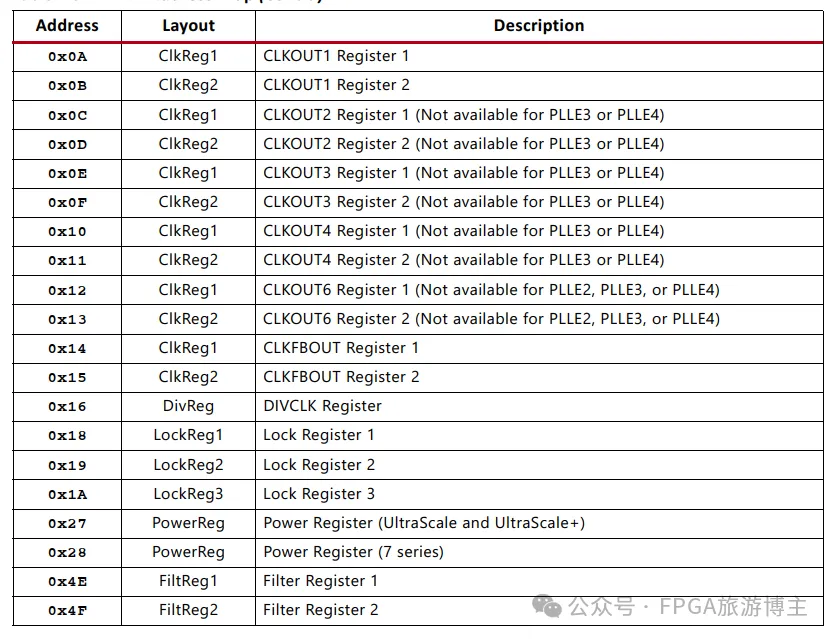

04.drp相关寄存器

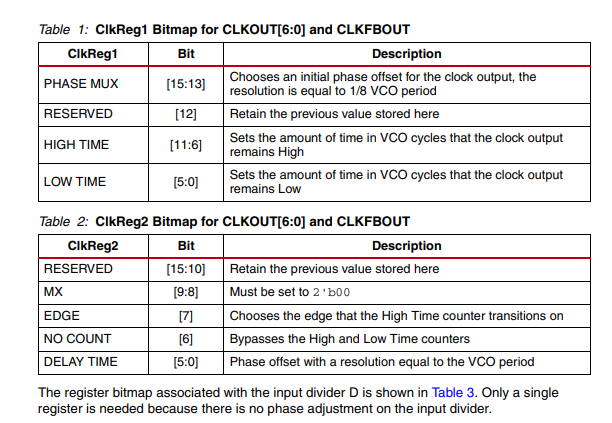

drp相关寄存器总体可分为两类,用xilinx的话来说就是reg1和reg2。

reg1功能主要是分频系数、占空比的调节。

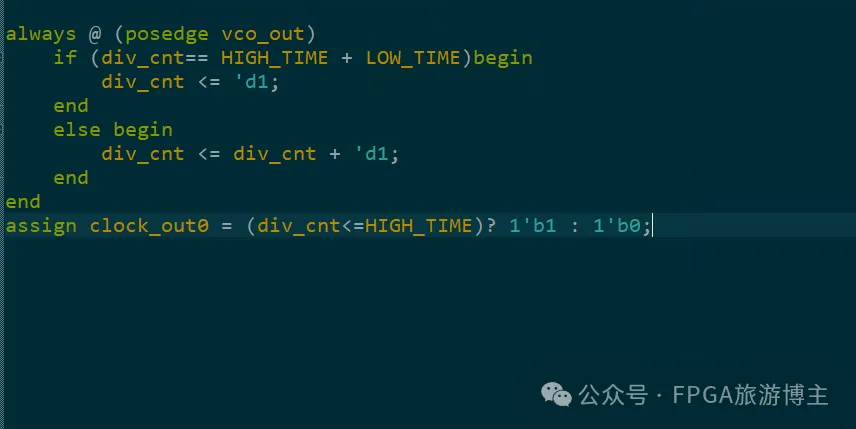

分频的底层原理是对vco的输出进行分频,类似于将vco输出当做时钟,根据high time和low time 产生pwm波形,这个pwm就是用户需要的经过分频后的时钟。以下伪代码是博主对分频功能的揣测,具体情况xilinx也没给出,所以只能说是揣测。实际mmcm里的分频肯定是固定电路实现的,伪代码只是方便理解reg1是怎么去实现分频功能。

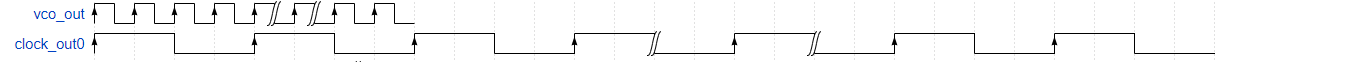

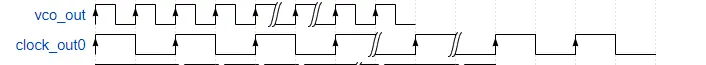

假设high time为2 ,low time为2,实现4分频,占空比50%,vco_out和clock_out0的关系如下:

假设high time为3 ,low time为1,实现4分频,占空比75%,vco_out和clock_out0的关系如下:

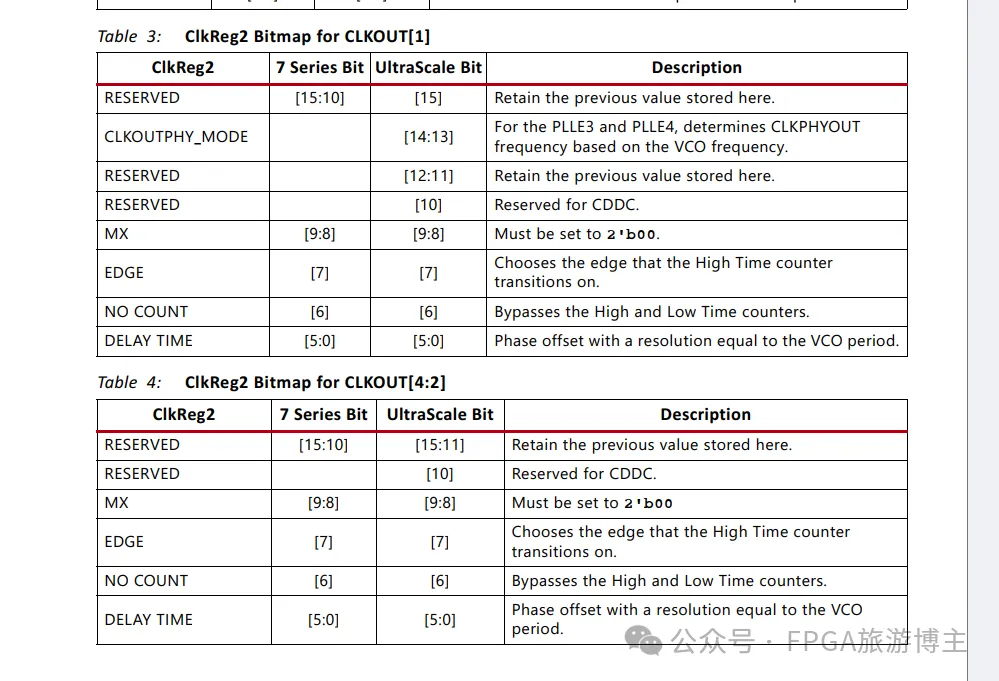

reg2功能主要相位调节,不同clock输出通道之间reg2的定义有些许差异。

reg1、reg2个输出通道之间的地址偏移如下:

05.应用举例

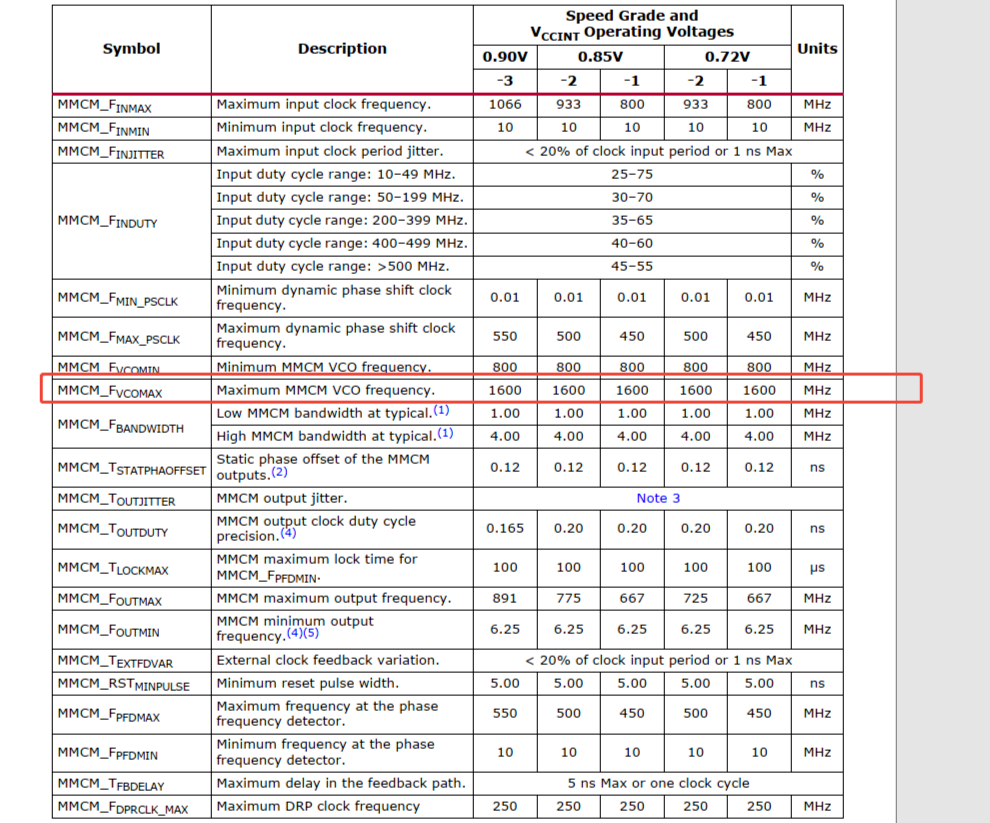

以148.5m输入,clock_out0分别1倍频2倍频输出为例。若基于u+系列的fpga,则vco的输出频率范围为800m~1600m:

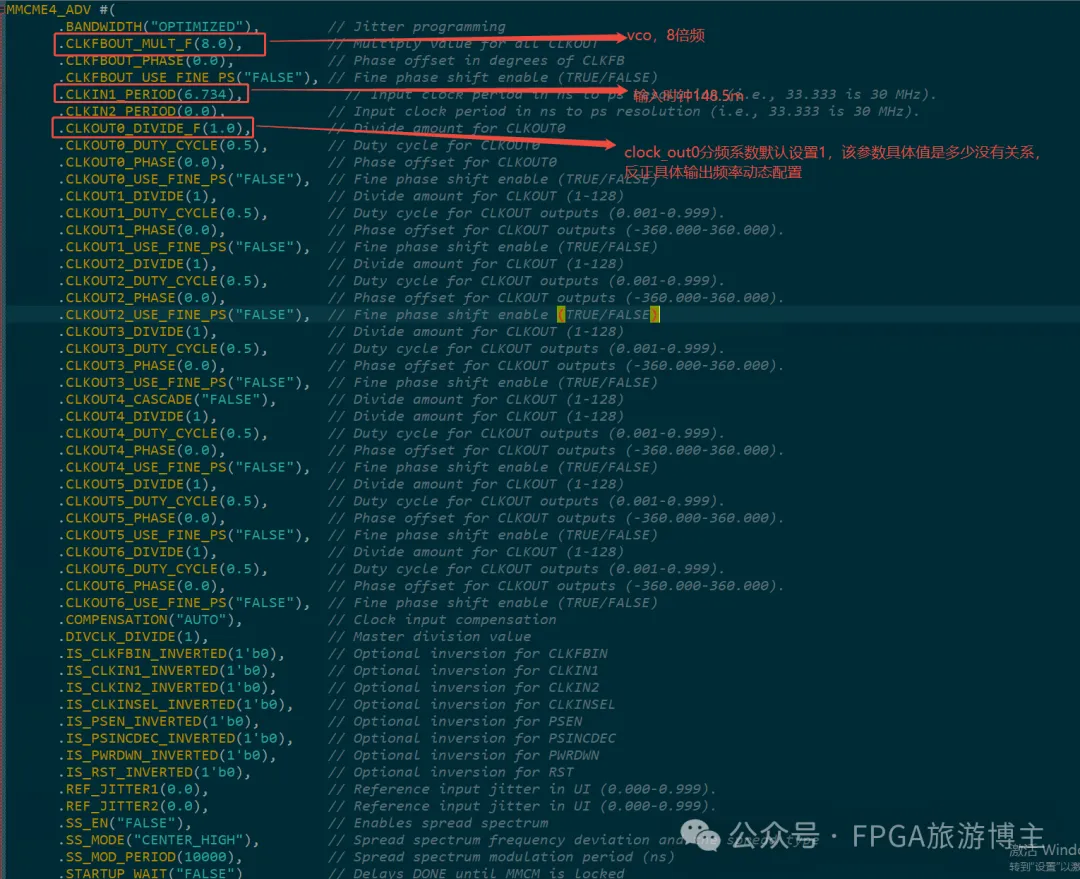

故此CLKFBOUT_MULT_F需设置为8,保证vco在正常工作范围内源于设置如下:

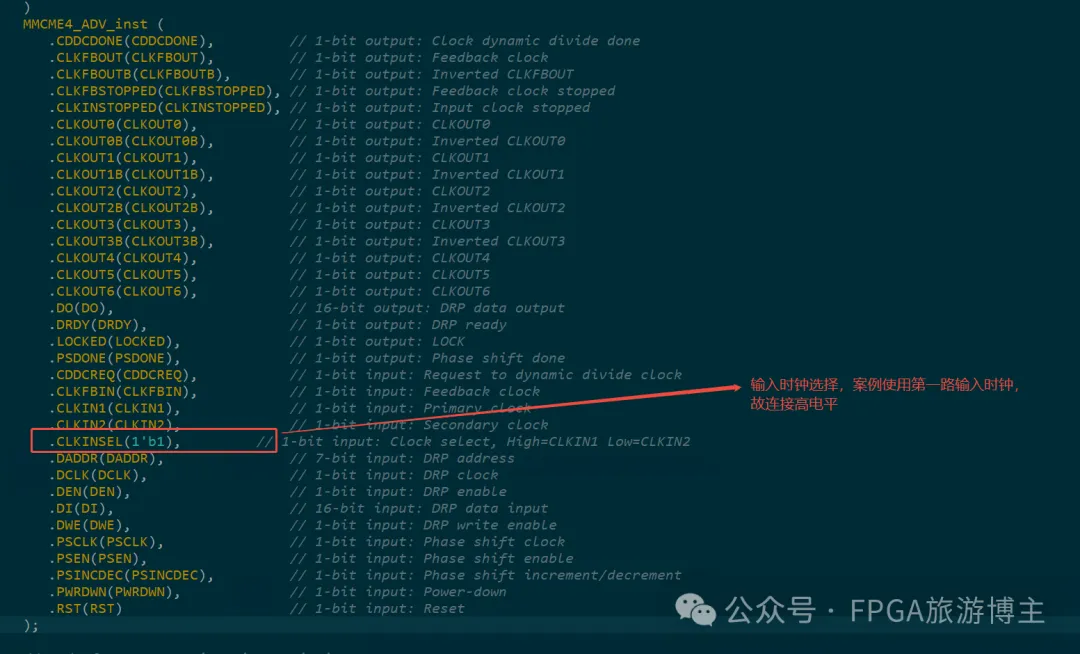

输入时钟的选择:

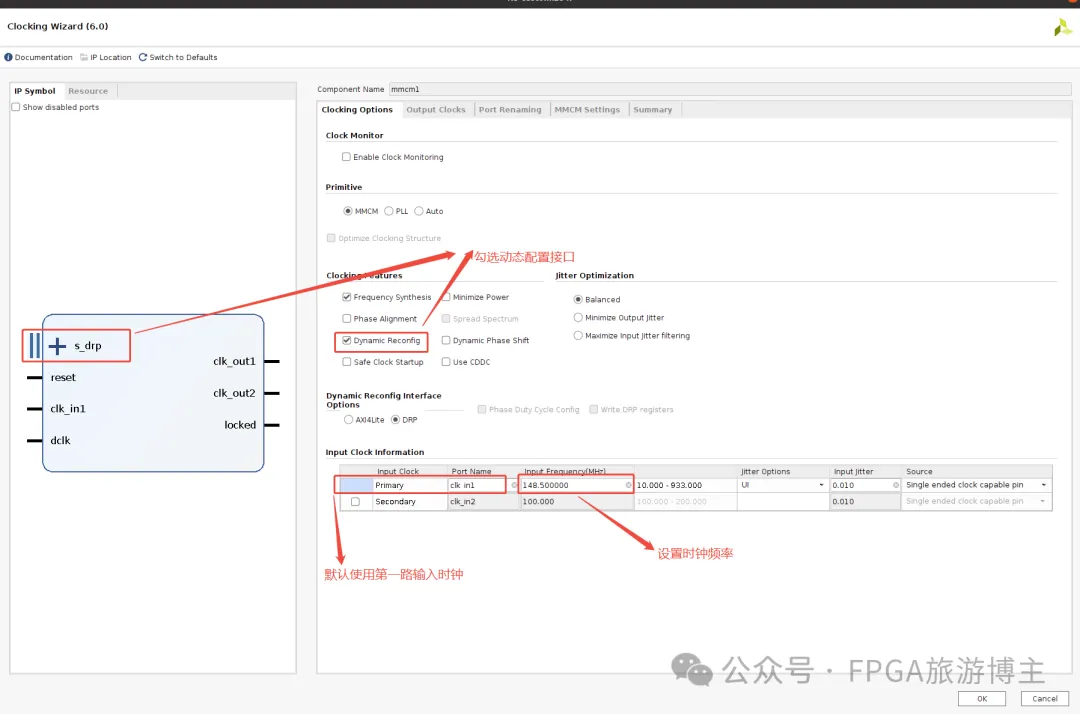

采用ip方式时设置如下:

设置输入时钟相关参数、调出drp接口

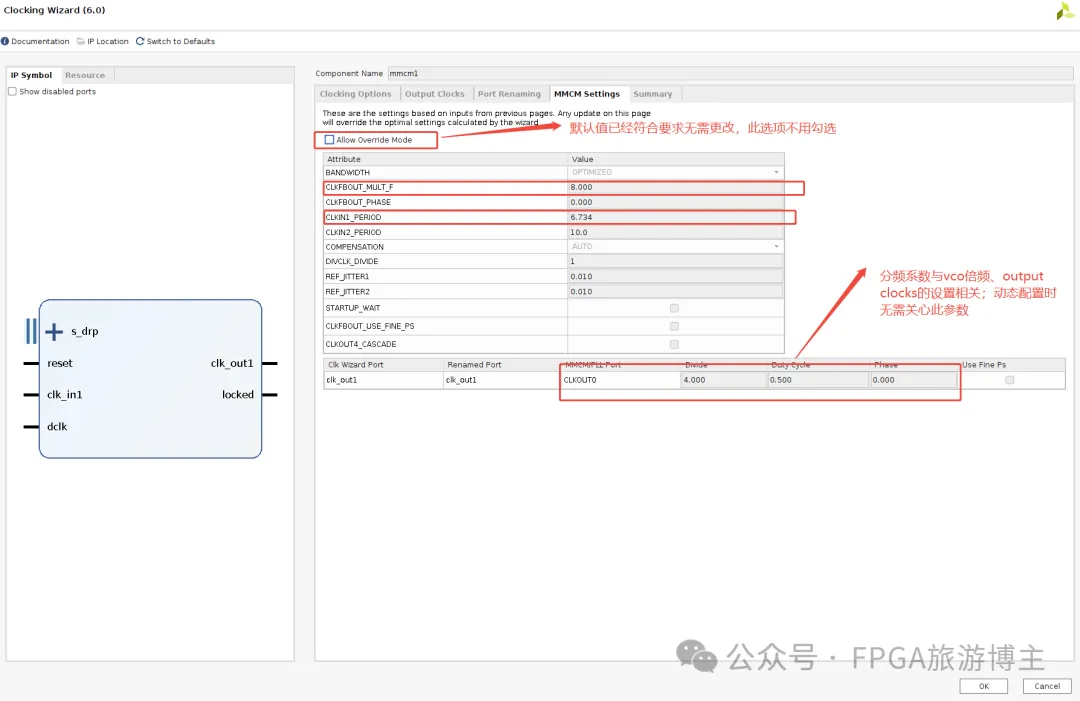

vco相关设置默认值正确,无需修改。

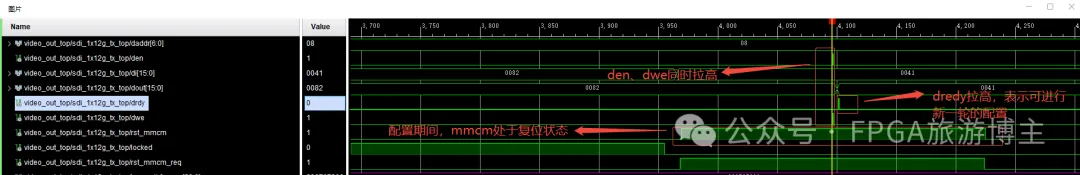

实际抓取配置时序如下:

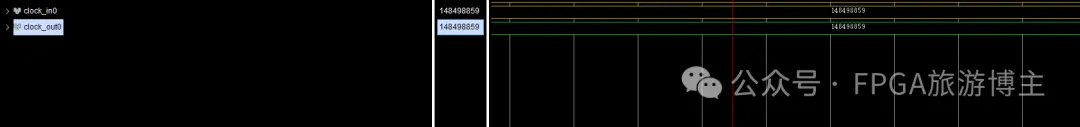

8分频时,fpga内部嵌入自行设计的频率计,检测到输入输出时钟如下图,输入、输出时钟频率相同:

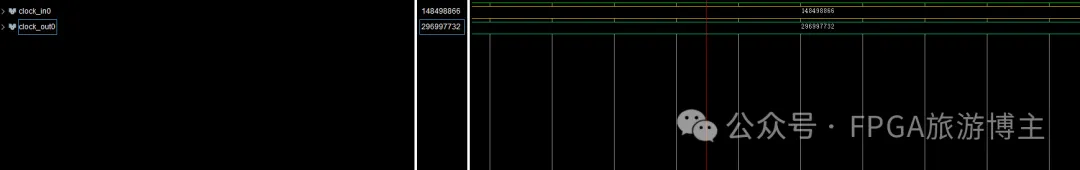

4分频时,fpga内部嵌入自行设计的频率计,检测到输入输出时钟如下图,输出时钟频率是输入时钟频率的2倍:

转载自:微信公众号-FPGA旅游博主

posted on 2026-01-13 16:21 taylorrrrrrrrrr 阅读(3) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号