VIM

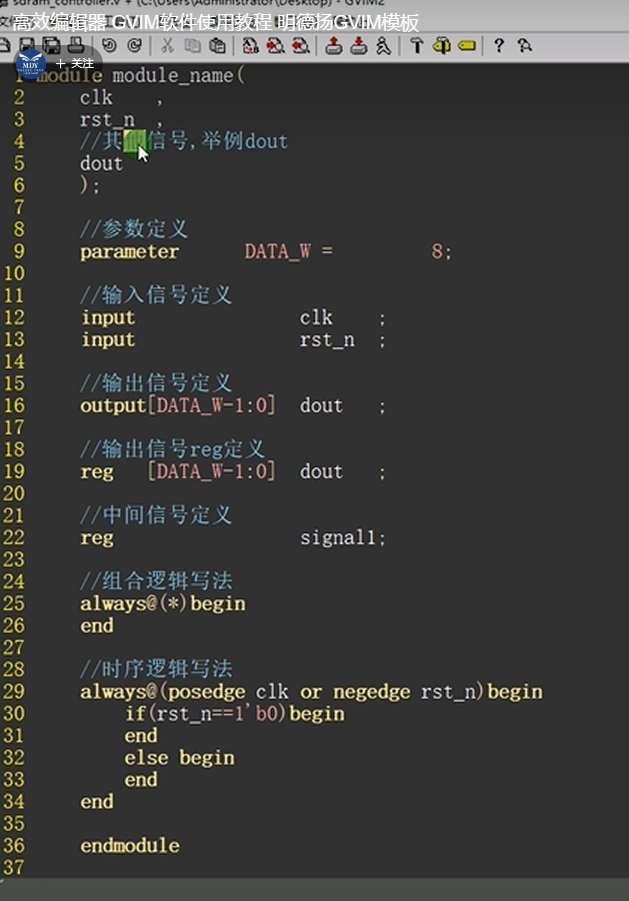

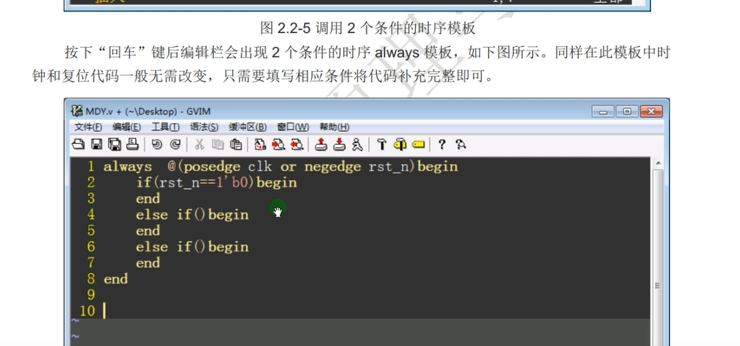

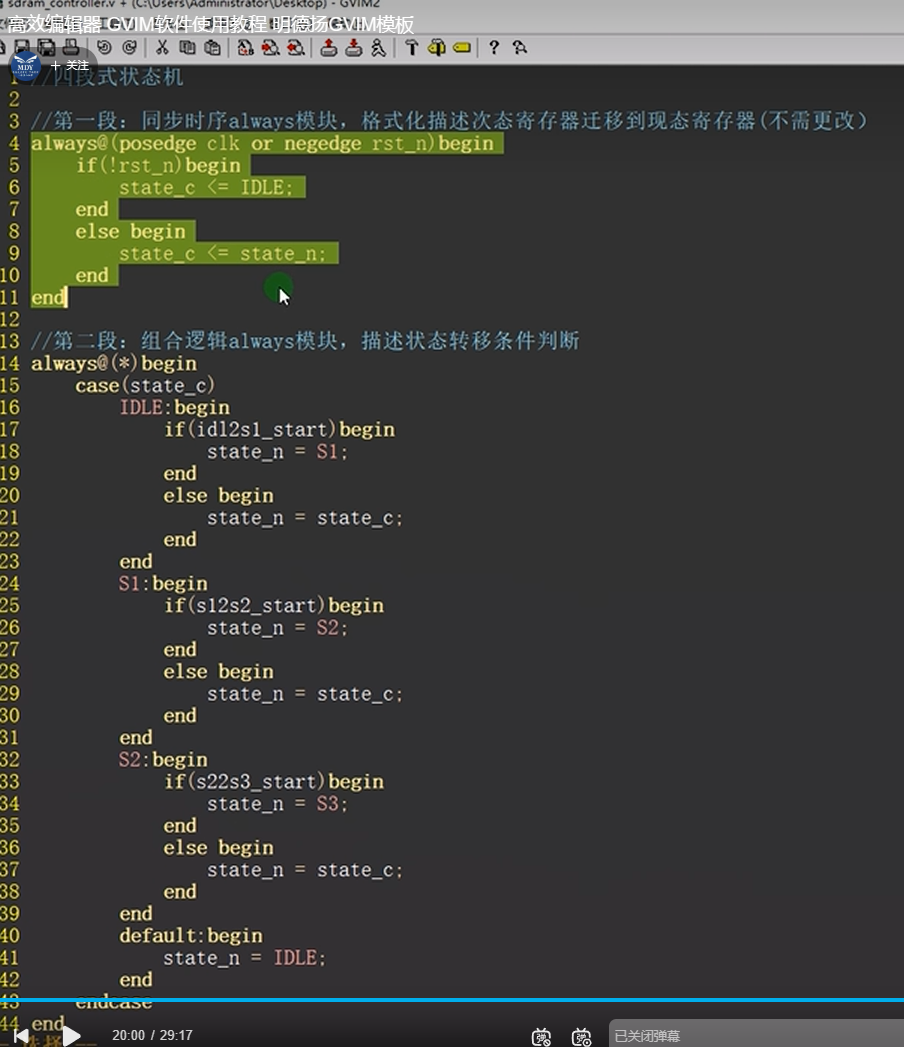

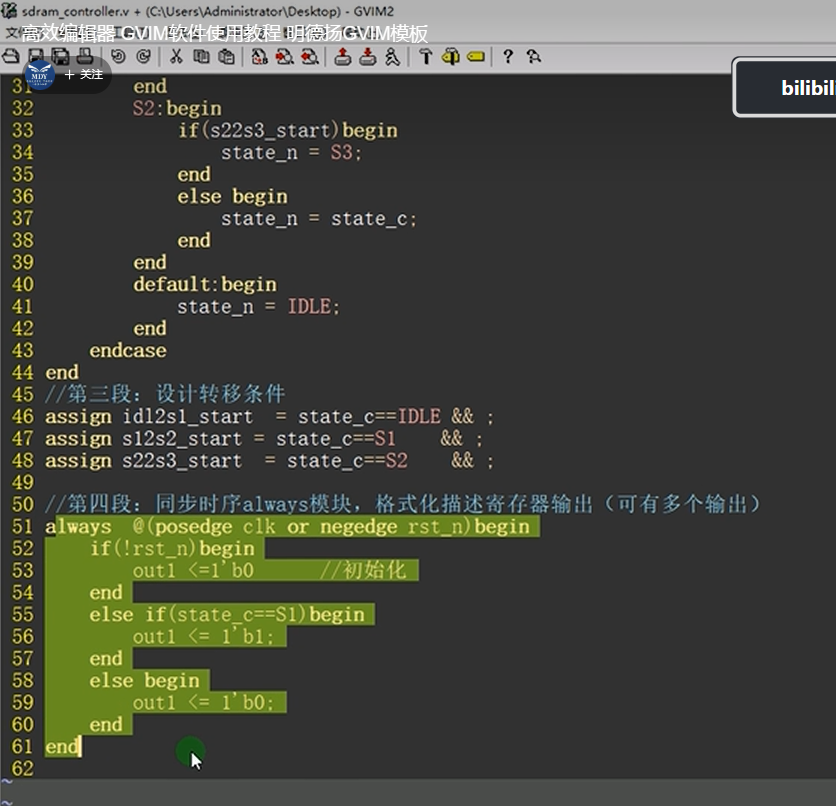

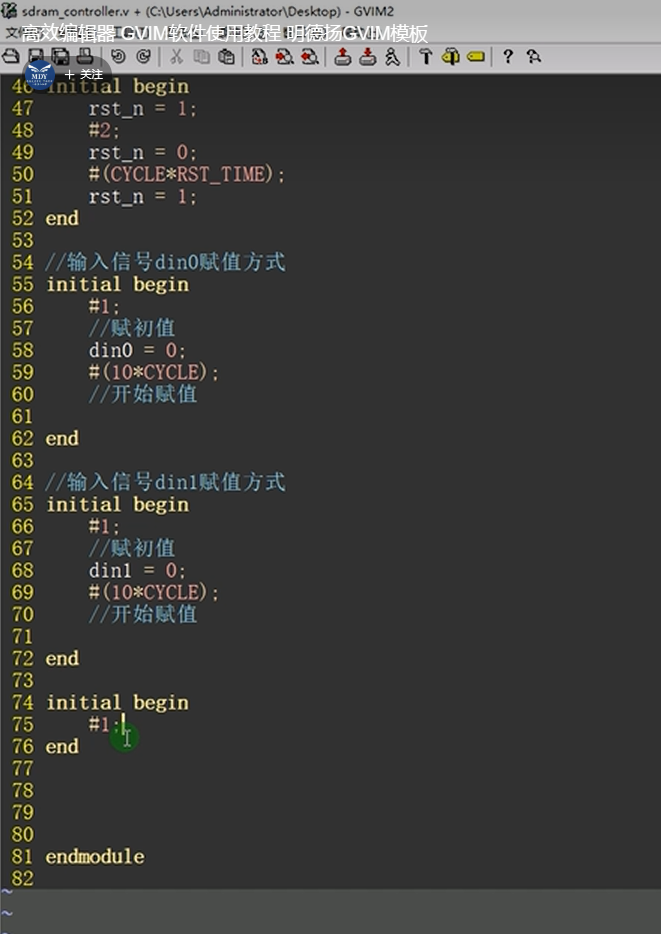

syntax enable set background=light colorscheme solarized set encoding=utf-8 set fileencodings=utf-8,ucs-bom,gb18030,gbk,gb2312,cp936 set hlsearch set nocompatible source $VIMRUNTIME/vimrc_example.vim source $VIMRUNTIME/mswin.vim "source $VIMRUNTIME/colors/desert.vim source $VIMRUNTIME/colors/solarized.vim "source $VIMRUNTIME/colors/corporation.vim "colors=light "background=corporation.vim " 开启高亮光标行 "set cursorline hi CursorLine cterm=NONE ctermbg=darkred ctermfg=white guibg=darkred guifg=white "hi CursorLine cterm=NONE ctermbg=darkred ctermfg=red guibg=darkred guifg=red " 开启高亮光标列 "set cursorcolumn hi CursorColumn cterm=NONE ctermbg=darkred ctermfg=white guibg=darkred guifg=white set guicursor=n-v-c:block-Cursor/lCursor,ve:ver35-Cursor,o:hor50-Cursor,i-ci:ver25-Cursor/lCursor,r-cr:hor20-Cursor/lCursor,sm:block-Cursor-blinkwait175-blinkoff150-blinkon175 behave mswin :set showmatch :set matchtime=2 set nu! set sw=4 set ts=4 set et set guifont=新宋体:h16:cGB2312 filetype indent on :ab Zhushi /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter><Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Shixu always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end :ab Zuhe always @(*)begin<Enter>end :ab Canshu /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter>参数定义,明德扬规范要求,verilog内的用到的数字,都使用参数表示。<Enter>参数信号全部大写<Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Module2 module module_name(<Enter>clk ,<Enter>rst_n ,<Enter>dout<Enter>);<Enter><Enter><Enter>parameter DATA_W = 8;<Enter><Enter><Enter>input clk ;<Enter>input rst_n ;<Enter><Enter><Enter>output[DATA_W-1:0] dout ;<Enter><Enter><Enter>reg [DATA_W-1:0] dout ;<Enter><Enter><Enter>reg signal1;<Enter><Enter><Enter>always@(*)begin<Enter>end<Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter><Enter>endmodule :ab Module module module_name<Enter>#(parameter MAX=20)<Enter>(<Enter>input clk,<Enter>input rst_n,<Enter>input en,<Enter>output [32-1:0] dout<Enter>);<Enter><Enter><Enter>reg signal1;<Enter><Enter><Enter>always@(*)begin<Enter>end<Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter><Enter>endmodule :ab Head /************************************************************************************<Enter>本代码由明德扬工作室精心设计和制作。<Enter><Enter>我们希望通过规范、严谨的代码,使同学们接触到纯正的集成电路/FPGA代码。<Enter><Enter>明德扬工作室长期招募成员,可免费培训,欢迎集成电路/FPGA爱好者加入。<Enter><Enter>学习交流群:97925396<Enter><Enter>*************************************************************************************/ :ab Test `timescale 1 ns/1 ns<Enter><Enter>module testbench_name();<Enter><Enter><Enter>reg clk ;<Enter>reg rst_n;<Enter><Enter><Enter>reg[3:0] din0 ;<Enter>reg din1 ;<Enter>......<Enter><Enter><Enter>wire dout0;<Enter>wire[4:0] dout1;<Enter>......<Enter><Enter><Enter>parameter CYCLE = 20;<Enter><Enter><Enter>parameter RST_TIME = 3 ;<Enter><Enter><Enter>module_name uut(<Enter>.clk (clk ), <Enter>.rst_n (rst_n ),<Enter>.din0 (din0 ),<Enter>.din1 (din1 ),<Enter>.dout0 (dout0 ),<Enter>.dout1 (dout1 )<Enter>......<Enter>);<Enter><Enter><Enter><Enter>initial begin<Enter>clk = 0;<Enter>forever<Enter>#(CYCLE/2)<Enter>clk=~clk;<Enter>end<Enter><Enter><Enter>initial begin<Enter>rst_n = 1;<Enter>#2;<Enter>rst_n = 0;<Enter>#(CYCLE*RST_TIME);<Enter>rst_n = 1;<Enter>end<Enter><Enter><Enter>initial begin<Enter>#1;<Enter><Enter>din0 = 0;<Enter>#(10*CYCLE);<Enter><Enter><Enter>end<Enter><Enter><Enter>initial begin<Enter>#1;<Enter><Enter>din1 = 0;<Enter>#(10*CYCLE);<Enter><Enter><Enter>end<Enter><Enter><Enter><Enter>endmodule :ab Ztj <Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>state_c <= IDLE;<Enter>end<Enter>else begin<Enter>state_c <= state_n;<Enter>end<Enter>end<Enter><Enter><Enter>always@(*)begin<Enter>case(state_c)<Enter>IDLE:begin<Enter>if(idl2s1_start)begin<Enter>state_n = S1;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S1:begin<Enter>if(s12s2_start)begin<Enter>state_n = S2;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S2:begin<Enter>if(s22s3_start)begin<Enter>state_n = S3;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>default:begin<Enter>state_n = IDLE;<Enter>end<Enter>endcase<Enter>end<Enter><Enter>assign idl2s1_start = state_c==IDLE && ;<Enter>assign s12s2_start = state_c==S1 && ;<Enter>assign s22s3_start = state_c==S2 && ;<Enter><Enter><Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>out1 <=1'b0 <Enter>end<Enter>else if(state_c==S1)begin<Enter>out1 <= 1'b1;<Enter>end<Enter>else begin<Enter>out1 <= 1'b0;<Enter>end<Enter>end :ab Jsq always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt <= 0;<Enter>end<Enter>else if(add_cnt)begin<Enter>if(end_cnt)<Enter>cnt <= 0;<Enter>else<Enter>cnt <= cnt + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt = ; <Enter>assign end_cnt = add_cnt && cnt== ; :ab Jsq2 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter> :ab Jsq3 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt2 <= 0;<Enter>end<Enter>else if(add_cnt2)begin<Enter>if(end_cnt2)<Enter>cnt2 <= 0;<Enter>else<Enter>cnt2 <= cnt2 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt2 = end_cnt1;<Enter>assign end_cnt2 = add_cnt2 && cnt2== ;<Enter> :ab Shixu2 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu1 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu3 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Zuhe2 always @(*)begin<Enter>if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe3 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe4 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Width_func function integer clogb2 (input integer bit_depth);<Enter>begin<Enter>for(clogb2=0;bit_depth>0;clogb2=clogb2+1)<Enter>bit_depth = bit_depth >> 1;<Enter>end<Enter>endfunction<Enter> :ab Output32 output[ 31: 0] ; :ab Output16 output[ 15: 0] ; :ab Output8 output[ 7: 0] ; :ab Output4 output[ 3: 0] ; :ab Output3 output[ 2: 0] ; :ab Output2 output[ 1: 0] ; :ab Output1 output ; :ab Input32 input [ 31: 0] ; :ab Input16 input [ 15: 0] ; :ab Input8 input [ 7: 0] ; :ab Input4 input [ 3: 0] ; :ab Input3 input [ 2: 0] ; :ab Input2 input [ 1: 0] ; :ab Input1 input ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Reg32 reg [ 31: 0] ; :ab Reg16 reg [ 15: 0] ; :ab Reg8 reg [ 7: 0] ; :ab Reg4 reg [ 3: 0] ; :ab Reg3 reg [ 2: 0] ; :ab Reg2 reg [ 1: 0] ; :ab Reg1 reg ; :ab Initial initial begin<Enter>#1;<Enter>end set diffexpr=MyDiff() function MyDiff() let opt = '-a --binary ' if &diffopt =~ 'icase' | let opt = opt . '-i ' | endif if &diffopt =~ 'iwhite' | let opt = opt . '-b ' | endif let arg1 = v:fname_in if arg1 =~ ' ' | let arg1 = '"' . arg1 . '"' | endif let arg2 = v:fname_new if arg2 =~ ' ' | let arg2 = '"' . arg2 . '"' | endif let arg3 = v:fname_out if arg3 =~ ' ' | let arg3 = '"' . arg3 . '"' | endif let eq = '' if $VIMRUNTIME =~ ' ' if &sh =~ '\<cmd' let cmd = '""' . $VIMRUNTIME . '\diff"' let eq = '"' else let cmd = substitute($VIMRUNTIME, ' ', '" ', '') . '\diff"' endif else let cmd = $VIMRUNTIME . '\diff' endif silent execute '!' . cmd . ' ' . opt . arg1 . ' ' . arg2 . ' > ' . arg3 . eq endfunction set encoding=utf-8 set fileencodings=utf-8,ucs-bom,gb18030,gbk,gb2312,cp936 "set fileencodings=utf-8,ucs-bom,gb18030,gbk,gb2312,cp936set encoding=utf-8 set fileencodings=utf-8,chinese set termencoding=utf-8 if has("win32") set fileencoding=chinese else set fileencoding=utf-8 endif "解决菜单乱码 source $VIMRUNTIME/delmenu.vim source $VIMRUNTIME/menu.vim "解决consle输出乱码 language messages zh_CN.utf-8

syntax enable set background=light colorscheme solarized set encoding=utf-8 set fileencodings=utf-8,ucs-bom,gb18030,gbk,gb2312,cp936 set hlsearch set nocompatible source $VIMRUNTIME/vimrc_example.vim source $VIMRUNTIME/mswin.vim "source $VIMRUNTIME/colors/desert.vim "source $VIMRUNTIME/colors/solarized.vim source $VIMRUNTIME/colors/corporation.vim "colors=light "background=corporation.vim behave mswin :set showmatch :set matchtime=2 set nu! set sw=4 set ts=4 set et set guifont=新宋体:h16:cGB2312 filetype indent on :ab Zhushi /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter><Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Shixu always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end :ab Zuhe always @(*)begin<Enter>end :ab Canshu /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter>参数定义,明德扬规范要求,verilog内的用到的数字,都使用参数表示。<Enter>参数信号全部大写<Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Module2 module module_name(<Enter>clk ,<Enter>rst_n ,<Enter>dout<Enter>);<Enter><Enter><Enter>parameter DATA_W = 8;<Enter><Enter><Enter>input clk ;<Enter>input rst_n ;<Enter><Enter><Enter>output[DATA_W-1:0] dout ;<Enter><Enter><Enter>reg [DATA_W-1:0] dout ;<Enter><Enter><Enter>reg signal1;<Enter><Enter><Enter>always@(*)begin<Enter>end<Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter><Enter>endmodule :ab Module module module_name<Enter>#(parameter MAX=20)<Enter>(<Enter>input clk,<Enter>input rst_n,<Enter>input en,<Enter>output [32-1:0] dout<Enter>);<Enter><Enter><Enter>reg signal1;<Enter><Enter><Enter>always@(*)begin<Enter>end<Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter><Enter>endmodule :ab Head /************************************************************************************<Enter>本代码由明德扬工作室精心设计和制作。<Enter><Enter>我们希望通过规范、严谨的代码,使同学们接触到纯正的集成电路/FPGA代码。<Enter><Enter>明德扬工作室长期招募成员,可免费培训,欢迎集成电路/FPGA爱好者加入。<Enter><Enter>学习交流群:97925396<Enter><Enter>*************************************************************************************/ :ab Test `timescale 1 ns/1 ns<Enter><Enter>module testbench_name();<Enter><Enter><Enter>reg clk ;<Enter>reg rst_n;<Enter><Enter><Enter>reg[3:0] din0 ;<Enter>reg din1 ;<Enter>......<Enter><Enter><Enter>wire dout0;<Enter>wire[4:0] dout1;<Enter>......<Enter><Enter><Enter>parameter CYCLE = 20;<Enter><Enter><Enter>parameter RST_TIME = 3 ;<Enter><Enter><Enter>module_name uut(<Enter>.clk (clk ), <Enter>.rst_n (rst_n ),<Enter>.din0 (din0 ),<Enter>.din1 (din1 ),<Enter>.dout0 (dout0 ),<Enter>.dout1 (dout1 )<Enter>......<Enter>);<Enter><Enter><Enter><Enter>initial begin<Enter>clk = 0;<Enter>forever<Enter>#(CYCLE/2)<Enter>clk=~clk;<Enter>end<Enter><Enter><Enter>initial begin<Enter>rst_n = 1;<Enter>#2;<Enter>rst_n = 0;<Enter>#(CYCLE*RST_TIME);<Enter>rst_n = 1;<Enter>end<Enter><Enter><Enter>initial begin<Enter>#1;<Enter><Enter>din0 = 0;<Enter>#(10*CYCLE);<Enter><Enter><Enter>end<Enter><Enter><Enter>initial begin<Enter>#1;<Enter><Enter>din1 = 0;<Enter>#(10*CYCLE);<Enter><Enter><Enter>end<Enter><Enter><Enter><Enter>endmodule :ab Ztj <Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>state_c <= IDLE;<Enter>end<Enter>else begin<Enter>state_c <= state_n;<Enter>end<Enter>end<Enter><Enter><Enter>always@(*)begin<Enter>case(state_c)<Enter>IDLE:begin<Enter>if(idl2s1_start)begin<Enter>state_n = S1;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S1:begin<Enter>if(s12s2_start)begin<Enter>state_n = S2;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S2:begin<Enter>if(s22s3_start)begin<Enter>state_n = S3;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>default:begin<Enter>state_n = IDLE;<Enter>end<Enter>endcase<Enter>end<Enter><Enter>assign idl2s1_start = state_c==IDLE && ;<Enter>assign s12s2_start = state_c==S1 && ;<Enter>assign s22s3_start = state_c==S2 && ;<Enter><Enter><Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>out1 <=1'b0 <Enter>end<Enter>else if(state_c==S1)begin<Enter>out1 <= 1'b1;<Enter>end<Enter>else begin<Enter>out1 <= 1'b0;<Enter>end<Enter>end :ab Jsq always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt <= 0;<Enter>end<Enter>else if(add_cnt)begin<Enter>if(end_cnt)<Enter>cnt <= 0;<Enter>else<Enter>cnt <= cnt + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt = ; <Enter>assign end_cnt = add_cnt && cnt== ; :ab Jsq2 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter> :ab Jsq3 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt2 <= 0;<Enter>end<Enter>else if(add_cnt2)begin<Enter>if(end_cnt2)<Enter>cnt2 <= 0;<Enter>else<Enter>cnt2 <= cnt2 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt2 = end_cnt1;<Enter>assign end_cnt2 = add_cnt2 && cnt2== ;<Enter> :ab Shixu2 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu1 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu3 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Zuhe2 always @(*)begin<Enter>if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe3 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe4 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Width_func function integer clogb2 (input integer bit_depth);<Enter>begin<Enter>for(clogb2=0;bit_depth>0;clogb2=clogb2+1)<Enter>bit_depth = bit_depth >> 1;<Enter>end<Enter>endfunction<Enter> :ab Output32 output[ 31: 0] ; :ab Output16 output[ 15: 0] ; :ab Output8 output[ 7: 0] ; :ab Output4 output[ 3: 0] ; :ab Output3 output[ 2: 0] ; :ab Output2 output[ 1: 0] ; :ab Output1 output ; :ab Input32 input [ 31: 0] ; :ab Input16 input [ 15: 0] ; :ab Input8 input [ 7: 0] ; :ab Input4 input [ 3: 0] ; :ab Input3 input [ 2: 0] ; :ab Input2 input [ 1: 0] ; :ab Input1 input ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Reg32 reg [ 31: 0] ; :ab Reg16 reg [ 15: 0] ; :ab Reg8 reg [ 7: 0] ; :ab Reg4 reg [ 3: 0] ; :ab Reg3 reg [ 2: 0] ; :ab Reg2 reg [ 1: 0] ; :ab Reg1 reg ; :ab Initial initial begin<Enter>#1;<Enter>end

对眼睛很好的主题

https://github.com/wsniper/vim-color-theme-protect-eyes?tab=readme-ov-file

https://www.cnblogs.com/hongfei/p/3679433.html

https://www.cnblogs.com/moluoqishi/p/10913990.html

数字IC设计入门必备——VIM自定义模板调用与VCS基本仿真操作示例

http://old.mdy-edu.com/wentijieda/20210409/1199.html

MDY

https://alidocs.dingtalk.com/i/nodes/YMyQA2dXW7rpzDqBSvDgRA128zlwrZgb?doc_type=wiki_doc&utm_medium=portal_space_create&utm_source=portal

通过网盘分享的文件:代码编辑器: GVIM

链接: https://pan.baidu.com/s/1ow1a9rMU-LnNoTKdhshnEg?pwd=k577 提取码: k577

这个没有注释板

set encoding=utf-8 set fileencodings=utf-8,ucs-bom,gb18030,gbk,gb2312,cp936 set nocompatible source $VIMRUNTIME/vimrc_example.vim source $VIMRUNTIME/mswin.vim source $VIMRUNTIME/colors/desert.vim behave mswin :set showmatch :set matchtime=2 set nu! set sw=4 set ts=4 set et set guifont=新宋体:h16:cGB2312 filetype indent on :ab Zhushi /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter><Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Shixu always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end :ab Zuhe always @(*)begin<Enter>end :ab Canshu /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter>参数定义,明德扬规范要求,verilog内的用到的数字,都使用参数表示。<Enter>参数信号全部大写<Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Module module module_name(<Enter>clk ,<Enter>rst_n ,<Enter>dout<Enter>dout<Enter>);<Enter><Enter><Enter>parameter DATA_W = 8;<Enter><Enter><Enter>input clk ;<Enter>input rst_n ;<Enter><Enter><Enter>output[DATA_W-1:0] dout ;<Enter><Enter><Enter>reg [DATA_W-1:0] dout ;<Enter><Enter><Enter>reg signal1;<Enter><Enter><Enter>always@(*)begin<Enter>end<Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter><Enter>endmodule :ab Head /************************************************************************************<Enter>本代码由明德扬工作室精心设计和制作。<Enter><Enter>我们希望通过规范、严谨的代码,使同学们接触到纯正的集成电路/FPGA代码。<Enter><Enter>明德扬工作室长期招募成员,可免费培训,欢迎集成电路/FPGA爱好者加入。<Enter><Enter>学习交流群:97925396<Enter><Enter>*************************************************************************************/ :ab Test `timescale 1 ns/1 ns<Enter><Enter>module testbench_name();<Enter><Enter><Enter>reg clk ;<Enter>reg rst_n;<Enter><Enter><Enter>reg[3:0] din0 ;<Enter>reg din1 ;<Enter>......<Enter><Enter><Enter>wire dout0;<Enter>wire[4:0] dout1;<Enter>......<Enter><Enter><Enter>parameter CYCLE = 20;<Enter><Enter><Enter>parameter RST_TIME = 3 ;<Enter><Enter><Enter>module_name uut(<Enter>.clk (clk ), <Enter>.rst_n (rst_n ),<Enter>.din0 (din0 ),<Enter>.din1 (din1 ),<Enter>.dout0 (dout0 ),<Enter>.dout1 (dout1 )<Enter>......<Enter>);<Enter><Enter><Enter><Enter>initial begin<Enter>clk = 0;<Enter>forever<Enter>#(CYCLE/2)<Enter>clk=~clk;<Enter>end<Enter><Enter><Enter>initial begin<Enter>rst_n = 1;<Enter>#2;<Enter>rst_n = 0;<Enter>#(CYCLE*RST_TIME);<Enter>rst_n = 1;<Enter>end<Enter><Enter><Enter>initial begin<Enter>#1;<Enter><Enter>din0 = 0;<Enter>#(10*CYCLE);<Enter><Enter><Enter>end<Enter><Enter><Enter>initial begin<Enter>#1;<Enter><Enter>din1 = 0;<Enter>#(10*CYCLE);<Enter><Enter><Enter>end<Enter><Enter><Enter><Enter>endmodule :ab Ztj <Enter><Enter><Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>state_c <= IDLE;<Enter>end<Enter>else begin<Enter>state_c <= state_n;<Enter>end<Enter>end<Enter><Enter><Enter>always@(*)begin<Enter>case(state_c)<Enter>IDLE:begin<Enter>if(idl2s1_start)begin<Enter>state_n = S1;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S1:begin<Enter>if(s12s2_start)begin<Enter>state_n = S2;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S2:begin<Enter>if(s22s3_start)begin<Enter>state_n = S3;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>default:begin<Enter>state_n = IDLE;<Enter>end<Enter>endcase<Enter>end<Enter><Enter>assign idl2s1_start = state_c==IDLE && ;<Enter>assign s12s2_start = state_c==S1 && ;<Enter>assign s22s3_start = state_c==S2 && ;<Enter><Enter><Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>out1 <=1'b0 <Enter>end<Enter>else if(state_c==S1)begin<Enter>out1 <= 1'b1;<Enter>end<Enter>else begin<Enter>out1 <= 1'b0;<Enter>end<Enter>end :ab Jsq always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt <= 0;<Enter>end<Enter>else if(add_cnt)begin<Enter>if(end_cnt)<Enter>cnt <= 0;<Enter>else<Enter>cnt <= cnt + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt = ; <Enter>assign end_cnt = add_cnt && cnt== ; :ab Jsq2 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter> :ab Jsq3 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt2 <= 0;<Enter>end<Enter>else if(add_cnt2)begin<Enter>if(end_cnt2)<Enter>cnt2 <= 0;<Enter>else<Enter>cnt2 <= cnt2 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt2 = end_cnt1;<Enter>assign end_cnt2 = add_cnt2 && cnt2== ;<Enter> :ab Shixu2 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu1 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu3 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Zuhe2 always @(*)begin<Enter>if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe3 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe4 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Output32 output[ 31: 0] ; :ab Output16 output[ 15: 0] ; :ab Output8 output[ 7: 0] ; :ab Output4 output[ 3: 0] ; :ab Output3 output[ 2: 0] ; :ab Output2 output[ 1: 0] ; :ab Output1 output ; :ab Input32 input [ 31: 0] ; :ab Input16 input [ 15: 0] ; :ab Input8 input [ 7: 0] ; :ab Input4 input [ 3: 0] ; :ab Input3 input [ 2: 0] ; :ab Input2 input [ 1: 0] ; :ab Input1 input ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Reg32 reg [ 31: 0] ; :ab Reg16 reg [ 15: 0] ; :ab Reg8 reg [ 7: 0] ; :ab Reg4 reg [ 3: 0] ; :ab Reg3 reg [ 2: 0] ; :ab Reg2 reg [ 1: 0] ; :ab Reg1 reg ; :ab Initial initial begin<Enter>#1;<Enter>end set diffexpr=MyDiff() function MyDiff() let opt = '-a --binary ' if &diffopt =~ 'icase' | let opt = opt . '-i ' | endif if &diffopt =~ 'iwhite' | let opt = opt . '-b ' | endif let arg1 = v:fname_in if arg1 =~ ' ' | let arg1 = '"' . arg1 . '"' | endif let arg2 = v:fname_new if arg2 =~ ' ' | let arg2 = '"' . arg2 . '"' | endif let arg3 = v:fname_out if arg3 =~ ' ' | let arg3 = '"' . arg3 . '"' | endif let eq = '' if $VIMRUNTIME =~ ' ' if &sh =~ '\<cmd' let cmd = '""' . $VIMRUNTIME . '\diff"' let eq = '"' else let cmd = substitute($VIMRUNTIME, ' ', '" ', '') . '\diff"' endif else let cmd = $VIMRUNTIME . '\diff' endif silent execute '!' . cmd . ' ' . opt . arg1 . ' ' . arg2 . ' > ' . arg3 . eq endfunction set encoding=utf-8 set fileencodings=utf-8,ucs-bom,gb18030,gbk,gb2312,cp936 "set fileencodings=utf-8,ucs-bom,gb18030,gbk,gb2312,cp936set encoding=utf-8 set fileencodings=utf-8,chinese set termencoding=utf-8 if has("win32") set fileencoding=chinese else set fileencoding=utf-8 endif "解决菜单乱码 source $VIMRUNTIME/delmenu.vim source $VIMRUNTIME/menu.vim "解决consle输出乱码 language messages zh_CN.utf-8

set nocompatible source $VIMRUNTIME/vimrc_example.vim source $VIMRUNTIME/mswin.vim source $VIMRUNTIME/colors/desert.vim behave mswin :set showmatch :set matchtime=2 set nu! set sw=4 set ts=4 set et set guifont=新宋体:h16:cGB2312 filetype indent on :ab Zhushi /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter><Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Shixu always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end :ab Zuhe always @(*)begin<Enter>end :ab Canshu /*********www.mdy-edu.com 明德扬科教 注释开始****************<Enter>参数定义,明德扬规范要求,verilog内的用到的数字,都使用参数表示。<Enter>参数信号全部大写<Enter>**********www.mdy-edu.com 明德扬科教 注释结束****************/ :ab Module module module_name(<Enter>clk ,<Enter>rst_n ,<Enter>//其他信号,举例dout<Enter>dout<Enter>);<Enter><Enter>//参数定义<Enter>parameter DATA_W = 8;<Enter><Enter>//输入信号定义<Enter>input clk ;<Enter>input rst_n ;<Enter><Enter>//输出信号定义<Enter>output[DATA_W-1:0] dout ;<Enter><Enter>//输出信号reg定义<Enter>reg [DATA_W-1:0] dout ;<Enter><Enter>//中间信号定义<Enter>reg signal1;<Enter><Enter>//组合逻辑写法<Enter>always@(*)begin<Enter>end<Enter><Enter>//时序逻辑写法<Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter><Enter>endmodule :ab Head /************************************************************************************<Enter>本代码由明德扬工作室精心设计和制作。<Enter><Enter>我们希望通过规范、严谨的代码,使同学们接触到纯正的集成电路/FPGA代码。<Enter><Enter>明德扬工作室长期招募成员,可免费培训,欢迎集成电路/FPGA爱好者加入。<Enter><Enter>学习交流群:97925396<Enter><Enter>*************************************************************************************/ :ab Test `timescale 1 ns/1 ns<Enter><Enter>module testbench_name();<Enter><Enter>//时钟和复位<Enter>reg clk ;<Enter>reg rst_n;<Enter><Enter>//uut的输入信号<Enter>reg[3:0] din0 ;<Enter>reg din1 ;<Enter>......<Enter><Enter>//uut的输出信号<Enter>wire dout0;<Enter>wire[4:0] dout1;<Enter>......<Enter><Enter>//时钟周期,单位为ns,可在此修改时钟周期。<Enter>parameter CYCLE = 20;<Enter><Enter>//复位时间,此时表示复位3个时钟周期的时间。<Enter>parameter RST_TIME = 3 ;<Enter><Enter>//待测试的模块例化<Enter>module_name uut(<Enter>.clk (clk ), <Enter>.rst_n (rst_n ),<Enter>.din0 (din0 ),<Enter>.din1 (din1 ),<Enter>.dout0 (dout0 ),<Enter>.dout1 (dout1 )<Enter>......<Enter>);<Enter><Enter><Enter>//生成本地时钟50M<Enter>initial begin<Enter>clk = 0;<Enter>forever<Enter>#(CYCLE/2)<Enter>clk=~clk;<Enter>end<Enter><Enter>//产生复位信号<Enter>initial begin<Enter>rst_n = 1;<Enter>#2;<Enter>rst_n = 0;<Enter>#(CYCLE*RST_TIME);<Enter>rst_n = 1;<Enter>end<Enter><Enter>//输入信号din0赋值方式<Enter>initial begin<Enter>#1;<Enter>//赋初值<Enter>din0 = 0;<Enter>#(10*CYCLE);<Enter>//开始赋值<Enter><Enter>end<Enter><Enter>//输入信号din1赋值方式<Enter>initial begin<Enter>#1;<Enter>//赋初值<Enter>din1 = 0;<Enter>#(10*CYCLE);<Enter>//开始赋值<Enter><Enter>end<Enter><Enter><Enter><Enter>endmodule :ab Ztj //四段式状态机<Enter><Enter>//第一段:同步时序always模块,格式化描述次态寄存器迁移到现态寄存器(不需更改)<Enter>always@(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>state_c <= IDLE;<Enter>end<Enter>else begin<Enter>state_c <= state_n;<Enter>end<Enter>end<Enter><Enter>//第二段:组合逻辑always模块,描述状态转移条件判断<Enter>always@(*)begin<Enter>case(state_c)<Enter>IDLE:begin<Enter>if(idl2s1_start)begin<Enter>state_n = S1;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S1:begin<Enter>if(s12s2_start)begin<Enter>state_n = S2;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>S2:begin<Enter>if(s22s3_start)begin<Enter>state_n = S3;<Enter>end<Enter>else begin<Enter>state_n = state_c;<Enter>end<Enter>end<Enter>default:begin<Enter>state_n = IDLE;<Enter>end<Enter>endcase<Enter>end<Enter>//第三段:设计转移条件<Enter>assign idl2s1_start = state_c==IDLE && ;<Enter>assign s12s2_start = state_c==S1 && ;<Enter>assign s22s3_start = state_c==S2 && ;<Enter><Enter>//第四段:同步时序always模块,格式化描述寄存器输出(可有多个输出)<Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>out1 <=1'b0 //初始化<Enter>end<Enter>else if(state_c==S1)begin<Enter>out1 <= 1'b1;<Enter>end<Enter>else begin<Enter>out1 <= 1'b0;<Enter>end<Enter>end :ab Jsq always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt <= 0;<Enter>end<Enter>else if(add_cnt)begin<Enter>if(end_cnt)<Enter>cnt <= 0;<Enter>else<Enter>cnt <= cnt + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt = ; <Enter>assign end_cnt = add_cnt && cnt== ; :ab Jsq2 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter> :ab Jsq3 always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt0 <= 0;<Enter>end<Enter>else if(add_cnt0)begin<Enter>if(end_cnt0)<Enter>cnt0 <= 0;<Enter>else<Enter>cnt0 <= cnt0 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt0 = ;<Enter>assign end_cnt0 = add_cnt0 && cnt0== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin <Enter>if(!rst_n)begin<Enter>cnt1 <= 0;<Enter>end<Enter>else if(add_cnt1)begin<Enter>if(end_cnt1)<Enter>cnt1 <= 0;<Enter>else<Enter>cnt1 <= cnt1 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt1 = end_cnt0;<Enter>assign end_cnt1 = add_cnt1 && cnt1== ;<Enter><Enter>always @(posedge clk or negedge rst_n)begin<Enter>if(!rst_n)begin<Enter>cnt2 <= 0;<Enter>end<Enter>else if(add_cnt2)begin<Enter>if(end_cnt2)<Enter>cnt2 <= 0;<Enter>else<Enter>cnt2 <= cnt2 + 1;<Enter>end<Enter>end<Enter><Enter>assign add_cnt2 = end_cnt1;<Enter>assign end_cnt2 = add_cnt2 && cnt2== ;<Enter> :ab Shixu2 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu1 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Shixu3 always @(posedge clk or negedge rst_n)begin<Enter>if(rst_n==1'b0)begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>end<Enter> :ab Zuhe2 always @(*)begin<Enter>if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe3 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Zuhe4 always @(*)begin<Enter>if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else if()begin<Enter>end<Enter>else begin<Enter>end<Enter>end<Enter> :ab Output32 output[ 31: 0] ; :ab Output16 output[ 15: 0] ; :ab Output8 output[ 7: 0] ; :ab Output4 output[ 3: 0] ; :ab Output3 output[ 2: 0] ; :ab Output2 output[ 1: 0] ; :ab Output1 output ; :ab Input32 input [ 31: 0] ; :ab Input16 input [ 15: 0] ; :ab Input8 input [ 7: 0] ; :ab Input4 input [ 3: 0] ; :ab Input3 input [ 2: 0] ; :ab Input2 input [ 1: 0] ; :ab Input1 input ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Wire32 wire [ 31: 0] ; :ab Wire16 wire [ 15: 0] ; :ab Wire8 wire [ 7: 0] ; :ab Wire4 wire [ 3: 0] ; :ab Wire3 wire [ 2: 0] ; :ab Wire2 wire [ 1: 0] ; :ab Wire1 wire ; :ab Reg32 reg [ 31: 0] ; :ab Reg16 reg [ 15: 0] ; :ab Reg8 reg [ 7: 0] ; :ab Reg4 reg [ 3: 0] ; :ab Reg3 reg [ 2: 0] ; :ab Reg2 reg [ 1: 0] ; :ab Reg1 reg ; :ab Initial initial begin<Enter>#1;<Enter>end set diffexpr=MyDiff() function MyDiff() let opt = '-a --binary ' if &diffopt =~ 'icase' | let opt = opt . '-i ' | endif if &diffopt =~ 'iwhite' | let opt = opt . '-b ' | endif let arg1 = v:fname_in if arg1 =~ ' ' | let arg1 = '"' . arg1 . '"' | endif let arg2 = v:fname_new if arg2 =~ ' ' | let arg2 = '"' . arg2 . '"' | endif let arg3 = v:fname_out if arg3 =~ ' ' | let arg3 = '"' . arg3 . '"' | endif let eq = '' if $VIMRUNTIME =~ ' ' if &sh =~ '\<cmd' let cmd = '""' . $VIMRUNTIME . '\diff"' let eq = '"' else let cmd = substitute($VIMRUNTIME, ' ', '" ', '') . '\diff"' endif else let cmd = $VIMRUNTIME . '\diff' endif silent execute '!' . cmd . ' ' . opt . arg1 . ' ' . arg2 . ' > ' . arg3 . eq endfunction set encoding=utf-8 set fileencodings=utf-8,chinese set termencoding=utf-8 if has("win32") set fileencoding=chinese else set fileencoding=utf-8 endif "解决菜单乱码 source $VIMRUNTIME/delmenu.vim source $VIMRUNTIME/menu.vim "解决consle输出乱码 language messages zh_CN.utf-8

verilog的代码片段在GVIM/VIM中的使用——":ab" 配置使用(定制自己的coding)_vimrc :ab-CSDN博客

gvim使用:ab命令快速制作verilog模板 - 灰信网(软件开发博客聚合)

:ab Module module module_name(<enter>clk ,<enter>rst_n ,<enter>in ,<enter>out <enter>);<enter><enter> parameter DATA_W = 8;<enter><enter>input clk ;<enter>input rst_n ;<enter><enter>output [DATA_W-1:0] out ;<enter><enter>reg [DATA_W-1:0] out ; <enter><enter>reg signal1 ;<enter><enter>always@( * ) begin<enter>end<enter><enter>always @(posedge clk or negedge rst_n) begin <enter>if(~rst_n) begin <enter>end<enter>else begin<enter>end<enter>end<enter><enter>endmodule :ab Zuhe always @(*) begin<Enter>if( )begin<Enter>end<Enter>else begin<Enter>end<Enter>end :ab Shixu always @( posedge clk or negedge rst_n) begin<enter>if( ~rst_n ) begin<enter>end<enter>else begin<enter>end<enter>end :ab Jsq always @( posedge clk or negedge rst_n ) begin<enter>if ( ~rst_n ) begin<enter>cnt <= 0;<enter>end<enter>else if ( &cnt ) begin<enter>cnt <= 0;<enter>end<enter>else begin<enter>cnt <= cnt + 1;<enter>end<enter>end :ab Ztj reg [2:0] cs;<enter>reg [2:0] ns;<enter>parameter [2:0] IDLE = 3'b000,<enter>S1 = 3'b001,<enter>S2 = 3'b010,<enter>ERROR = 3'b100;<enter>always @( posedge clk or negedge rst_n ) begin<enter>if ( !rst_n ) begin<enter>cs <= IDLE;<enter>end<enter>else begin<enter>cs <= ns;<enter>end<enter>end<enter><enter>always @( * ) begin<enter>ns = IDLE;<enter>case ( cs )<enter>IDLE : begin<enter>if ( ) begin<enter>ns = IDLE;<enter>end<enter>end<enter>S1 : begin<enter>if ( ) begin<enter>ns = S1;<enter>end <enter>end <enter>S2 : begin <enter> if ( ) begin<enter>ns = S2; <enter>end <enter>end <enter>ERROR : begin <enter> if ( ) begin<enter>ns = ERROR; <enter>end<enter>end <enter>endcase <enter>end<enter><enter>always @( posedge clk or negedge nrst ) begin <enter>if ( !nrst ) begin <enter>end<enter>else begin <enter>case ( ns )<enter>endcase <enter>end <enter>end :ab TB `timescale 1ns/100ps<enter><enter>module dff_tb();<enter><enter> reg t_clk;<enter>reg t_rst_n;<enter>reg [3:0] t_d;<enter>wire [3:0] t_q;<enter><enter>syn_dff dut1 (.clk(t_clk),.rst_n(t_rst_n)); <enter><enter>initial begin<enter>t_clk = 0;<enter>end<enter>always #20 t_clk = ~t_clk;<enter><enter>initial begin<enter>t_rst_n = 1;<enter>@( posedge t_clk );<enter>t_rst_n = 0;<enter>@( posedge t_clk );<enter>t_rst_n = 1;<enter>end<enter><enter>initial begin<enter>t_d = 1;<enter>#25 t_d = 0;<enter>#20 $finish;<enter>end<enter>endmodule

自己制作模板方法:

:ab name code

Tips:

我的gvim自动缩进2空格,tab也为2空格,如果将代码复制进去格式不太好看的话可能是这个引起的,将以下代码复制到_vimrc文件中即可:

"设置缩进

"设置Tab长度为2空格

set tabstop=2

"设置自动缩进长度为2空格

set shiftwidth=2

使用模板可以减少不必要的重复,大量缩短时间,希望我的分享对你有帮助,转载请说明出处~

GVIM与模板——让FPGA开发变得更简单 - 没落骑士 - 博客园

20_01利用GVIM制作模板_转_哔哩哔哩_bilibili

设置行号

:set number

在normal模式下按下/即可进入查找模式,输入要查找的字符串并按下回车。

Vim会跳转到第一个匹配。按下n查找下一个,按下N查找上一个。

补全命令:Ctrl+p

gg 跳转到第一行

G跳转到最后一行

:100 跳到100行

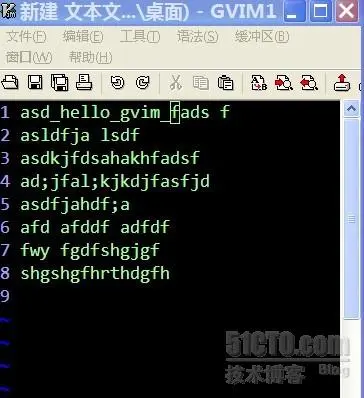

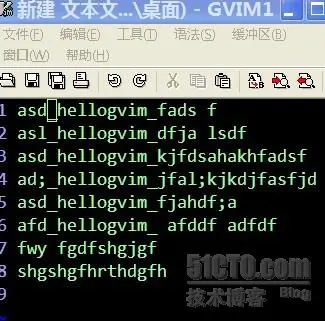

windows下gvim列编辑_51CTO博客_vim 列编辑

下面就是列编辑操作步骤啦

1,按esc退出编辑模式,光标变成一块而不是一条竖线了

2,把光标放在要列编辑的开始的地方

3,按ctrl+q

4,输入4j(就是你要列编辑的行数啦,比如5j,8j,10j,30j之类的)。光标变成一列竖的了,这就是列编辑的初始状态,大家很熟悉的吧

5,按shift+i,也就是大写的I了。光标会又回到列编辑最开始的地方(步骤2那里)

6,在所在光标那儿输入你想插入的字符。这时你只能看见第一行改变了

7,再按esc退出列编辑模式,就可以看见选定的行都相应的变了

posted on 2025-07-22 14:04 taylorrrrrrrrrr 阅读(38) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号