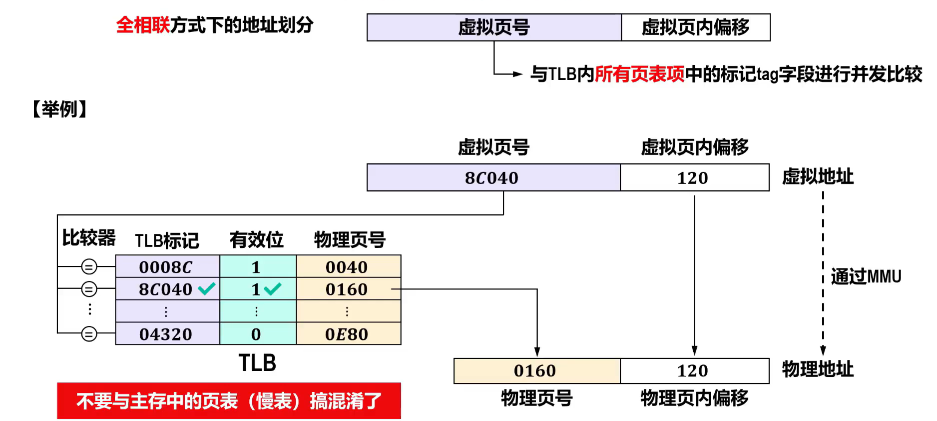

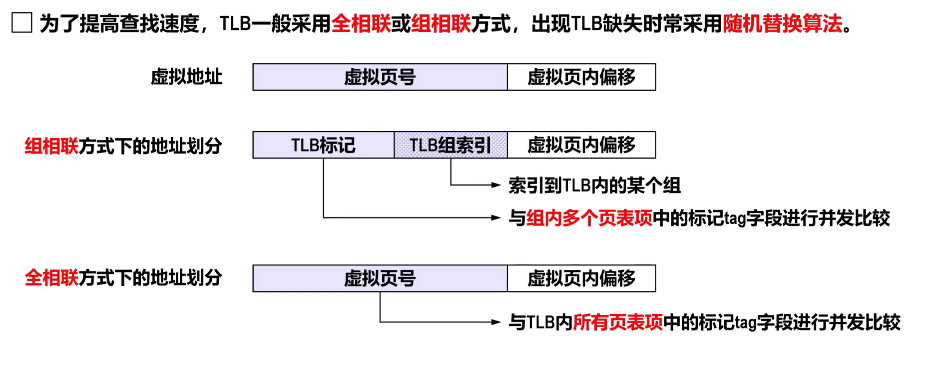

页式虚拟存储器——使用快表TLB进行加速地址转换

1.通过TLB的索引索引到相应的组。

2.将虚拟地址的TLB标记分别与该组中页表项的两个tag字段进行并发比较,并得到比较结果。

3.将比较结果分别与各自相应页表项的有效位的值进行逻辑与。

4.两个与运算的结果作为多路选择器的选择输出控制端。

5.多路选择器的两个数据输入端,分别来自该组中两个页表项的物理页号字段。

6.在TLB命中的情况下,多路选择器的输出就来自该组被命中的那个页表项中的物理页号。

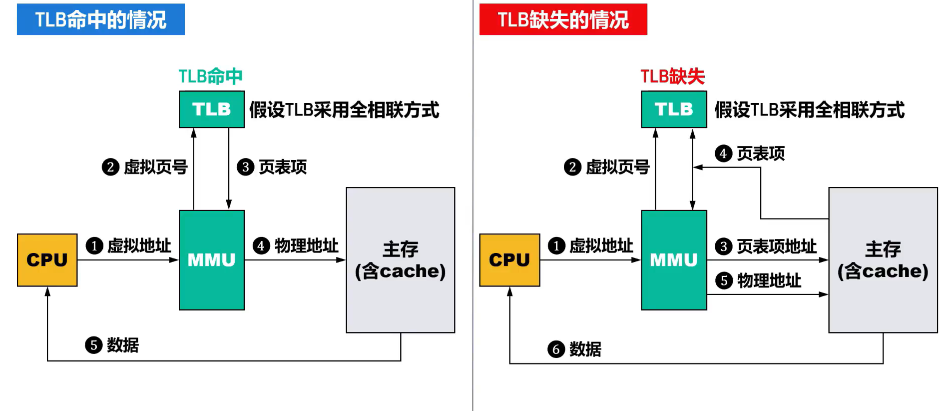

TLB命中的情况

1.CPU给出一个虚拟地址。

2.MMU通过虚拟页号在TLB中进行全相联并发比较,假设TLB命中,也就是在TLB中找到了相应的有效的页表项,这表明该页表项所对应的虚拟页,已经从辅存调入了cache/主存系统

3.TLB给MMU返回页表项。

4.MMU用页表项中存放位置字段存放的物理页号,与虚拟地址中的页内偏移部分构造出物理地址,通过物理地址访问cache/主存中的相应数据。

5.Cache主存系统给CPU返回数据。

TLB缺失的情况

1、2步与上述相同

3.MMU利用页表基址寄存器,和该虚拟地址中的虚拟页号部分生成页表项地址,通过页表项地址访问cache主存中的相应页表项。

4.cache主存系统给MMU返回页表项,若页表项中有效位的取值为1,则需更新TLB,MMU用页表项中存放位置字段存放的物理页号与虚拟地址中的页内偏移部分构造出物理地址。

5.通过物理地址访问cache主存系统中的相应数据

6.cache主存系统给CPU返回数据。

posted on 2025-04-14 12:20 swj2529411658 阅读(177) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号