ZYNQ xapp585 lvds 文档阅读 (二)

文档地址:

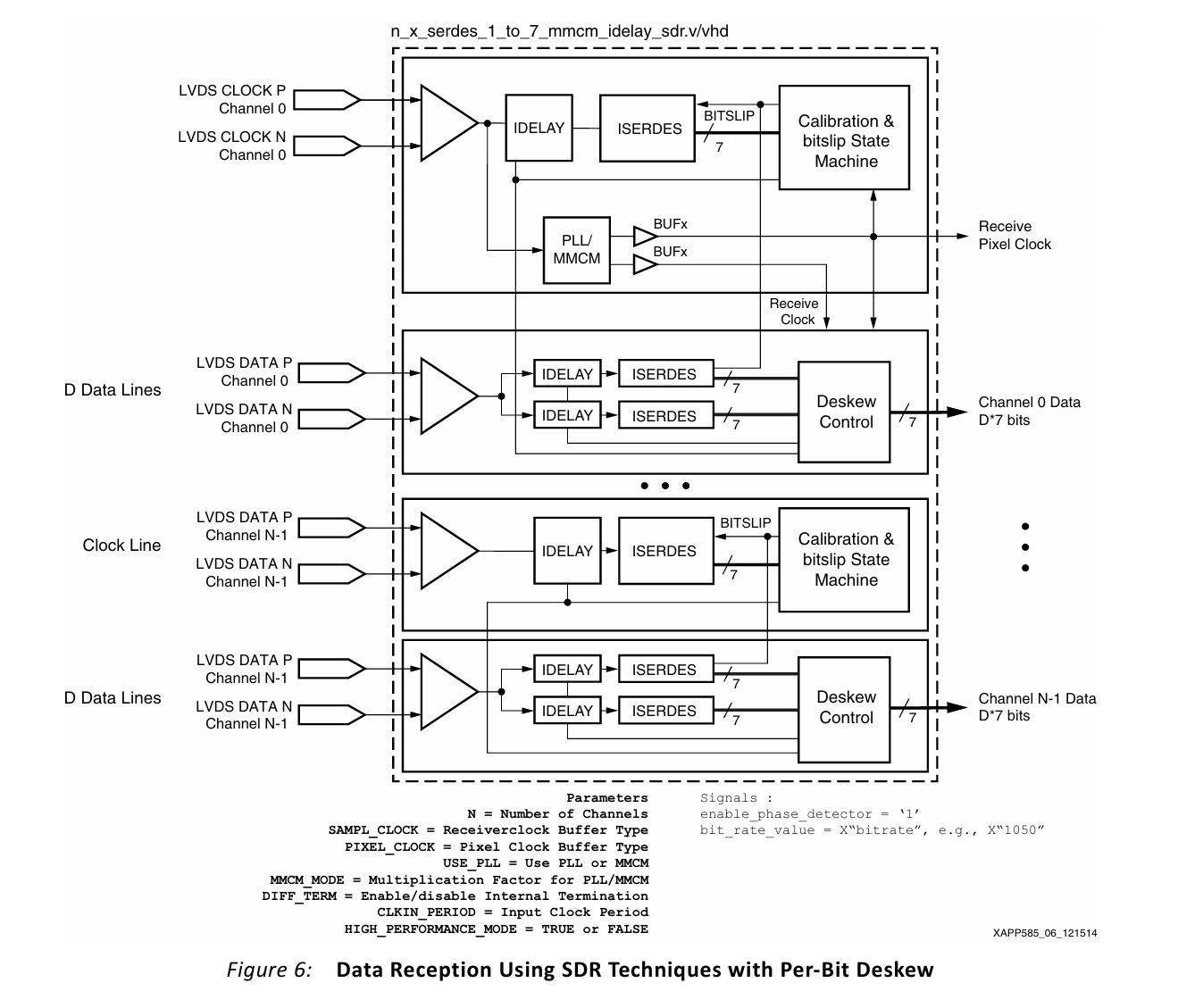

带每比特去歪斜的 SDR 数据接收

带每比特去歪斜的 SDR 数据接收与标准 SDR 情况类似:先确定正确的时钟延迟,再将该延迟值传递给数据线上的 IODELAYE2 元件。

如图 6 所示,输入数据线还会被路由至第二个 IODELAYE2 元件和第二个 ISERDES 原语。由于输入标准为 LVDS(低压差分信号),需要两个输入引脚,因此这第二个延迟元件和 ISERDES 原语相当于 “免费” 使用(无需额外占用资源)。

主数据延迟元件的初始延迟设置与之前相同,标称处于数据眼图中心;从数据延迟元件的设置则与主延迟相差半个比特周期(或提前,或滞后)。因此,对输入数据线会进行两次采样,两次采样的间隔为半个比特周期。

后续用于确定正确采样延迟的算法如下:

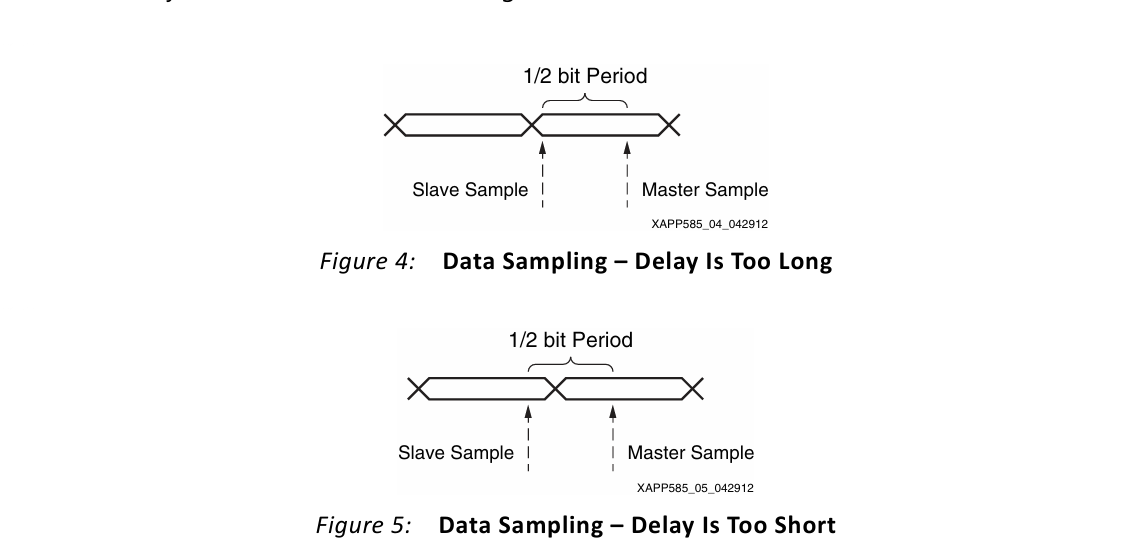

若在(数据)跳变之后,间隔半个比特周期采集的两个样本值相同,则说明采样点过晚,输入延迟需减少 1 个抽头(见图 4);若在(数据)跳变之后,这两个采集样本值不同,则说明采样点过早,输入延迟需增加 1 个抽头(见图 5)。

该调整机制的运行需要输入数据发生变化:如果数据线始终保持静态 0 或静态 1(无跳变),则延迟会一直维持在 “通过输入时钟校准得到的初始值”,直到数据线出现跳变后,才会启动延迟调整。

由于无法实时同步于采样时钟进行这种比较,因此会使用并行 7 位数据,即每条输入线需要两个 7 位样本。

该算法可能存在两种极端情况:一种是延迟向零值回绕,另一种是延迟远离零值回绕。无论哪种情况,都会发生数据损坏 —— 要么某一位被接收两次,要么完全丢失。通用互连逻辑中包含寄存器和多路复用器,可检测这两种情况,并适当插入流水线级,确保数据损坏不会发生。

这种方法的缺点是需要一定量的通用互连逻辑来实现;优点则是每条输入线都能实时单独进行去歪斜处理,同时保证数据接收正确。这使得诸如 PCB 布线、引脚延迟和发射器引脚差异等歪斜源可以从时序分析中排除。

去歪斜算法可处理任何方向的任意比特偏差,但由于视频接口的特性(并行字需要与输入像素时钟模式同步),建议每个通道的输入线和时钟线歪斜保持在 ±1/4 单位间隔(UI)范围内。超出此范围时电路仍能工作,但可能需要额外的用户逻辑来执行字去歪斜。这种情况下的接收器框图如图 6 所示。

补充说明

- 并行 7 位数据的作用:由于无法在高速串行采样时钟下实时完成两个样本的比较,转为对并行 7 位数据进行处理,降低了实时比较的时序压力,是算法实现的关键适配。

- 延迟回绕(delay wrap around):指 IODELAYE2 的延迟值达到最大 / 最小值后,继续调整会从另一端重新开始(如最大延迟值后加 1 抽头会回到最小值),这种情况下可能导致采样点跳变,引发数据错误。

- 字去歪斜(word deskew):与 “每比特去歪斜” 不同,字去歪斜针对的是 “整个并行字(如 7 位)” 的时序对齐,当通道内歪斜超出 ±1/4 UI 时,单个比特的校准已无法保证字边界正确,需通过额外逻辑调整整个字的时序。

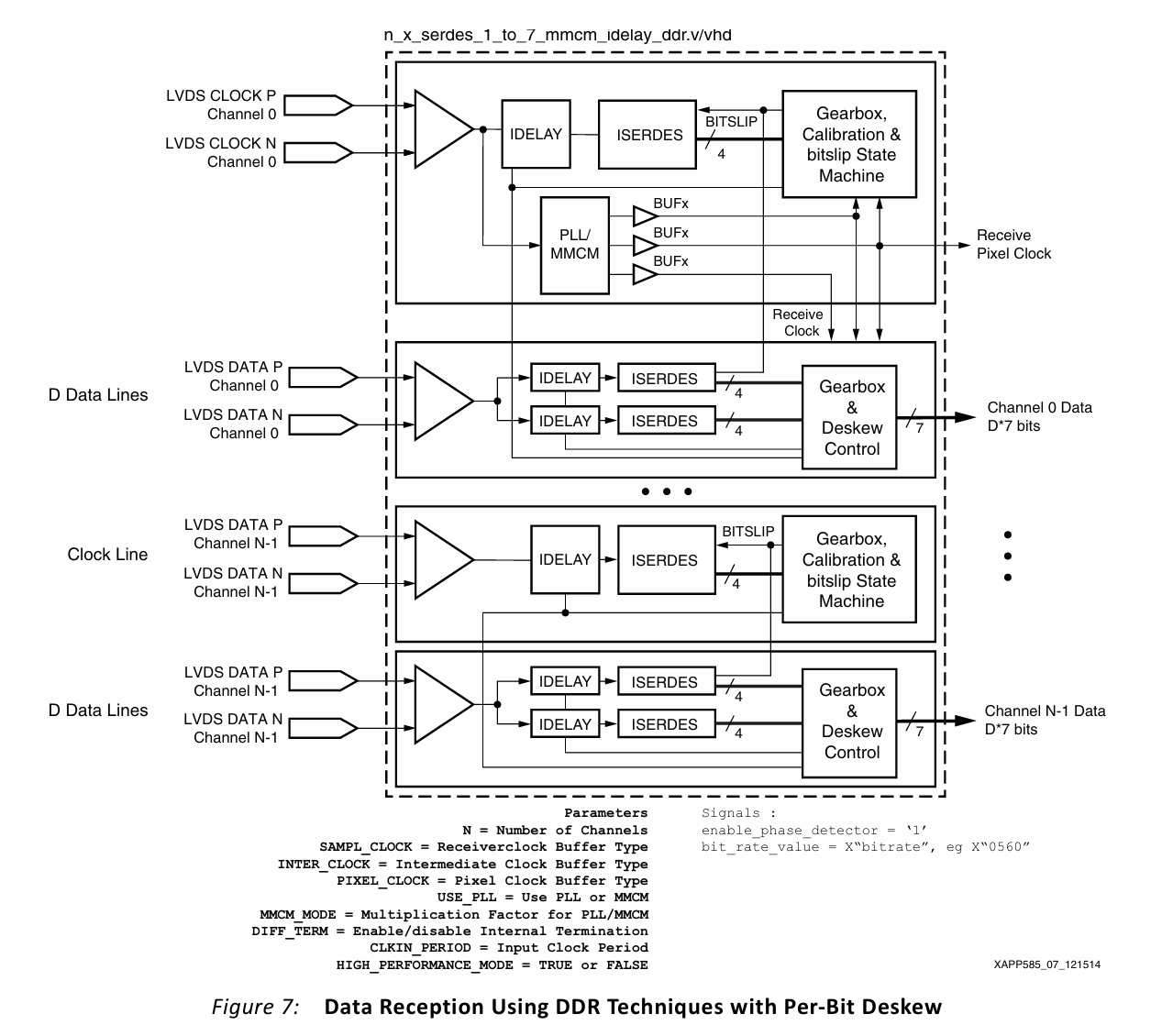

带每比特去歪斜的 DDR 数据接收

本文涉及的最后一种数据接收情况是带每比特去歪斜的 DDR 技术。

数据接收方式与标准 DDR 情况相同,即采用 1:4 的 ISERDES 配置,并配合中间时钟和齿轮箱,但此时也会使用从 ISERDES(slave ISERDES)。该从 ISERDES 也配置为 1:4 模式,且现在有两个 IODELAYE2 元件,其设置值相差半个比特周期,每个 ISERDES 各对应一个。

去歪斜机制的工作方式与之前相同,不同之处在于样本数据是直接取自主 ISERDES(master ISERDES)和从 ISERDES 的 4 位数据。最终输出再通过一个 4 位到 7 位的齿轮箱转移到像素时钟域,如图 7 所示。

最低数据速率考量

数据捕获机制依赖于 IODELAYE2 模块。该模块包含 31 个延迟抽头(tap),每个抽头的标称延迟为 78 皮秒(ps),因此最低捕获速率计算如下:78 ps × 31 = 2418 ps(对应 415 Mb/s)。任何低于该值的比特率都可能导致完全无法检测到(数据)边沿。

若未检测到边沿,时钟校准电路会将延迟值(IDELAY)设为 “最大抽头数的一半”,随后停止校准。将延迟值设为该数值后,采样时钟两侧至少会有 1170 ps 的裕量(margin)。

因此,当数据接收速率低于 415 Mb/s(对应像素时钟频率为 59.28 MHz,由 415 Mb/s ÷ 7 计算得出)时,每比特去歪斜功能(若已启用)会自动禁用。若在延迟线中检测到边沿,则最终延迟值会静态设置为该检测值 ±10h(十六进制)个抽头;若未检测到边沿,则延迟线会被设置为 10h(十六进制)个抽头。无论哪种情况,延迟值的设置都会确保其与数据眼图(eye)边沿至少相距 10h(十六进制)个抽头,这在较低比特率下是可接受的。

显然,该速率下限不适用于发送端逻辑 —— 因为发送端无需进行(延迟)校准。

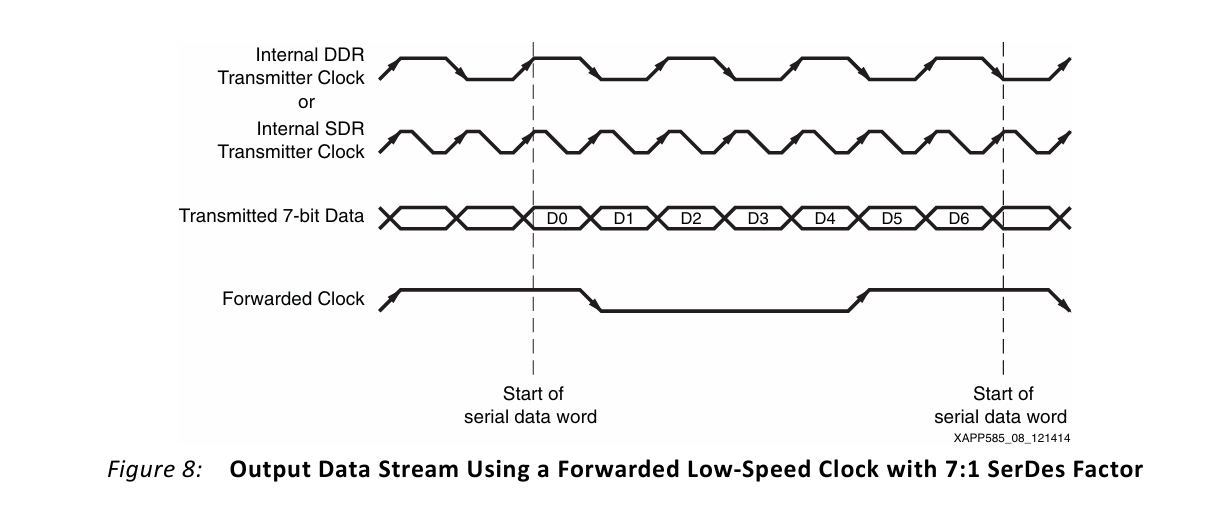

所需的输出转发时钟(forwarded clock,即随数据发送给接收端的时钟) 与数据流会同时改变状态,因此可由同一个发送时钟(transmit clock) 生成。此类应用的一个示例是相机、平板电视及显示器中使用的 7:1 接口,如图 8 所示。

7 系列 FPGA 中的数据传输

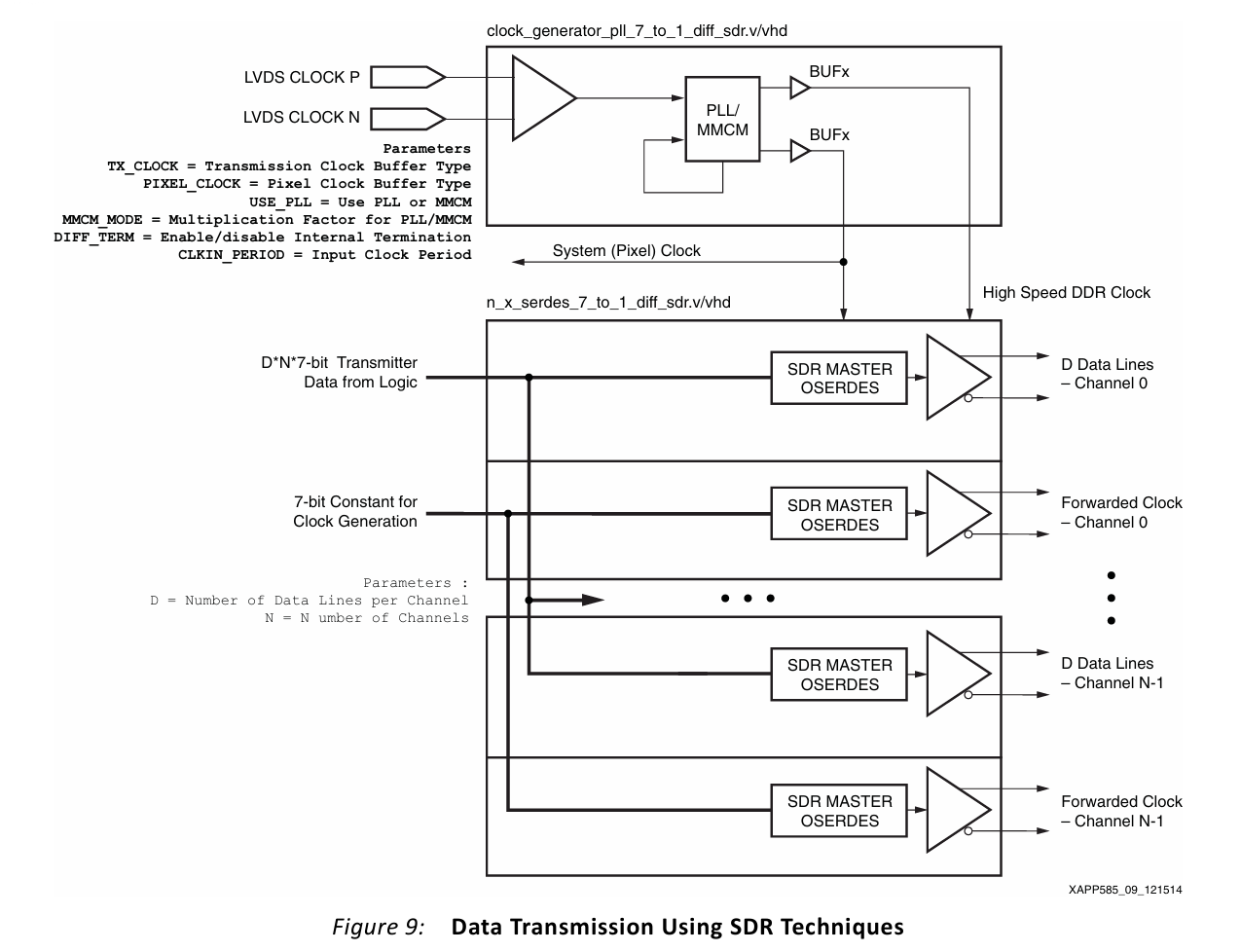

该机制的拓扑结构非常简洁。发送端源时钟在 PLL(锁相环)中按需倍频,以生成内部 SDR(单数据速率)或 DDR(双数据速率)的发送时钟。

在 SDR 应用场景示例中,内部像素时钟会乘以 7 的某个倍数,确保生成的 VCO(压控振荡器)频率处于第 3 页表 1 所述的限制范围内。在 DDR 场景中,内部像素时钟会乘以 3.5。

PLL 或 MMCM 会输出两个时钟,分别用作高速时钟和低速时钟。这两个时钟保持相位对齐,以确保所有 OSERDES(输出串并转换原语)通过其 SR(置位 / 复位)输入端口的同步复位实现同步后,能正确完成串行化操作。随后,输入的并行数据会在高速传输时钟的驱动下被串行化输出。

转发时钟输出的生成方式类似:通过向与时钟线关联的 OSERDES 发送恒定值来实现。在视频 7:1 应用中,转发时钟需采用 1100001 或 1100011 模式,以确保转发时钟与数据的关系符合通用标准。

采用 SDR 发送时钟时的必要电路及输出波形如图 9 所示。OSERDES 配置为 7:1 模式,7 位数据(或时钟用的恒定数据)会与 OSERDES 的 CLKDIV(分频时钟)引脚保持同步输入,如图 10 所示。

在单个 FPGA 同时执行 7:1 标准的数据接收和发送时,PLL(锁相环)或 MMCM(混合模式时钟管理器)通常会在发送端与接收端之间共享。此时,相同的 PLL 和时钟网络可同时用于数据接收和发送。

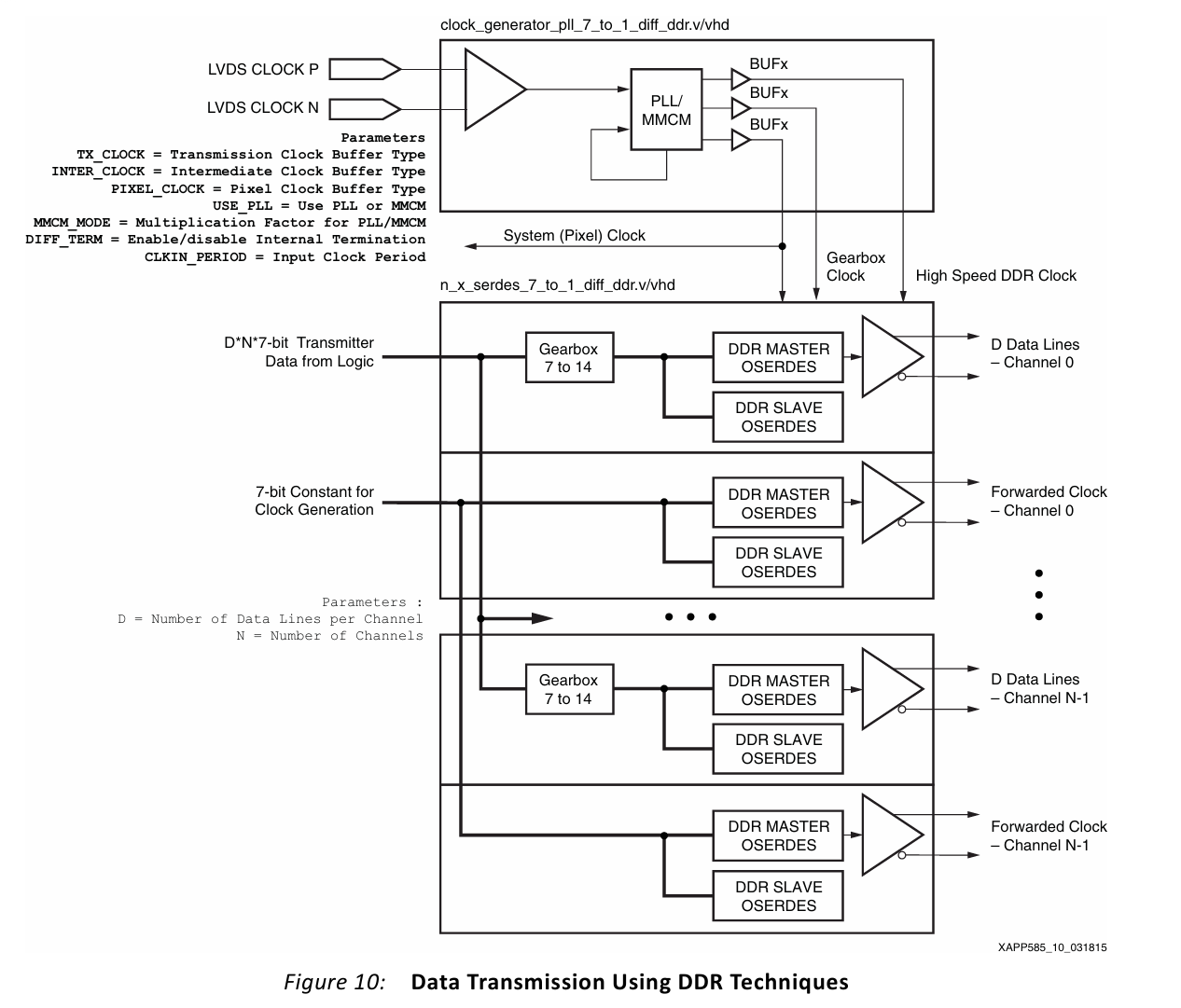

DDR 模式考量

DDR 机制的拓扑结构比 SDR 模式稍复杂。OSERDES(输出串并转换原语)在 DDR 模式下无法直接实现 7:1 串行化,但级联时可配置为 14:1 的 DDR 模式。

发送端源时钟在 PLL(锁相环)/MMCM(混合模式时钟管理器)中进行 3.5 倍频,生成内部 DDR 发送时钟和与输入频率相同的像素时钟。此外,还需要第三个时钟 —— 其频率为像素时钟的一半,用于 OSERDES 的 CLKDIV(分频时钟)输入,且该时钟频率为高速传输时钟的 1/14。数据需以 14 位为单位,与这个较慢的第三个时钟同步地送入 OSERDES。

像素时钟速率的内部数据通过图 10 所示的简单齿轮箱(数据位宽转换模块)转移到这个较慢的第三个时钟域。如图 10 所示,齿轮箱的输入为 7 位宽、像素时钟速率的数据,输出为 14 位宽、像素时钟一半速率的数据,可直接连接至 OSERDES。

接收器时序考量

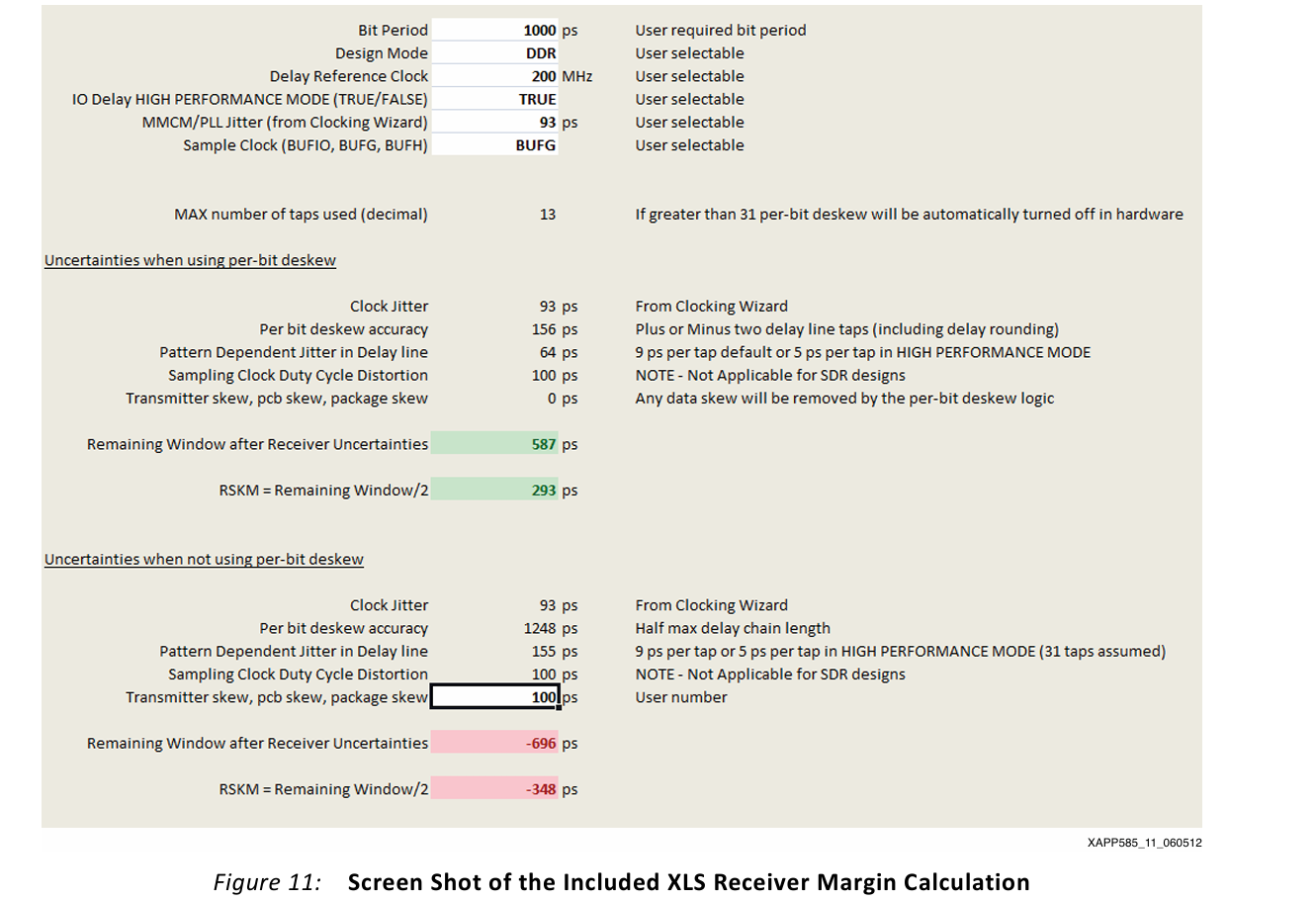

接收器设计需要考虑多个不确定性来源。这些来源的影响应从比特周期中扣除,以分析设计是否满足设计者的要求。

为方便分析,设计 ZIP 文件中包含一个 Excel 表格,可用于快速评估。图 11 展示了该表格的截图。

用户在表格的白色单元格中输入其特定设计的参数后,计算得出的剩余接收器裕量和接收器歪斜裕量(RSKM)会以绿色或红色显示,分别表示裕量为正或为负。

不确定性来源包括:

-

PLL/MMCM 抖动:该数值可通过时钟向导(clocking wizard)获取。

-

每比特去歪斜精度:使用每比特去歪斜时,该数值为 ±2 个延迟抽头(含所有舍入误差);不使用每比特去歪斜时,该数值为 IODELAYE2 元件延迟范围的一半。

-

无论哪种情况,该数值均包含主从 IODELAYE2 元件之间的时钟歪斜,以及这两个元件在建立时间和保持时间上的差异。IODELAYE2 元件需要 200 MHz 或 300 MHz 的参考时钟才能正常工作。

-

有关 IODELAYE2 及其关联的 IDELAYCTRL 控制块的更多信息,可参考《7 系列 FPGA SelectIO 资源用户指南》(UG471)[参考文献 4]。

-

将参考时钟频率提高到 300 MHz 可改善接收器裕量,但会导致每比特去歪斜的最低工作比特率升至 641 Mb/s。

-

延迟线中的模式相关抖动:通常为每抽头 9 ps,但使用 IODELAYE2 元件的高性能模式(HIGH_PERFORMANCE mode)时,可降至每抽头 5 ps。所使用的抽头数量会在表格中计算得出。

-

采样时钟占空比失真:这仅在使用 DDR 技术时才有意义,且随接收器采样时钟所选用的缓冲器类型而变化。

-

发射器歪斜、PCB 歪斜、封装歪斜:在使用每比特去歪斜的设计中,这些歪斜都会被抵消;但在不使用每比特去歪斜时,需将其纳入考量。

浙公网安备 33010602011771号

浙公网安备 33010602011771号