ZYNQ xapp585 lvds 文档阅读 (一)

文档地址:

摘要

Xilinx 7 系列 FPGA 包含 ISERDES(输入串并转换原语)和 OSERDES(输出串并转换原语),这两种原语使得串并转换电路的设计非常简便。

在采用每比特去歪斜(per-bit deskew)的情况下,每路信号的运行速率可达到 415 Mb/s 至 1200 Mb/s(具体速率取决于所使用的器件系列和速度等级);

而在较低运行速率下,则采用静态数据对齐(static data alignment)方式。

本应用笔记介绍了如何将 ISERDES 和 OSERDES 与混合模式时钟管理器(MMCM)或锁相环(PLL)高效结合,以低压差分信号(LVDS)实现 7:1 数据的接收与传输。

在采用每比特去歪斜时,每路信号的传输速率为 415 Mb/s 至 1200 Mb/s(具体速率取决于所使用的器件系列和速度等级)。

可从 Xilinx 官网下载本应用笔记对应的参考设计文件。有关设计文件的详细信息,请参阅《参考设计》章节。

接收器概述

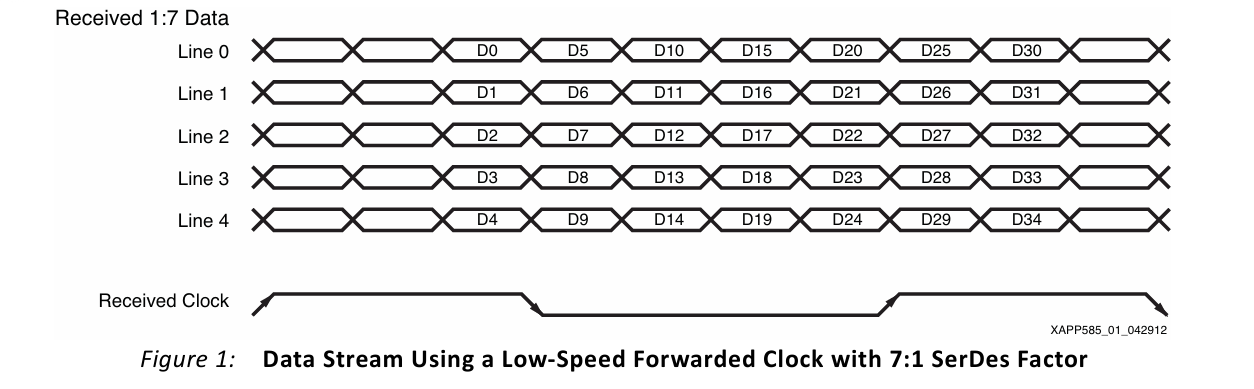

图 1 所示的此类 1:7 接口(图中展示了 5 线接口)需进行时钟倍频,在电视、蓝光播放器等消费类设备中,当数据在器件间传输时,该接口广泛用于视频处理。

一个视频通道通常包含 5 路 LVDS 数据线和 1 路 LVDS 时钟线。现代电视可采用多个通道(通常为 4 个或 8 个),以确保足够的视频带宽。

本应用笔记针对单通道和多通道设计提供了参考设计方案:在这些设计中,所有通道的像素时钟频率相同,且只需一个时钟倍频元件(MMCM 或 PLL)即可满足所有通道需求,从而减少 FPGA 资源的占用,并大幅简化设计人员对引脚分配的选择。

该设计中的宏支持对单个或多个通道进行参数化配置:一个变量用于设置待生成的通道数量,另一个变量则确定每个通道的 LVDS 数据线数量。

通道既可以全部位于 7 系列 FPGA 的同一个 I/O 组(I/O bank)中,也可以分布在不同的 I/O 组。建议将同一通道的所有线路置于同一 I/O 组,但只要时钟元件选择得当,不同通道也可位于不同 I/O 组。

为所有通道生成内部时钟的输入时钟,即为通道 0 的时钟输入,因此该信号对(指 LVDS 时钟信号对)应放置在具备时钟功能的 I/O 引脚上。其他通道的时钟仅用于成帧目的,因此若有需要,可将其放置在普通 LVDS 输入引脚上。

ISERDES 与 OSERDES 使用指南

输入数据可选择通过 7 系列 FPGA 中集成的输入延迟原语(IODELAYE2),按引脚逐个进行实时去歪斜处理。这种方式能让设计人员放宽印刷电路板(PCB)布线的歪斜要求,同时还能获得更严格的时序裕量。

ISERDES 与 OSERDES 使用指南

7 系列 FPGA 中的每个I/O 逻辑单元(I/O logic tile) 都包含一个 8 位 ISERDES(输入串并转换原语)和一个 8 位 OSERDES(输出串并转换原语)。

两个相邻单元(主单元与从单元)的 ISERDES 或 OSERDES 可通过级联(cascade) 构成一个 10 位或 14 位的模块。

基于此,在单数据速率(SDR)模式下,ISERDES 的输入比率(串并转换比)支持 1:2 至 1:8(含首尾值)、1:10 和 1:14;

在双数据速率(DDR)模式下,其输入比率支持 1:2、1:4、1:6、1:8、1:10 和 1:14。

而 OSERDES 在 SDR 模式下的输出比率(并串转换比)支持 2:1 至 8:1(含首尾值)、10:1 和 14:1;

在 DDR I/O 时钟模式下,其输出比率同样支持 2:1、1:4、1:6、1:8、1:10 和 14:1。

当采用差分信号标准时,级联 ISERDES 或 OSERDES 模块不存在额外问题 —— 因为这类标准会用到与 ISERDES、OSERDES 寄存器相关联的两个 I/O 逻辑单元(主单元与从单元),因此使用两个 ISERDES 或 OSERDES 实际上相当于 “无额外成本”(无需额外占用更多 FPGA 资源)。在平板显示器和相机的 7:1(串并 / 并串转换)应用中,差分信号通常是默认采用的标准。

当所需比特率低于所选器件及速度等级中时钟网络支持的最高时钟频率时,应采用 SDR 技术;超过该速度阈值则可使用 DDR 技术,此时能达到的最高比特率受限于 PLL(锁相环)或 MMCM(混合模式时钟管理器)的最高输出频率。SDR 技术的优势在于:所需的通用互连逻辑大幅减少,且时钟中的任何占空比失真(duty cycle distortion) 都不会对其产生影响。

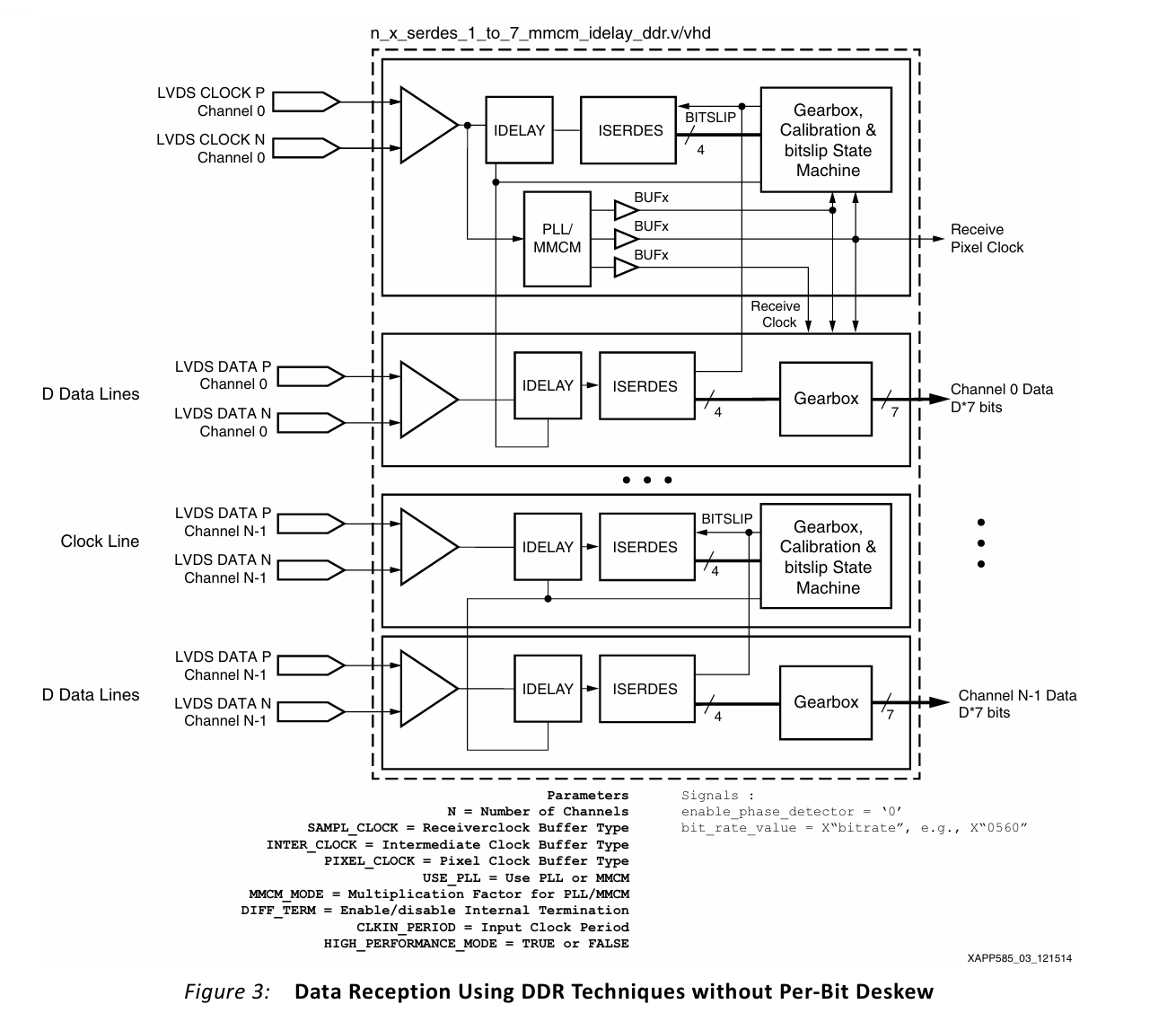

由于 ISERDES 和 OSERDES 本身不原生支持 7:1 DDR 模式,必须通过分布式 RAM 齿轮箱(distributed RAM gearbox,即数据位宽转换模块) 才能实现该功能。该齿轮箱的工作原理如下:以 “采样时钟频率的 1/4” 从 ISERDES 接收 4 位宽的数据,再以 “采样时钟频率除以 7”(即原始接收的像素时钟频率)输出 7 位宽的数据。

时钟设计指南

混合模式时钟管理器(MMCM)可驱动 BUFIO(I/O 时钟缓冲器)、BUFR(区域时钟缓冲器)、BUFH(高扇出时钟缓冲器)和 BUFG(全局时钟缓冲器)这几种时钟网络;

而锁相环(PLL)仅可驱动 BUFH(高扇出时钟缓冲器)和 BUFG(全局时钟缓冲器)这两种时钟网络。

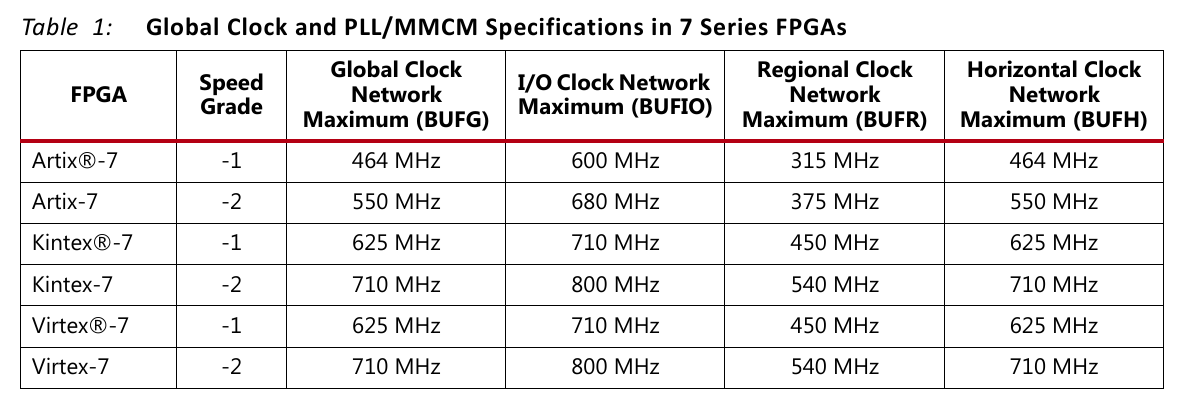

7 系列 FPGA 各速度等级下,可用时钟网络的最高频率如表 1 所示。为确保信息的完整性,这些规格参数应参考最新版本的数据手册进行确认,包括《Artix-7 FPGA 数据手册:直流与交流开关特性》(DS181,参考文献 1)、《Kintex-7 FPGA 数据手册:直流与交流开关特性》(DS182,参考文献 2)以及《Virtex-7 FPGA 数据手册:直流与交流开关特性》(DS183,参考文献 3)。

但此类应用通常用于对成本敏感的产品中,因此需采用当前可用的最低速度等级。目前测试仅局限于每路 1200 Mb/s 的速率。

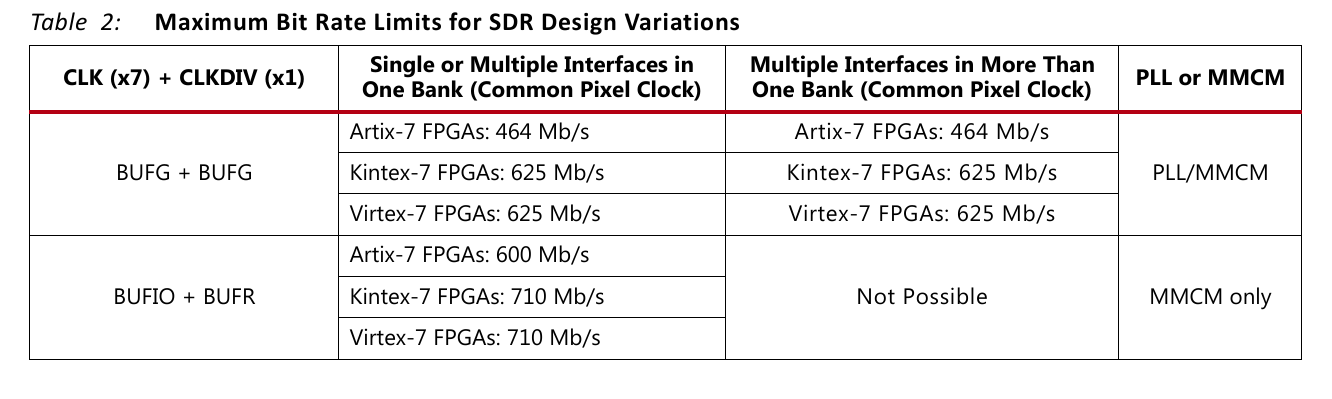

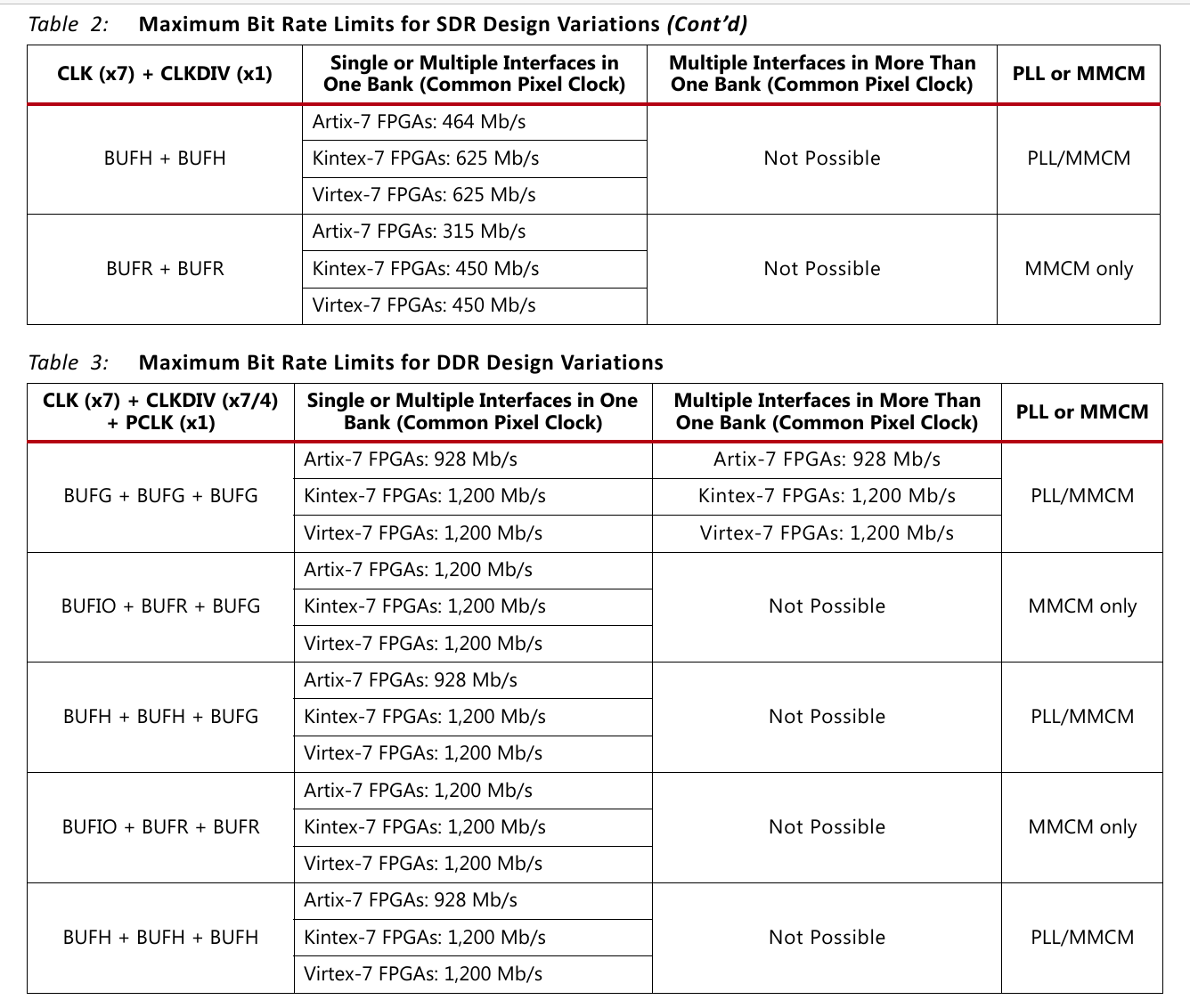

前文所述的各类设计方案,其最高工作频率相关信息汇总于表 2 和表 3 中。需注意,表 2 和表 3 中仅列出了最低速度等级(-1 级)的数据。

其他速度等级的最高频率可从对应的 7 系列 FPGA 数据手册中查询。从时钟缓冲器需求来看:SDR 时钟方案需使用 2 个时钟缓冲器,DDR 时钟方案需使用 3 个时钟缓冲器。未列出的任何时钟缓冲器组合,要么是芯片硬件(silicon)不支持,要么属于不推荐的解决方案。

1:7 解串与数据接收介绍

数据流的速率是输入时钟的 7 倍,且该时钟信号本身还用作接收数据的成帧信号(framing signal)。在一个时钟周期内,数据线的状态会发生 7 次变化。一个广泛应用的例子是相机、平板电视和显示器中使用的 7:1 接口。

在此应用场景中,接收的时钟会在 PLL(锁相环)或 MMCM(混合模式时钟管理器)中进行 7 倍频,生成的高速时钟会通过全局缓冲器(BUFG)、I/O 缓冲器(BUFIO) 或水平时钟缓冲器(BUFH) 传输至 ISERDES(输入串并转换原语)逻辑。这些时钟缓冲器可工作在 SDR(单数据速率)或 DDR(双数据速率)模式下。

输入数据会通过一个IODELAYE2 元件输送至 ISERDES,该 IODELAYE2 元件已通过状态机训练,使其相对于采样时钟的延迟尽可能接近1/2 单位间隔(1/2 UI,Unit Interval)。这一过程通过将输入时钟作为训练基准来实现。

由输入像素时钟得到的成帧数据,还会与 ISERDES 的位滑动功能(Bitslip) 配合使用,以生成与原始传输数据具有正确字对齐关系的并行数据(如图 1 所示)。最终,这些解串后的并行数据会以原始输入时钟的速率传输至通用互连逻辑。

此处需重点关注两项设计要点,具体如下:

1. 基于 SDR 采样时钟的设计

当采用 SDR(单数据速率)采样时钟时,ISERDES 可直接工作在 1:7 模式下。ISERDES 仅支持以下三种时钟元件组合:

- 两个 BUFG(全局时钟缓冲器)

- 两个 BUFH(高扇出时钟缓冲器)

- 一个 BUFIO(I/O 时钟缓冲器)+ 一个 BUFR(区域时钟缓冲器)

不同时钟缓冲器的应用差异如下:

- 使用 BUFG 的优势:并行数据可通过覆盖整个 FPGA 器件的时钟进行传输,适用于全芯片范围内的数据同步需求。

- 使用 BUFR 或 BUFH 的特点:并行数据仅能通过覆盖当前 “时钟区域(clock region)” 的时钟传输,适合局部区域内的数据处理场景。

若需接收多个 “像素时钟速率相同” 的通道,有两种布局与时钟方案可选:

- 将所有通道置于同一 I/O 组(I/O bank),此时上述所有时钟方案均适用;

- 将通道分布在不同 I/O 组,此时仅支持 BUFG 时钟方案。

2. 基于 DDR 采样时钟的设计

当采用 DDR(双数据速率)采样时钟时,ISERDES 需工作在 1:4 模式下,且需通过基于分布式 RAM 的齿轮箱(数据位宽转换模块) 模拟完整的 1:7 模式。该设计需涉及三个独立的时钟域(clock domains),具体如下:

- 采样时钟(原始高速时钟);

- 采样时钟除以 4(用于接收 ISERDES 输出的 4 位宽数据);

- 采样时钟除以 7(与原始输入像素时钟频率相等,用于输出 7 位宽数据)。

上述时钟对应的元件信息如表 3 所示。与 SDR 设计类似,若需接收多个 “像素时钟速率相同” 的通道:

- 通道置于同一 I/O 组时,所有时钟方案均适用;

- 通道分布在不同 I/O 组时,所有时钟均需采用 BUFG 时钟网络。

3. PLL 与 MMCM 的时钟方案差异

无论采用 SDR 还是 DDR 模式,若使用 PLL(锁相环)而非 MMCM(混合模式时钟管理器)进行时钟倍频,则仅支持 BUFH 或 BUFG 时钟方案—— 因为这两种缓冲器是 PLL 唯一可访问的缓冲器类型(PLL 无法驱动 BUFIO 和 BUFR)。

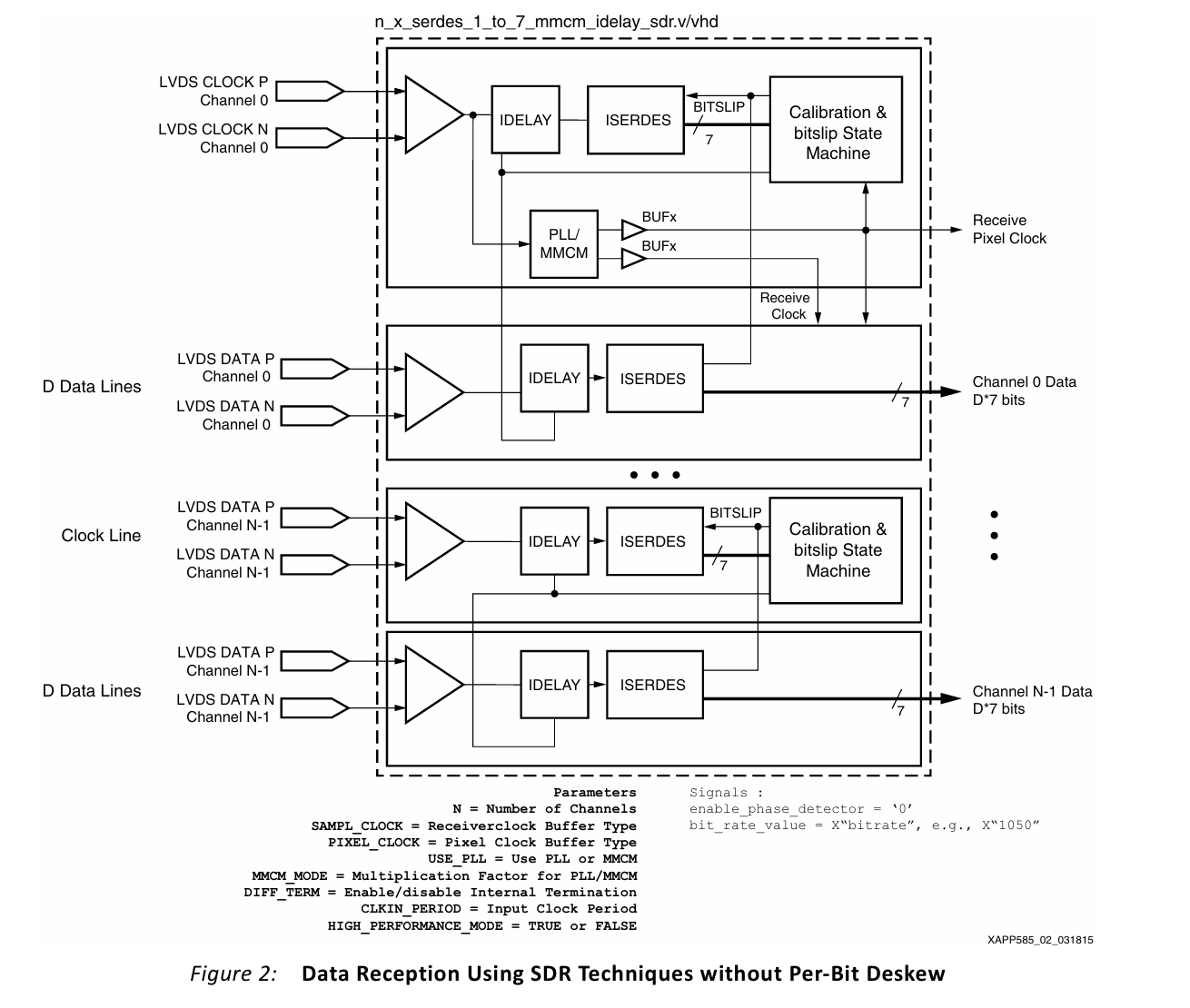

基础数据接收

该机制的拓扑结构非常简洁。接收时钟在 PLL(锁相环)或 MMCM(混合模式时钟管理器)中按需倍频,以生成内部 SDR(单数据速率)或 DDR(双数据速率)接收时钟。

在 7:1 视频应用场景示例中,对于 SDR 设计,接收的像素时钟需进行 7 倍频;对于 DDR 设计,则需进行 3.5 倍频。可根据所采用的模式和拓扑结构,为数据接收选择不同的时钟网络。

无论是 SDR 还是 DDR 设计,若采用单通道或多通道设计且所有输入引脚位于同一 I/O 组(I/O bank),则首选方案是使用 BUFIO(I/O 时钟缓冲器)和 BUFR(区域时钟缓冲器)作为串并转换模块(SerDes,此处特指 ISERDES)的时钟源。这些时钟也可替换为两个 BUFH(高扇出时钟缓冲器)时钟网络或两个 BUFG(全局时钟缓冲器)时钟网络。

若输入引脚跨越多于一个 I/O 组,则目前推荐的唯一方案是使用两个 BUFG 时钟网络。此外,DDR 数据接收还需额外一个中间时钟,该时钟可选用 BUFH 或 BUFG 时钟网络,具体选择由所需接收时钟的扇出能力决定。

时钟延迟的初始值设置为与当前比特率对应的抽头数,该比特率由宏模块的 16 位输入决定。例如,输入 0560 对应 560 Mb/s。

宏模块内部会生成一个 01h 至 1Fh 的 5 位值,与编程的比特率相对应。这个 5 位值等于与当前单位间隔(UI)时间相当的抽头数。以输入 0560 为例,其输出为 17h—— 因为 17h(十进制 23)乘以 78 皮秒的标称抽头延迟值,结果为 1794 皮秒,对应 557 Mb/s。从定义上来说,这个 5 位值并非精确值,但任何舍入误差都会在时序分析中得到考量。

当接收端的 PLL 或 MMCM 指示其已锁定后,状态机会从初始值开始缓慢减小时钟延迟,直到检测到接收的 7 位时钟数据发生变化。这一变化对应着检测到时钟边沿,此时会根据当前位置将时钟延迟的当前值增加或减少半个 UI,使延迟标称值处于数据眼图的中心(相对于经 PLL 或 MMCM 倍频后的时钟而言)。该值也会传输至相关数据线的延迟输入端,确保数据线同样在其中点位置被采样。

一种可能的事件序列如下:

-

将时钟延迟设置为 17h。

-

递减时钟延迟,直到在时钟数据输入上检测到变化,假设在延迟值为 05h 时检测到该变化。

-

向延迟线添加或减去半个比特周期的延迟。17h 的一半四舍五入为 0Bh。05h 减去 0Bh 的结果为负数,这是不合适的。因此,采用 05h 加 0Bh 等于 10h 作为时钟延迟线的最终值。

-

10h 这个值也用于相关通道的数据输入延迟线,通常每个通道有 4 或 5 个数据输入。数据输入的数量可通过宏上的参数进行编程设置。

最后,会对时钟线的输入数据进行已知模式检测(通常检测 1100001 或 1100011 这两种模式),以确保接收的并行数据与接收时钟保持正确的对应关系(见图 1)。若接收的模式不正确,则会发出位滑动命令(Bitslip command),实际将所有输入时钟和数据位移动一个位置(详见《7 系列 FPGA SelectIO 资源用户指南》(UG471)[参考文献 4])。位滑动命令最多重复执行七次,直至检测到正确模式,此时接收的并行数据即实现正确成帧。

此后不再进行时序调整。随着 V 和 T(电压和温度)的变化,PLL(锁相环)或 MMCM(混合模式时钟管理器)会将时钟维持在当前位置,确保数据接收正确。该方法假设:通道中的时钟线和数据线在印刷电路板(PCB)上已实现良好对齐。完整的时序分析详见《接收器时序考量》章节。

该宏模块(macro) 还可支持更多通道,通道数量可通过宏模块的参数进行编程设置。这些额外通道的输入时钟不用于频率倍频,仅使用通道 0 的倍频时钟作为接收时钟。不过,例如通道 1 的输入时钟会用作通道 1 状态机的输入,其对齐流程仍按上述方式进行。同样,使用该方法需满足以下假设:通道内的时钟线和数据线已实现良好对齐,但不要求各个通道之间相互对齐,仅需所有通道工作在相同频率下。

无去歪斜(deskew)功能的 DDR 设计中,ISERDES 原语(ISERDES primitives)会配置为 1:4 模式;

随后,数据会直接通过基于分布式 RAM 的齿轮箱(数据位宽转换模块) 完成传输 —— 从 “时钟频率除以 4” 下的 4 位宽数据,转换为 “像素时钟频率” 下的 7 位宽数据。每路数据线接收的 7 位数据,可与所选的时钟网络(BUFR、BUFH 或 BUFG)保持同步。

DDR 接收器的结构示意图如图 3 所示。

除了需额外增加齿轮箱,以及从 PLL(锁相环)或 MMCM(混合模式时钟管理器)多引出一个时钟外,DDR 模式的工作流程与前文《无每比特去歪斜的 SDR 数据接收》中所述的 SDR 模式完全一致。

同样,该设计也支持使用多个接收通道,但需遵循以下假设:通道内的数据线和时钟线已实现良好对齐,但不要求通道之间实现对齐。

浙公网安备 33010602011771号

浙公网安备 33010602011771号