硬件工程师经典面试题(3): 6层PCB叠层方案,哪一种更适合高速高频PCB设计?

Hello,大家好,先来汇报一下《电感应用分析精粹》的撰写进度。目前正在第一轮细化阶段,第1章(总5章)已经完成,约2万字,满意度200%。“细化”阶段位于“架构编排”阶段之后,后者是对整体框架的部署,而前者则是进一步对内容细节进行疏通(包括绘图)。可以这么说,稿件经过细化后,与最终出版的图书有八成相似了,敬请期待哈~~

好的,咱来看下一个面(笔)试题。根据布线层优化考虑,对于某6层板,最优叠层设计应该是哪个()

A:S01-G02-S03-S04-P05-S06

B:S01-S02-G03-P04-S05-S06

C:S01-G02-S03-P04-G05-S06

D:S01-G02-S03-G04-P05-S06

(注:S-信号层;G-地平面层;P-电源平面层)

这个题目也不错,四层板叠层太少,六层板刚刚好,只要叠层配置思路明白了,八层板及以上都是相似的。

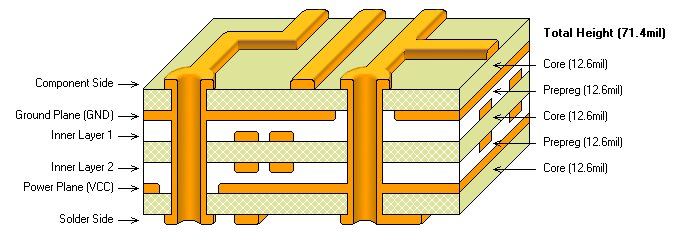

首先,我们了解一下PCB叠层配置的一般原则,简单介绍如下:

1、应该为每一个信号层配置相邻的平面层,以便提供连续的阻抗。

2、地平面层与电源平面层尽量相邻配置,以降低电源内阻

3、信号层尽量不要相邻配置,以避免发生串扰现象。

4、考虑层叠结构的对称性。

当然,有些是相互影响的。例如,”为信号层配置平面层”也可以避免信号串扰。受限于篇幅及题目所限,本文只能简单介绍一些经验,其实背后涉及大量高速PCB设计相关的内容,包括阻抗、噪声、反射、串扰、电源内阻、返回路径、传输线等等,详情可以参考已出版图书《PADS PCB设计指南》,其中对叠层理论相关的重要内容进行了详细阐述,如下图所示:

好的,接下来我们按上述原则分析试题的4个选项

A:(S01-G02-S03-S04-P05-S06):此方案有4个布线层与2个参考平面,布线空间比较多,但是电源与地平面之间存在两个信号层,所以电源内阻相对比较高。由于第3层靠近地平面且在内层,所以关键的高速信号线应优先安排在此层。当然,S03与S04应该尽量垂直交叉布线,以最大限制避免相邻布线层的串扰。

B:(S01-S02-G03-P04-S05-S06):此方案也有4个布线层与2个参考平面,由于电源平面与地平面相邻,因此能够提供较低的电源阻抗。最外面两层是较差的布线层。靠近地平面的S02是最好的布线层,可用于布置关键信号线。另外,S01与S02、S05与S06应该尽量垂直交叉布线。然而,交叉布线同样会使阻抗不连续(继而引发串扰与反射等问题),所以此方案并不适合高频高速应用场合。

C:(S01-G02-S03-P04-G05-S06)。此方案有3个布线层和3个参考平面 ,每一层信号线都有相邻的平面层,相应的阻抗都能够被较好控制,而且电源与接平面相邻,电源内阻也比较低。另外,两个相对靠外的地平面层也有一定的电磁屏蔽效果。S03是最优先布线层,其次是底层。当然,缺点也是有的,布线空间更少了,而且叠层也不是对称的。

D:(S01-G02-S03-G04-P05-S06):此方案与C选项相差之处在:第4层与第5层的地与平面层顺序。一般而言,地平面放在较外层能够起到更好的电磁屏蔽效果。

综上所述,对信号要求较高的高速高频PCB而言,选项“C”应该是最佳的。

需要注意的是,产品设计是性能与成本折中的过程,所以PCB叠层并没有绝对的好坏之分,关键在于项目的需求。例如,你的产品要求不高(EMC,ESD全部不管),也没有任何高速高频信号,就是布线密度非常大,那么,选项A或B也是不错的选择,因为布线空间更多。

浙公网安备 33010602011771号

浙公网安备 33010602011771号