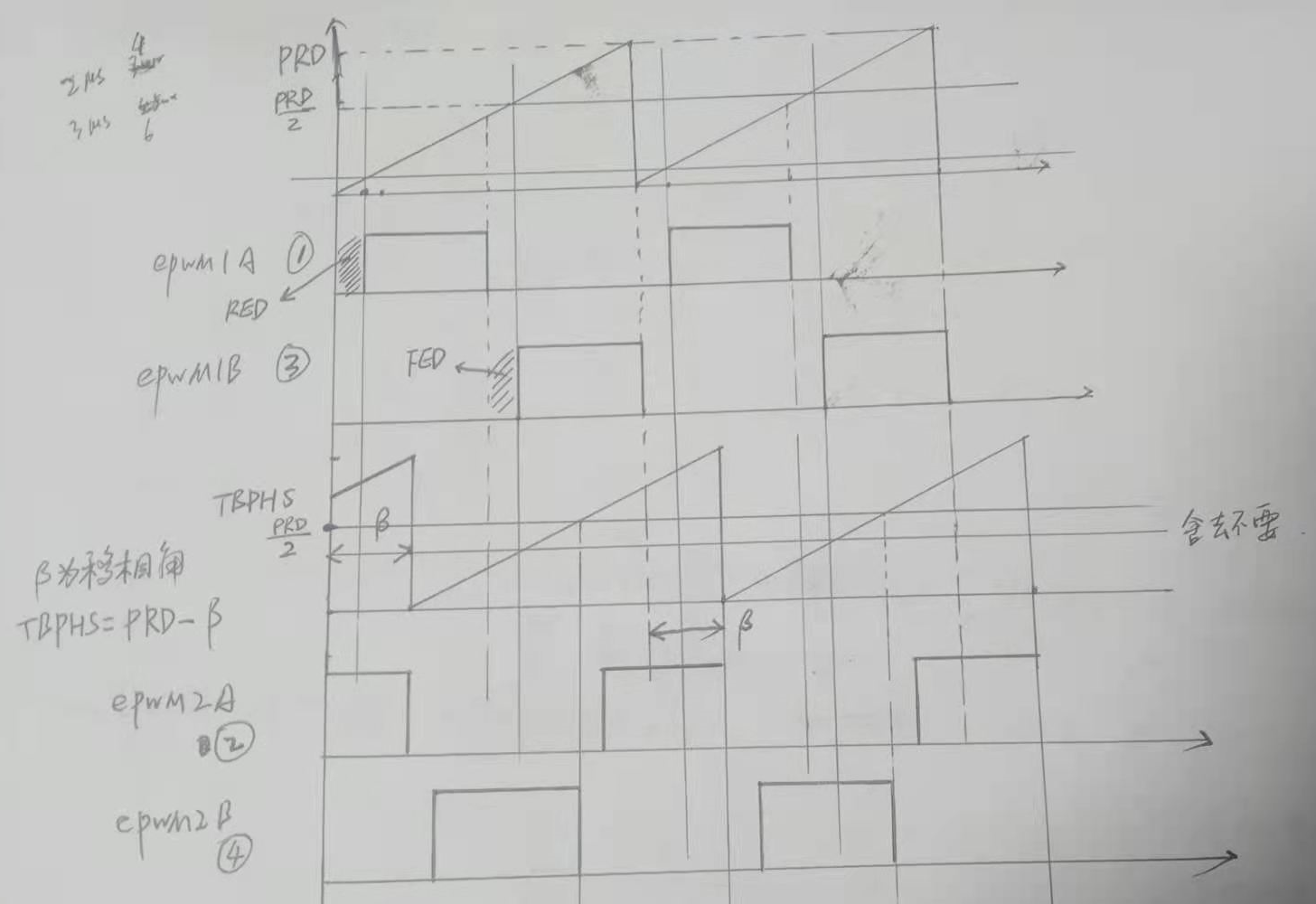

Example例子:移相全桥四路波形代码

https://www.docin.com/p-1355187078.html(参考论文)

/* * 日期:2018-1-27 * 功能:对ePWM1A和ePWM1B这一对互补信号,1为主机信号,2为从机信号 * 死区时间为2us,修改占空比只需改变移相角 * 频率为10kHz,移相位角为4us,占空比为[7500-300-yixiangjiao(600)]/15000*2=0.88 */ Uint16 yixiangjiao = 600; //移相位角为4us void InitEPwm1Example() { EPwm1Regs.TBPRD = 15000; // Period = 15000 TBCLK counts EPwm1Regs.CMPA.half.CMPA = 7500; // Set 50% fixed duty for EPWM1A EPwm1Regs.TBPHS.half.TBPHS = 0; // Set Phase register to zero EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1; EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Asymmetrical mode EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Master module EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // set actions for EPWM1A EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR; EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active Hi complementary EPwm1Regs.DBFED = 300; // FED = 300 TBCLKs initially EPwm1Regs.DBRED = 300; // RED = 300 TBCLKs initially // EPwm1Regs.DBFED = FED1_NewValue; // Update ZVS transition interval // EPwm1Regs.DBRED = RED1_NewValue; // Update ZVS transition interval } void InitEPwm2Example() { // EPWM Module 2 config EPwm2Regs.TBPRD = 15000; // Period = 15000 TBCLK counts EPwm2Regs.CMPA.half.CMPA = 7500; // Set 50% fixed duty EPWM2A EPwm2Regs.TBPHS.half.TBPHS = 0; // Set Phase register to zero initially EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1; EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP; // Asymmetrical mode EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Slave module EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW; EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // sync flow-through EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm2Regs.AQCTLA.bit.ZRO = AQ_CLEAR; // set actions for EPWM2A EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active Hi complementary EPwm2Regs.DBFED = 300; // FED = 30 TBCLKs initially EPwm2Regs.DBRED = 300; // RED = 40 TBCLKs initially // Run Time (Note: Example execution of one run-time instant) //============================================================ EPwm2Regs.TBPHS.half.TBPHS = 15000 - yixiangjiao; // Set Phase reg to 300/1200 * 360 = 90 deg // EPwm2Regs.DBFED = FED2_NewValue; // Update ZVS transition interval // EPwm2Regs.DBRED = RED2_NewValue; // Update ZVS transition interval }

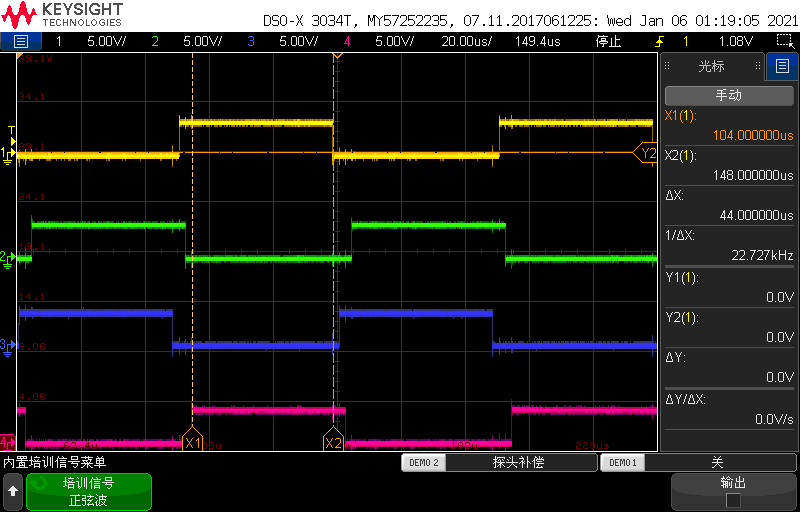

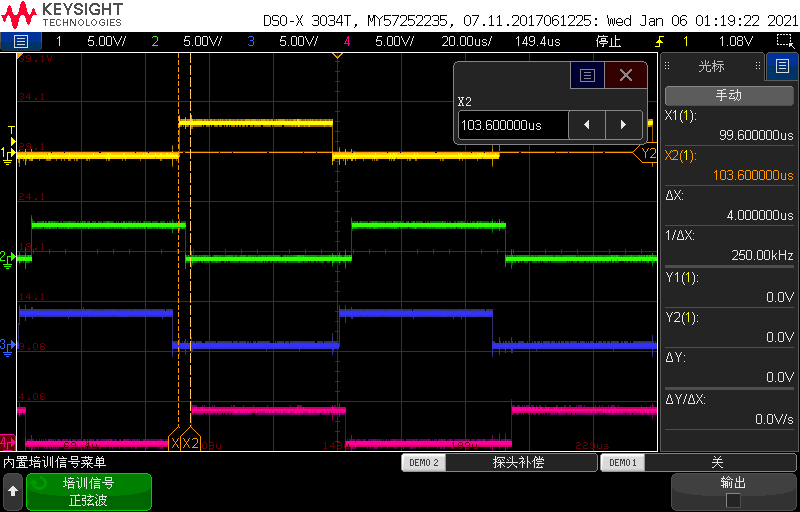

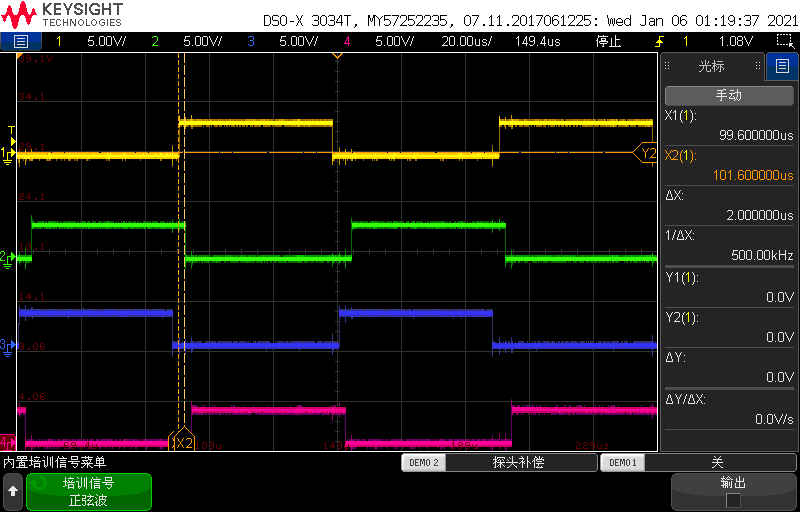

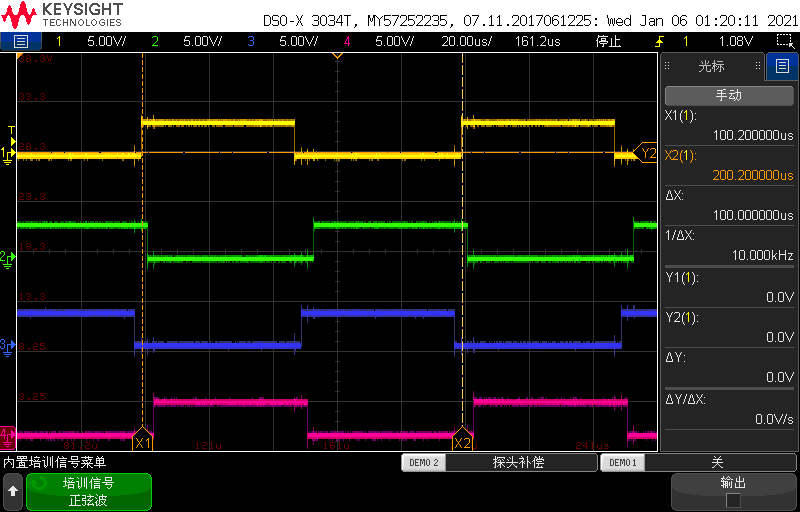

重要波形:

scope_33_占空比为0.88

scope_34_移相时间为4us

scope_35_死区时间为2us

scope_36_频率为10kHz

浙公网安备 33010602011771号

浙公网安备 33010602011771号