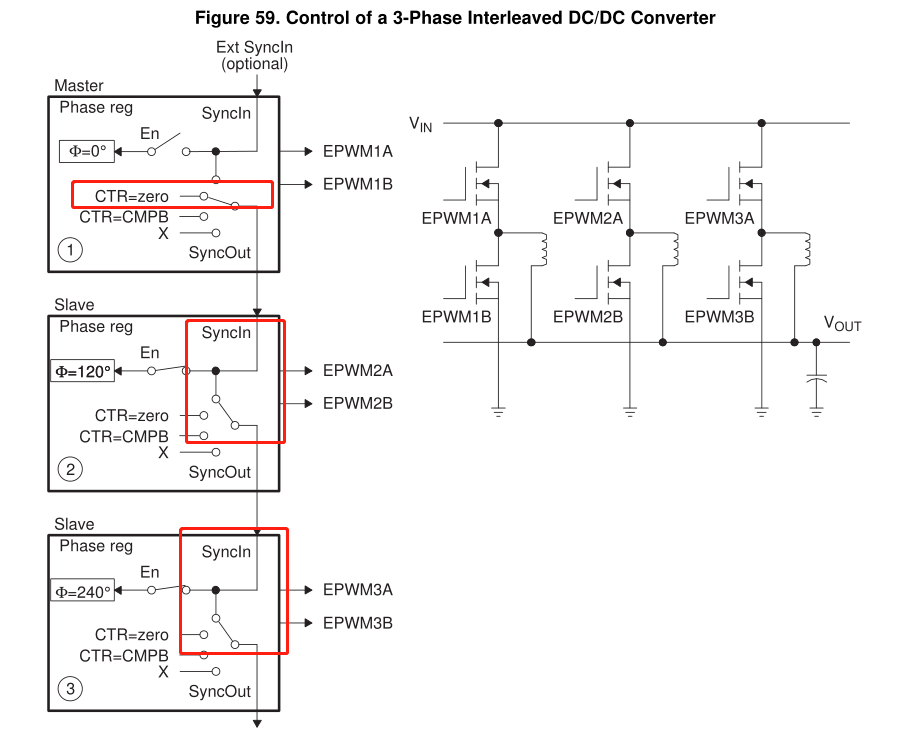

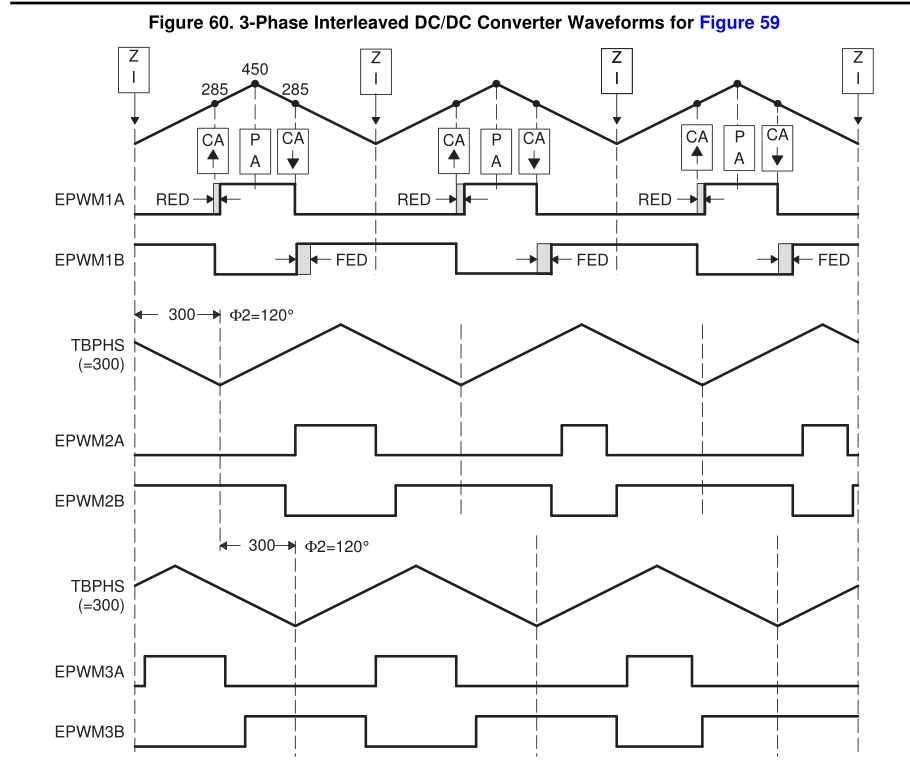

3.8 Controlling a 3-Phase Interleaved DC/DC Converter__控制三相交错DC/DC转换器_例子2:(使用方向EPwm2Regs.TBCTL.bit.PHSDIR位)

例子2:(使用方向EPwm2Regs.TBCTL.bit.PHSDIR位)

/* * 三相输入,周期为1000us,1k频率,EPWM1超前EPWM2 120度,超前EPWM3 240度。 * (1) H=2,C=1,F(TBCLK)=SYS/(H*C)=150M/(2*1)=75M * (2) 增计数模式下,TBPRD=F(TBCLK)/2/F(PWM)=37500 * (3) DBRED,DBFED虽然为16位,但仅10位有效,因此最大值为1024,值不可比1024大。 * (7) 上升沿延时的时间T=DBRED*T(TBCLK) * (4) 周期为75000,延时10us,因此EPwm1Regs.DBRED = 750; * (5) EPwm3Regs.TBCTL.bit.PHSDIR决定同步信号来临时,向上计数还是向下计数,默认向上计数(还需考证) * (6) TBPHS为同步信号来临时,装载的值。Phase = 25000/(37500*2) * 360 = 120 deg,延时了120度。 * */

void InitEPwm1Example() { // EPWM Module 1 config EPwm1Regs.TBPRD = 37500; // Period = 75000 TBCLK counts EPwm1Regs.TBPHS.half.TBPHS = 0; // Set Phase register to zero EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1 EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 1,2分频 EPwm1Regs.TBCTL.bit.CTRMODE = 2; // 增减计数模式 EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // 禁止装载 EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW; EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // Sync down-stream module(CTR=ZERO) EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // set actions for EPWM1A EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR; EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active Hi complementary(AHC模式) EPwm1Regs.DBRED = 750; // 10% 最大值为1024,10位有效 EPwm1Regs.DBFED = 750; // 10% EPwm1Regs.CMPA.half.CMPA = 37500 / 2; // 50%占空比 } void InitEPwm2Example() { // EPWM Module 2 config EPwm2Regs.TBPRD = 37500; // Period = 75000 TBCLK counts EPwm2Regs.TBPHS.half.TBPHS = 25000; // Phase = 25000/(37500*2) * 360 = 120 deg EPwm2Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1 EPwm2Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 1,2分频 EPwm2Regs.TBCTL.bit.CTRMODE = 2; // 增减计数模式 EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW; EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // sync flow-through(同步流入) EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Slave module EPwm2Regs.TBCTL.bit.PHSDIR = TB_DOWN; // Count DOWN on sync (=120 deg),同步信号来临时,向下计数 EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; // set actions for EPWM1A EPwm2Regs.AQCTLA.bit.CAD = AQ_CLEAR; EPwm2Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module EPwm2Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active Hi complementary(AHC模式) EPwm2Regs.DBRED = 750; // 10% 最大值为1024,10位有效 EPwm2Regs.DBFED = 750; // 10% EPwm2Regs.CMPA.half.CMPA = 37500 / 2; // 50%占空比 } void InitEPwm3Example() { // EPWM Module 2 config EPwm3Regs.TBPRD = 37500; // Period = 75000 TBCLK counts EPwm3Regs.TBPHS.half.TBPHS = 25000; // Phase = 25000/(37500*2) * 360 = 120 deg EPwm3Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1 EPwm3Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 1,2分频 EPwm3Regs.TBCTL.bit.CTRMODE = 2; // 增减计数模式 EPwm3Regs.TBCTL.bit.PRDLD = TB_SHADOW; EPwm3Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // sync flow-through(同步流入) EPwm3Regs.TBCTL.bit.PHSEN = TB_ENABLE; // Slave module EPwm3Regs.TBCTL.bit.PHSDIR = TB_UP; // Count Up on sync (=240 deg),同步信号来临时,向上计数 EPwm3Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW; EPwm3Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW; EPwm3Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm3Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero EPwm3Regs.AQCTLA.bit.CAU = AQ_SET; // set actions for EPWM1A EPwm3Regs.AQCTLA.bit.CAD = AQ_CLEAR; EPwm3Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // enable Dead-band module EPwm3Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active Hi complementary(AHC模式) EPwm3Regs.DBRED = 750; // 10% 最大值为1024,10位有效 EPwm3Regs.DBFED = 750; // 10% EPwm3Regs.CMPA.half.CMPA = 37500 / 2; // 50%占空比 }

(3)

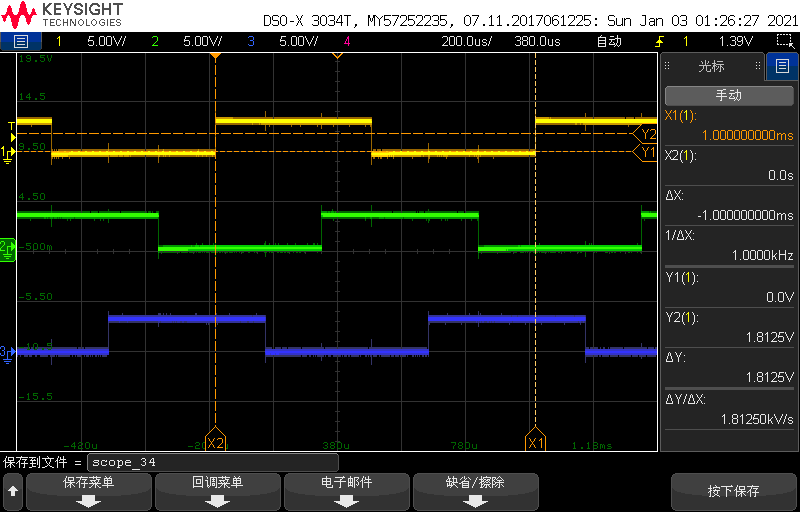

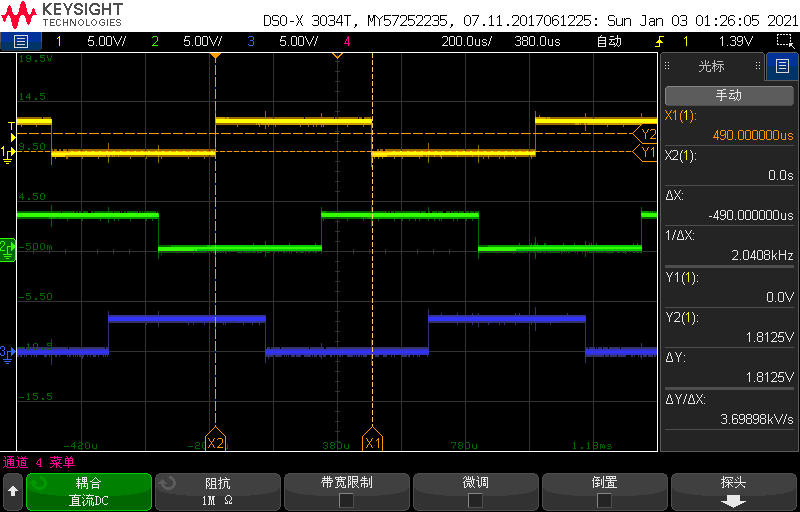

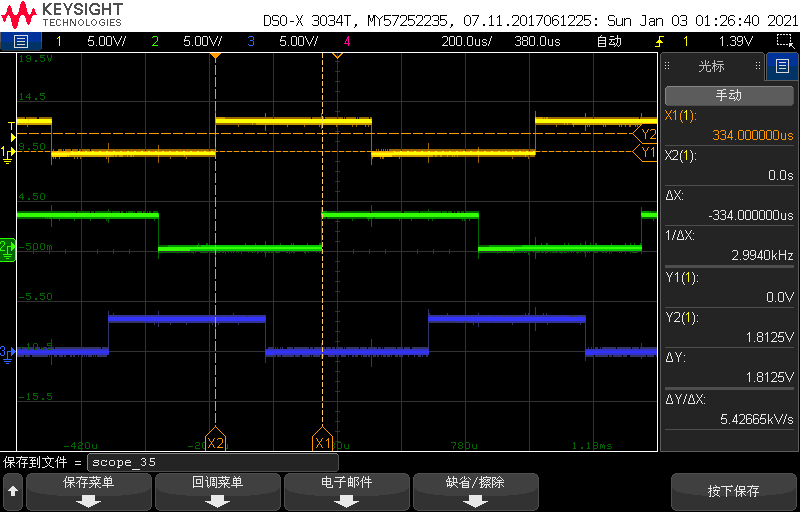

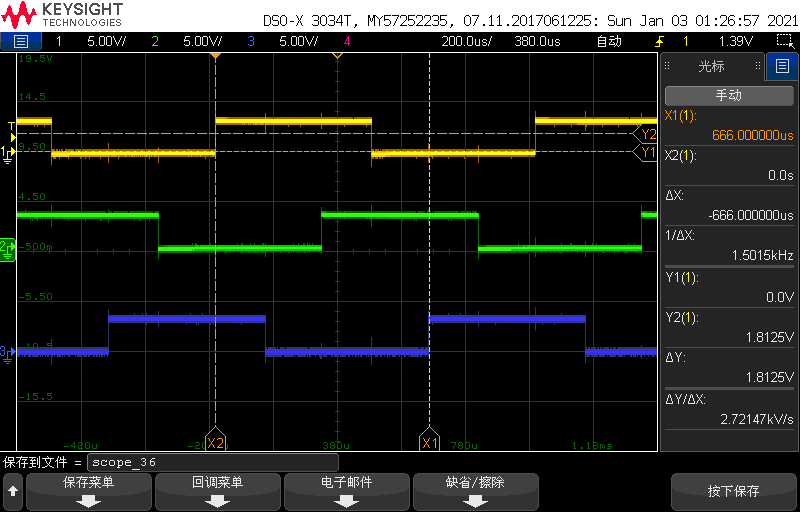

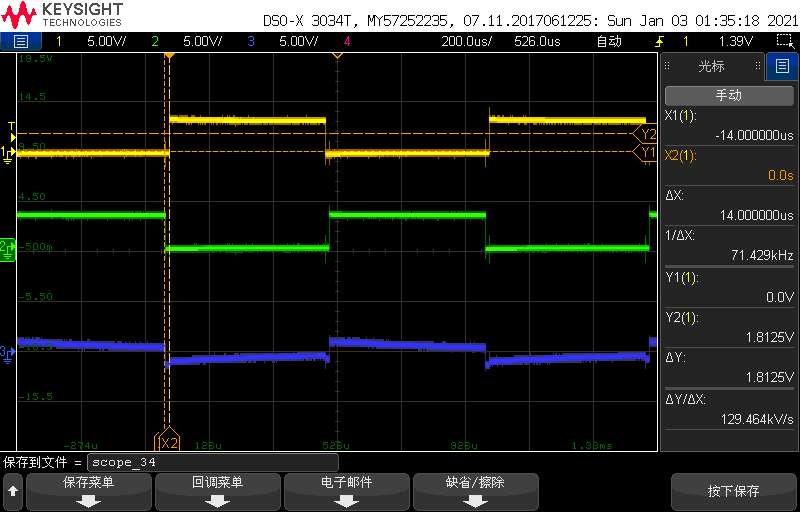

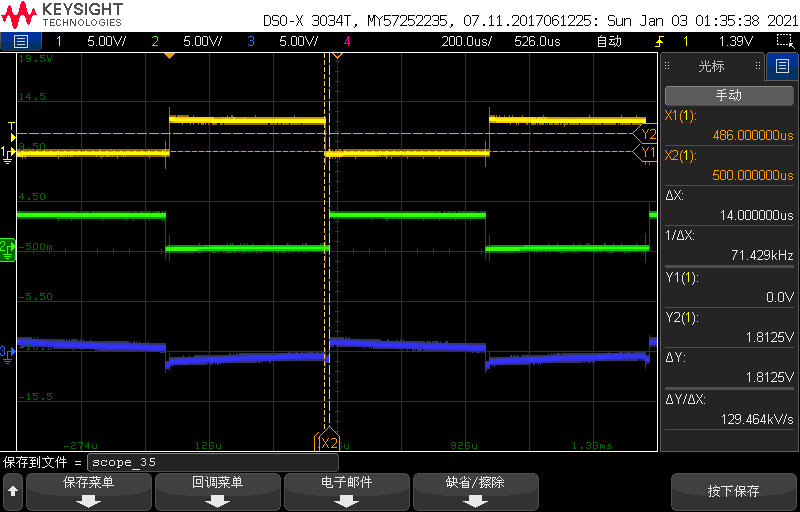

黄色:EPWM1A 绿色:EPWM2A 蓝色:EPWM3A 频率为1kHZ

占空比49%

EPWM1超前EPWM2 120度

EPWM1超前EPWM3 240度。

上升沿延时13us

下降沿延时13us

浙公网安备 33010602011771号

浙公网安备 33010602011771号