void InitEPwm1Example()

{

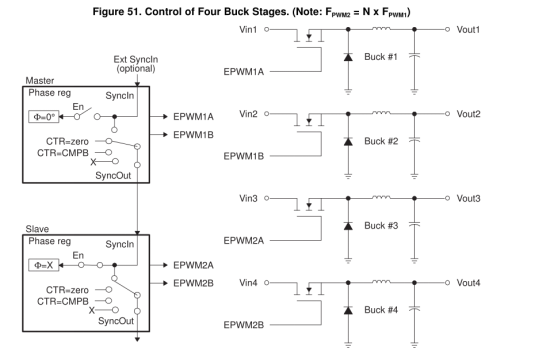

// EPWM Module 1 config

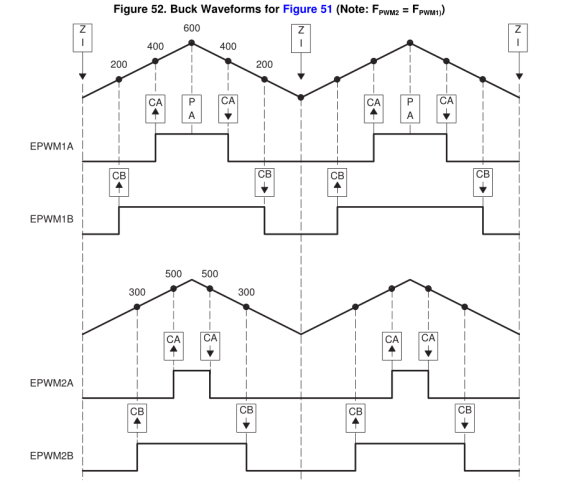

EPwm1Regs.TBPRD = 600; // Period = 1200 TBCLK counts

EPwm1Regs.TBPHS.half.TBPHS = 0; // Set Phase register to zero

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Symmetrical mode

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // Master module(主机)

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // Sync down-stream module

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero

EPwm1Regs.AQCTLA.bit.CAU = AQ_SET; // set actions for EPWM1A

EPwm1Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.CBU = AQ_SET; // set actions for EPWM1B

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm1Regs.CMPA.half.CMPA = 400; // adjust duty for output EPWM1A

EPwm1Regs.CMPB = 200; // adjust duty for output EPWM1B

}

void InitEPwm2Example()

{

// EPWM Module 2 config

EPwm2Regs.TBPRD = 600; // Period = 1200 TBCLK counts

EPwm2Regs.TBPHS.half.TBPHS = 0; // Set Phase register to zero

EPwm2Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; // Symmetrical mode

EPwm2Regs.TBCTL.bit.PHSEN = TB_ENABLE; // 从机使能

EPwm2Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm2Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; // sync flow-through(同步信号流入)

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; // load on CTR=Zero

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // load on CTR=Zero

EPwm2Regs.AQCTLA.bit.CAU = AQ_SET; // set actions for EPWM2A

EPwm2Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm2Regs.AQCTLB.bit.CBU = AQ_SET; // set actions for EPWM2B

EPwm2Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm2Regs.CMPA.half.CMPA = 500; // adjust duty for output EPWM2A

EPwm2Regs.CMPB = 300; // adjust duty for output EPWM2B

}

![]()

![]()

浙公网安备 33010602011771号

浙公网安备 33010602011771号