gem5_cache_分区与不同读写延迟设置

1. gem5 cache: 若采用gem5的classic缓存模型,是不支持多bank模式的,需自己配置。操作如下:

src/mem/cache/

a.【src/mem/cache/Cache.py】cache 的声明源代码:定义了cache的基本参数,以及三个文件:cache.hh, base.hh, noncoherent_cache.hh;

在该文件中添加:enable_bank_model, num_banks, bank_intlv_high_bit

class BaseCache(ClockedObject): type = 'BaseCache' abstract = True cxx_header = "mem/cache/base.hh"

size = Param.MemorySize("Capacity")

assoc = Param.Unsigned("Associativity")

tag_latency = Param.Cycles("Tag lookup latency")

data_latency = Param.Cycles("Data access latency")

response_latency = Param.Cycles("Latency for the return path on a miss");

# reset by zhengyi enable_bank_model = Param.Bool(True,

"knob to control is the bank model is used")

num_banks = Param.Undesigned(1,"Number of cache data array banks")

bank_intlv_hifh_bit = Param.Int(0,

"cache data array bank interleave highest bit"

"(0=automatically alighed to cache line granularity)")

# reset over

b. 【src/mem/cache/base.hh】

需要修改的地方很多,参考链接:

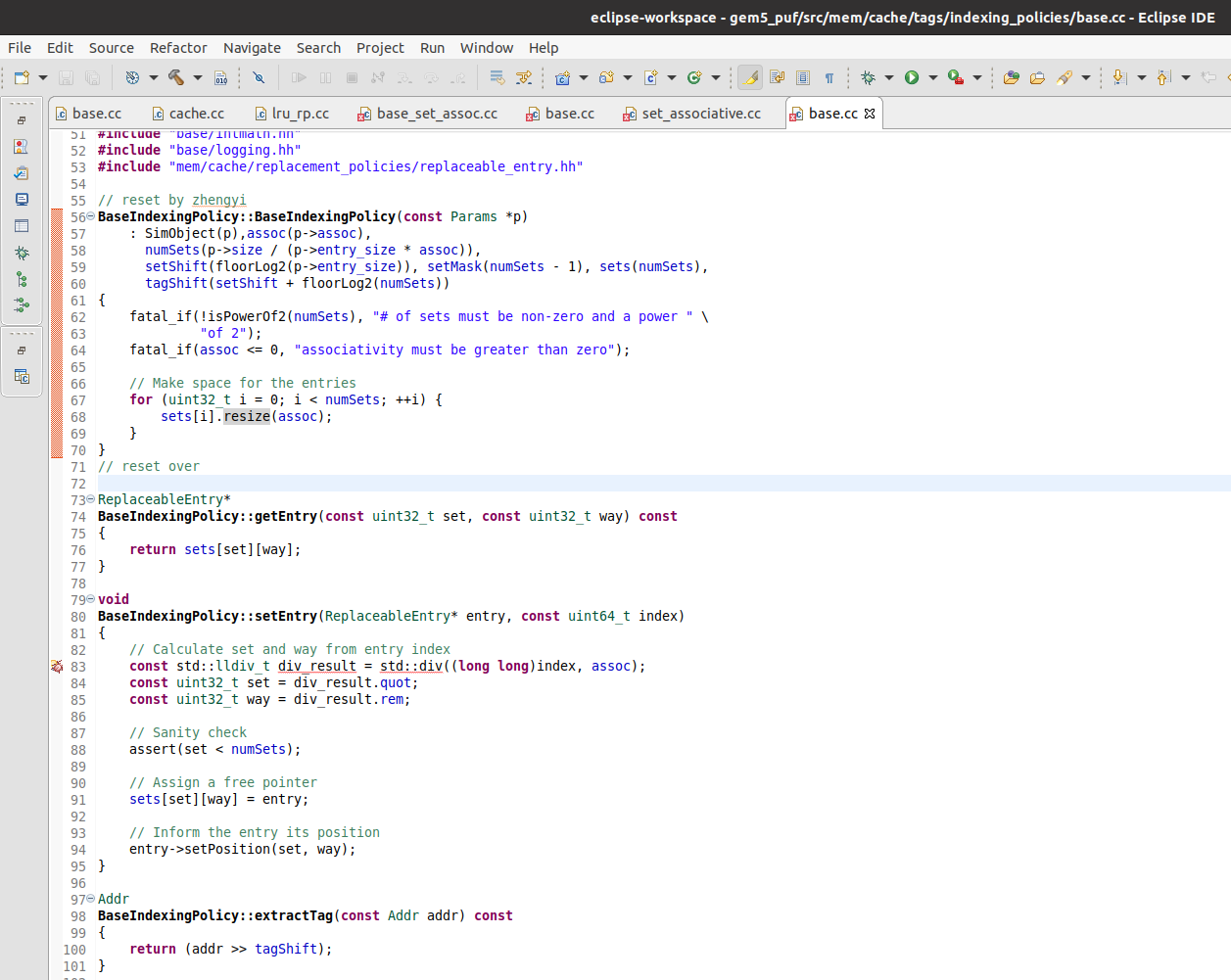

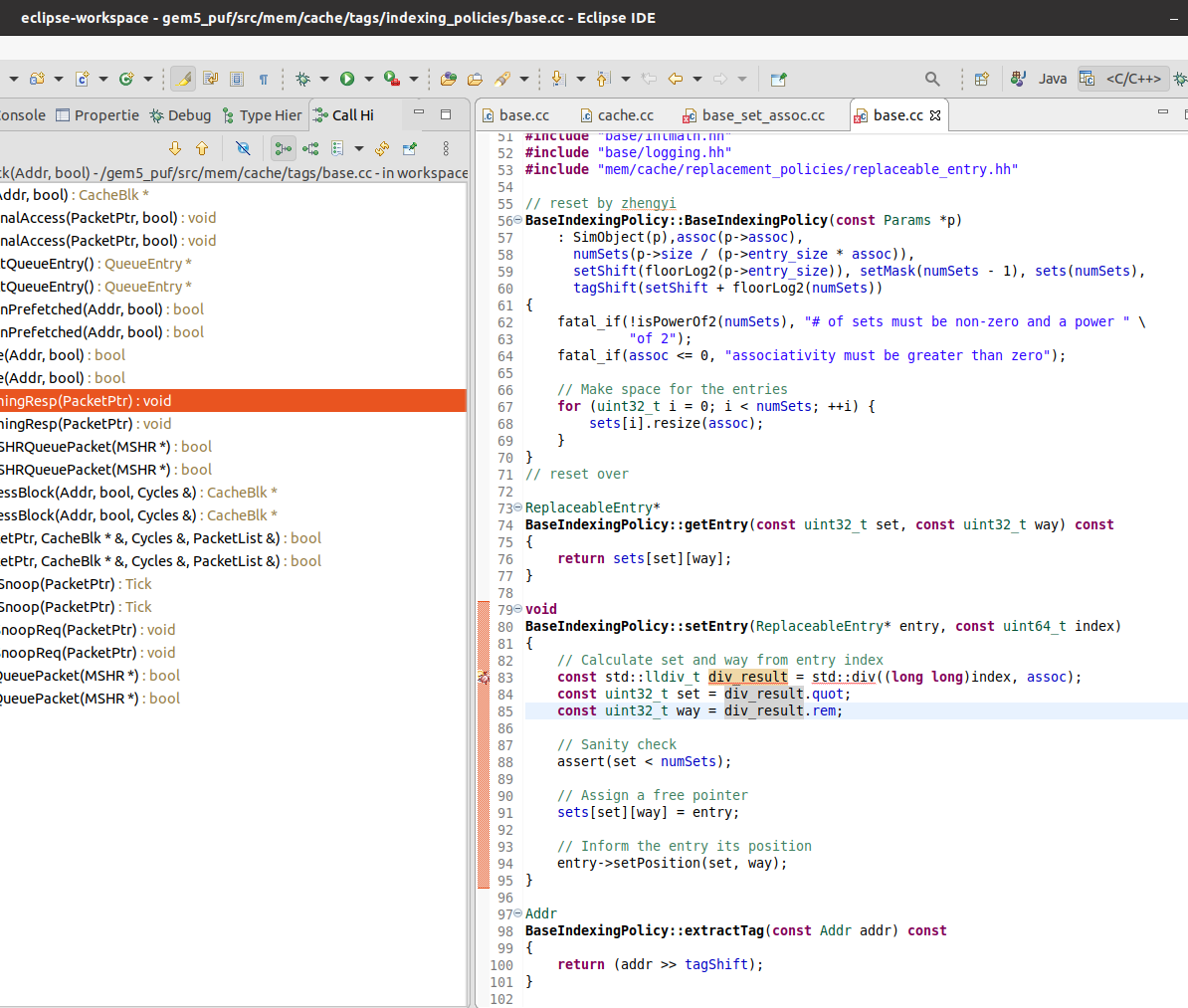

c. 【src/mem/cache/base.cc】cache 代码源文件

需要修改的地方很多,参考链接:

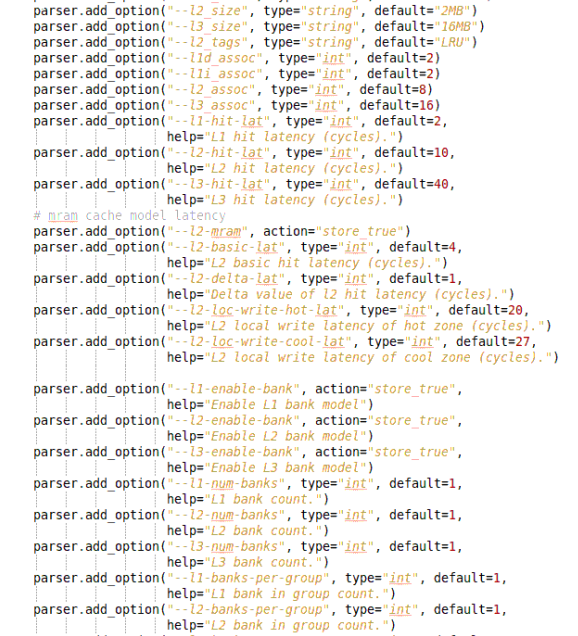

configs/common/ : 这部分主要定义cache的参数配置,默认值等;

a. 【configs/common/Options.py】定义常用的变量的初始值;在其中添加--part定义,此为LLC分区的块数,默认64;

# Cache Options parser.add_option("--external-memory-system", type="string", help="use external ports of this port_type for caches") parser.add_option("--tlm-memory", type="string", help="use external port for SystemC TLM cosimulation") parser.add_option("--caches", action="store_true") parser.add_option("--l2cache", action="store_true") parser.add_option("--num-dirs", type="int", default=1) parser.add_option("--num-l2caches", type="int", default=1) parser.add_option("--num-l3caches", type="int", default=1) parser.add_option("--l1d_size", type="string", default="64kB") parser.add_option("--l1i_size", type="string", default="32kB") parser.add_option("--l2_size", type="string", default="2MB") parser.add_option("--l3_size", type="string", default="16MB") parser.add_option("--l1d_assoc", type="int", default=2) parser.add_option("--l1i_assoc", type="int", default=2) parser.add_option("--l2_assoc", type="int", default=8) parser.add_option("--l3_assoc", type="int", default=16) # reset by zhengyi parser.add_option("--l1_enable_bank", action="store_true", help="Enable L1bank model") parser.add_option("--l2_enable_bank", action="store_true", help="Enable L2bank model") parser.add_option("--l3_enable_bank", action="store_true", help="Enable L3bank model") parser.add_option("--l1_num_banks", type="int", default=1, help="L1 bank count") parser.add_option("--l2_num_banks", type="int", default=1, help="L2 bank count") parser.add_option("--l3_num_banks", type="int", default=1, help="L3 bank count") parser.add_option("--l1_intlv_bit", type="int", default=0, help="L1 bank interleave highest bit") parser.add_option("--l2_intlv_bit", type="int", default=0, help="L2 bank interleave highest bit") parser.add_option("--l3_intlv_bit", type="int", default=0, help="L3 bank interleave highest bit") parser.add_option("--cacheline_size", type="int", default=64) # reset over

b. 【configs/common/CacheConfig.py】定义cache的基本配置,1/2级缓存,及其分区,替换策略等;在该文件中,为每一级cache添加bank相关属性;

# reset by zhengyi ################## if options.l2cache: # Provide a clock for the L2 and the L1-to-L2 bus here as they # are not connected using addTwoLevelCacheHierarchy. Use the # same clock as the CPUs. system.l2 = l2_cache_class(clk_domain=system.cpu_clk_domain, size=options.l2_size, assoc=options.l2_assoc, enable_bank_model=options.l2_enable_bank, num_banks=options.l2_num_banks, bank_intlv_high_bit=options.l2_intlv_bit) .... if options.memchecker: system.memchecker = MemChecker() for i in range(options.num_cpus): if options.caches: icache = icache_class(size=options.l1i_size, assoc=options.l1i_assoc, enable_bank_model=options.l1_enable_bank, num_banks=options.l1_num_banks, bank_intlv_high_bit=options.l1_intlv_bit) dcache = dcache_class(size=options.l1d_size, assoc=options.l1d_assoc, enable_bank_model=options.l1_enable_bank, num_banks=options.l1_num_banks, bank_intlv_high_bit=options.l1_intlv_bit) ################# reset by zhengyi over

c. 【configs/common/Caches.py】各级缓存默认参数设置:

class L1Cache(Cache): assoc = 2 tag_latency = 2 data_latency = 2 response_latency = 2 mshrs = 4 tgts_per_mshr = 20 enable_bank_model = False class L1_ICache(L1Cache): is_read_only = True # Writeback clean lines as well writeback_clean = True class L1_DCache(L1Cache): pass class L2Cache(Cache): assoc = 8 tag_latency = 20 data_latency = 20 response_latency = 20 mshrs = 20 tgts_per_mshr = 12 write_buffers = 8 enable_bank_model = False class IOCache(Cache): assoc = 8 tag_latency = 50 data_latency = 50 response_latency = 50 mshrs = 20 size = '1kB' tgts_per_mshr = 12 enable_bank_model = False class PageTableWalkerCache(Cache): assoc = 2 tag_latency = 2 data_latency = 2 response_latency = 2 mshrs = 10 size = '1kB' tgts_per_mshr = 12 enable_bank_model = False

2. gem5: different read and write latency of cache.

注:新版gem5中,关于latency的源代码部分从src/mem/cache/tag/中迁移到了src/mem/cache/base.cc

1. 修改: src/mem/cache/BaseCache.py (老版本,新版本中是:gem5/src/mem/cache/Cache.py)

将默认的hit_latency视为 read_latency; 添加自定义的 write_latency;

block_size = Param.Int("block size in bytes")

hit_latency = Param.Cycles("The hit latency for this cache")

+ write_latency = Param.Cycles("The write latency for this cache")

response_latency = Param.Cycles(

"Additional cache latency for the return path to core on a miss");

#reset by bi

class BaseCache(MemObject): type = 'BaseCache' cxx_header = "mem/cache/base.hh" assoc = Param.Int("associativity") basic_latency = Param.Cycles("The hit latency for the first line of this cache") delta_latency = Param.Cycles("The hit latency for hit one more line") loc_write_hot_latency = Param.Cycles("Additional latency for write one line in hot zone.") //reset by bi loc_write_cool_latency = Param.Cycles("Additional latency for write one line in cool zone.")//reset by bi response_latency = Param.Cycles( "Additional cache latency for the return path to core on a miss")

2. 修改: src/mem/cache/base.hh;

添加 write_latency 的 const 定义,以及bank group ID

const Cycles writeLatency;

/**

* Return Bank Group ID. according to BankId(Bi set)

*/

unsigned

getGroupId(unsigned bankId, int bank_num_per_group) const

{

double temp_id = ceil(bankId/bank_num_per_group); //get double type group_id

unsigned group_id = (unsigned)(temp_id); //convert double type to unsigned type

return group_id;

}

/** * Return Bank Group Read Latency. according to GroupId(Bi set) */ //unsigned //getGroupReadLatency(unsigned groupId, unsigned latency) const //{ // double deta = 1/clock; // latency = latency + ((int)((groupId-1)*deta+0.001))+1; // return latency; //} /** * Return Bank Group Write Latency. according to GroupId(Bi set) */ //unsigned //getGroupWriteLatency(unsigned groupId, unsigned latency) const //{ // double deta = 1/clock; // latency = latency + ((int)((groupId-1)*deta+0.001))+1; // return latency; //}

3. 修改: src/mem/cache/cache_impl.cc:

如果 way == assoc -1,那么它是该组的最后一路。定义为PUF其中一路。

这里是分组的位置,index为blk的索引编号,assoc为相联系数--即路数or每组的blk数

各延迟的初始值

浙公网安备 33010602011771号

浙公网安备 33010602011771号