FPGA基础03-二进制与格雷码转换

1.格雷码概念

格雷码的特点是从一个数变为相邻的一个数时,只有一个数据位发生跳变,由于这种特点,就可以避免二进制编码计数组合电路中出现的亚稳态。

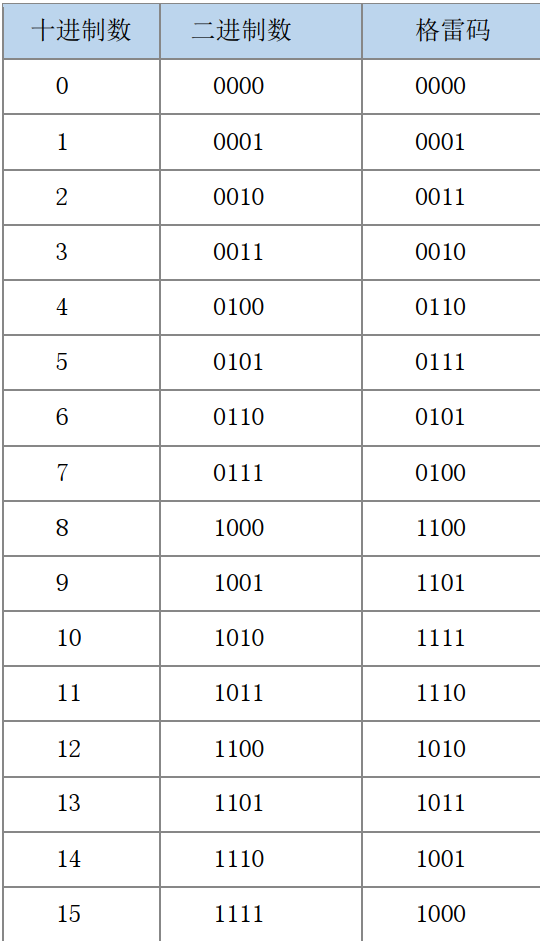

例子:

由上图可知:十进制3跳变到4时,二进制每一位都在发生变化,如果直接使用异步时钟采样这些数字信号,这就很可能会发生亚稳态或者数据采样错误,而采用格雷码,也最多1位数据出错。

2.二进制转格雷码

2.1 理论分析

(1)二进制的最高位作为格雷码的最高位;

(2)次高位的格雷码为二进制的高位和次高位相异或得到;

(3)其他位与次高位类似;

2.2 实际计算

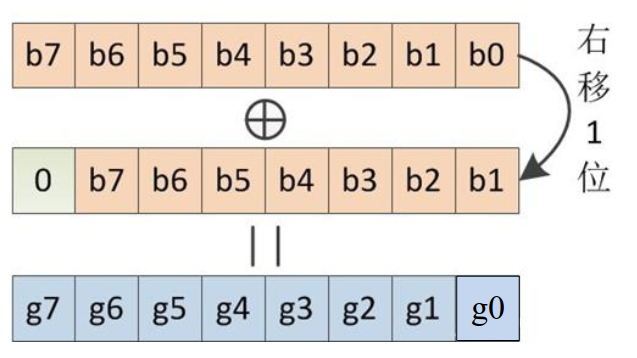

在具体计算时,可将二进制码右移 1 位后与本身异或,其结果就是格雷码。示意图如下:

分析:b7^0还是本身,所以g7 = b7,符合理论分析中的(1),后续步骤也符合(2)(3)。

3.格雷码转二进制

3.1 理论分析

(1)使用格雷码的最高位作为二进制的最高位;

(2)二进制次高位产生过程是使用二进制的高位和次高位格雷码相异或得到;

(3)其他位的值与次高位产生过程类似;

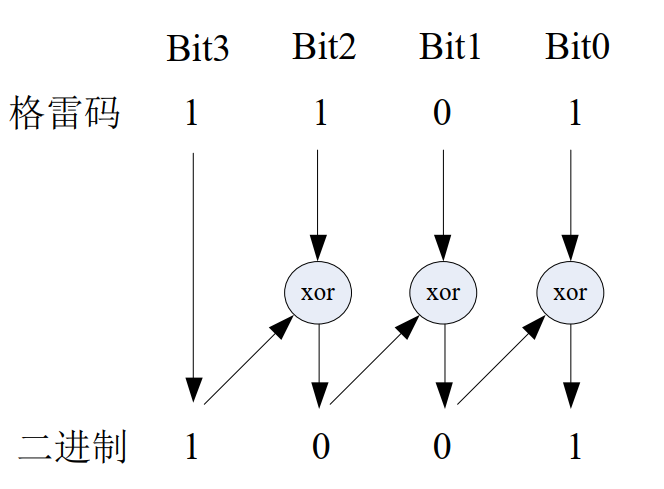

3.2 图解(位宽为4)

4. 应用

格雷码常用于通信, FIFO 或者 RAM 地址寻址。具体来说,就是在异步FIFO设计中,两侧信号属于不同时钟域,FIFO必须通过对比来自不同时钟域的读写地址指针数值给出空满指示信号,

地址指针需要多个比特信号才能代表FIFO深度,而格雷码的单比特变化特性正好适用于这一场合。

参考:正点原子逻辑设计指南

浙公网安备 33010602011771号

浙公网安备 33010602011771号