6.16-多周期MIPS CPU数据通路(2)

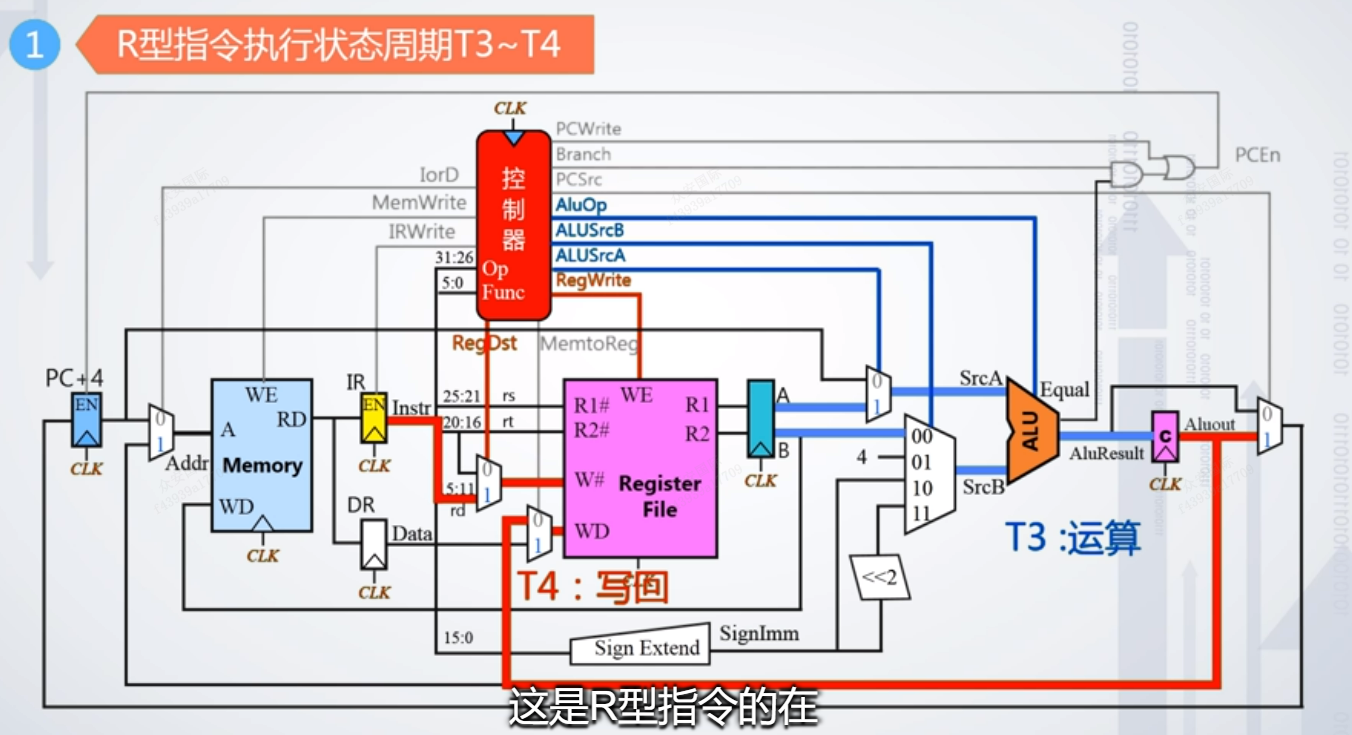

R型指令执行状态周期T3-T4

- R型指令完成基本的运算,当A和B对应的选择信号就绪以后,ALU给出一个对应的运算符,就可以完成响应的运算,将结果送入C寄存器的输入端,给出对应的控制信号才可以建立响应的数据通路T3,第三个节拍完成实际的R型指令的运算,根据R型指令的Funct字段,完成不同的运算,运算结果会送到C端,当时钟周期来临的时候,C会被更新为R型指令的运算结果

- 在第四拍将会将C值写回到R寄存器中,所以第四拍要将对应的目的寄存器编号送到写寄存器的输入端,要将写回的值经过响应的选择,选择到通用寄存器的多路选择器的对应的输入端,MemTorReg的选择信号来控制,输出到通用寄存器。所以第四个时钟周期来临,寄存器的值加上这个寄存器写信号以后,在时钟的配合下可以将寄存器的值改写。

- 这就是R型指令执行的通路,T3用作运算,运算完的结果送到C寄存器,T4响应的数据写到寄存器中,第四个时钟用来写回

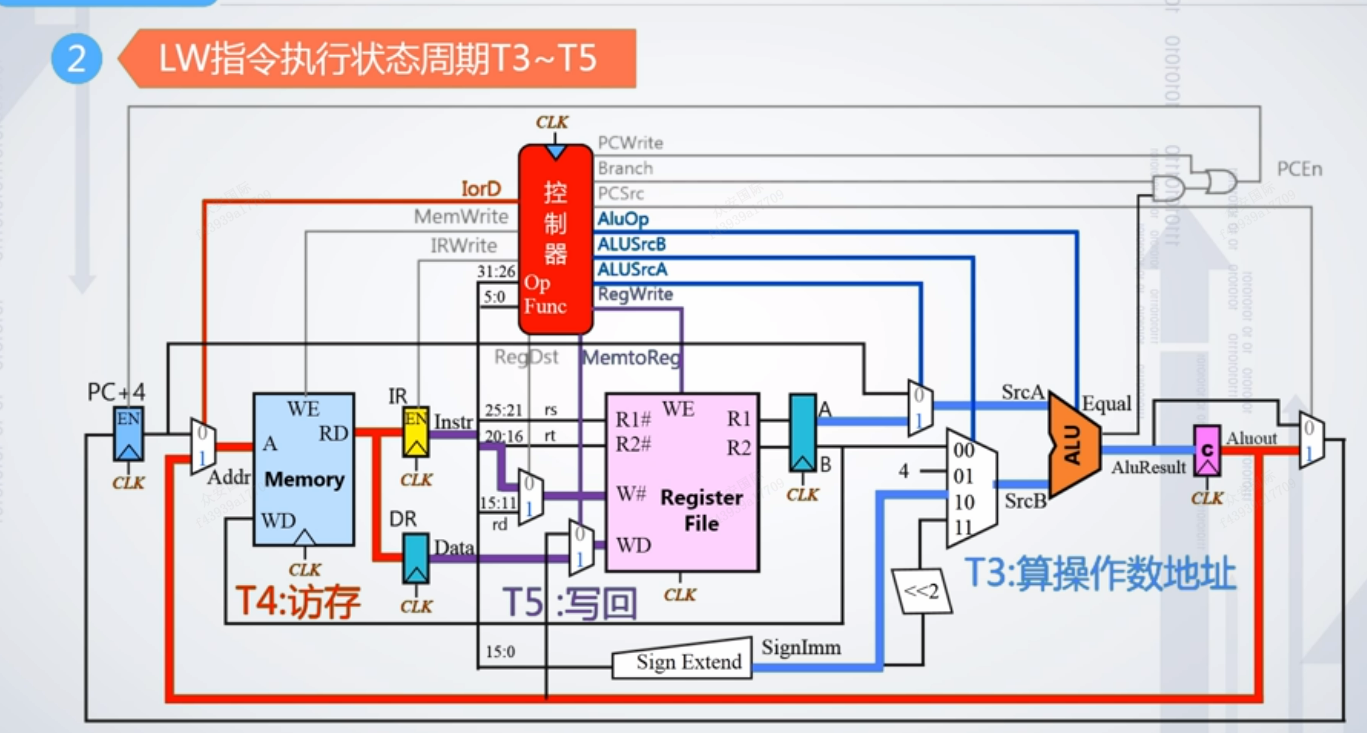

LW指令执行状态周期T3-T5

LW指令涉及到访存,所以第一步工作要先计算内存地址,也是ALU将对应的A值和对应的立即数进行加法操作,完成响应的结果得到一个地址,这个地址也是也是输入到C寄存器中

- 当第一个时钟T3来临的时候完成了响应地址的计算,要给出三个对应的控制信号建立响应的数据通路,将地址计算完成以后送到C寄存器,有了地址之后下一步就是访问主存的操作数

- 需要将C值写入以后再第三个节拍,将C值传递到Memory中,给出对应的Lod对应的控制信号,走这条通路访问主存,将数据从主存中取出,经过通路送到DR中,DR没有写使能,所以时钟到来之后DR的值会被锁存为新的数据,我们响应的操作数据就会被锁存再DR中,DR没有任何的写使能,DR会被锁存为新的值,响应的数据就会锁存到DR中

- 第四拍到来的时候,完成了去操作数访存的过程,第五拍来临的时候我们再将对应的数据由DR写入到寄存器文件中,完成寄存器的写回

- LW指令需要三个时钟周期才能够完成,总的需要五个时钟周期,最后完成数据的写回

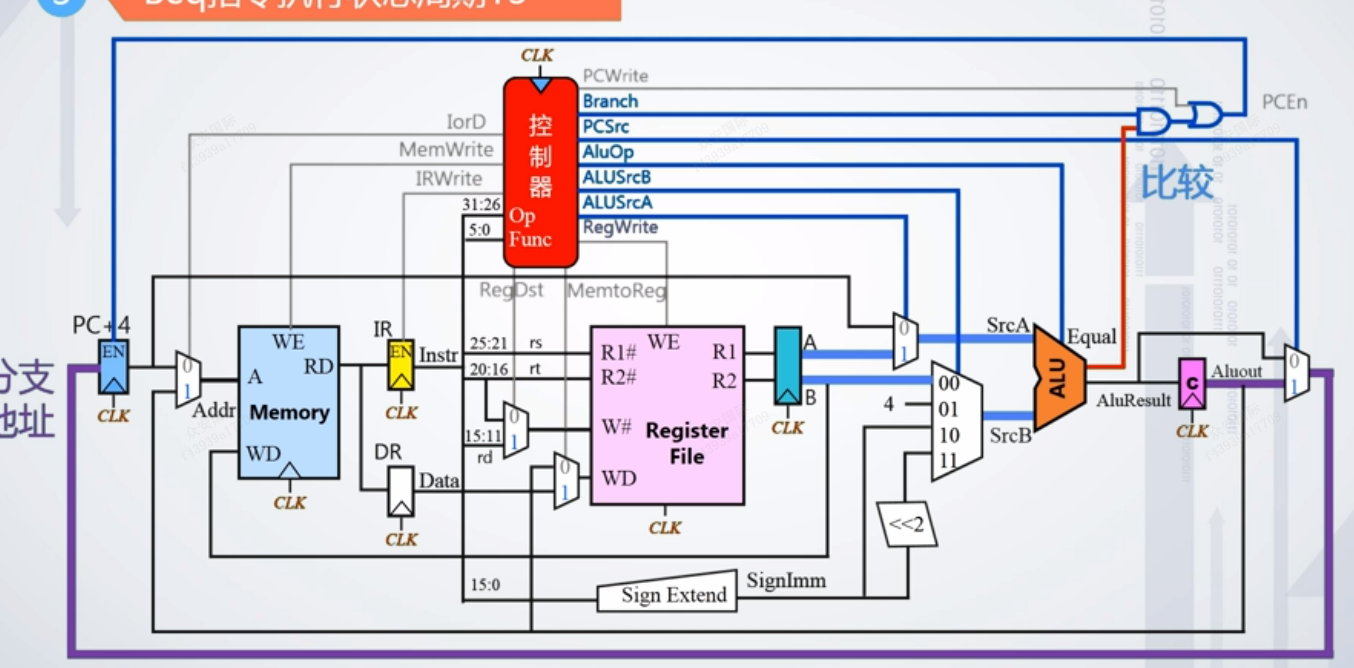

Beq指令执行状态周期T3

Beq指令只需要比较两个寄存器的值是否相等,而寄存器的值已经存在A和B寄存器中,只需要给出对应的控制信号将A和B的值送到ALU,由ALU进行运算equals信号然后由分支指令Branch与以后产生对应的分支选择控制信号,选择分支地址,分支地址在取指令的第二个节拍已经存储在C寄存器中,所以只需要选择响应的多路选择器,将C寄存器的值送到这边就可以由响应的分支指令的分支条件来控制是否进行分支,所以对于Beq指令只需要一个时钟周期

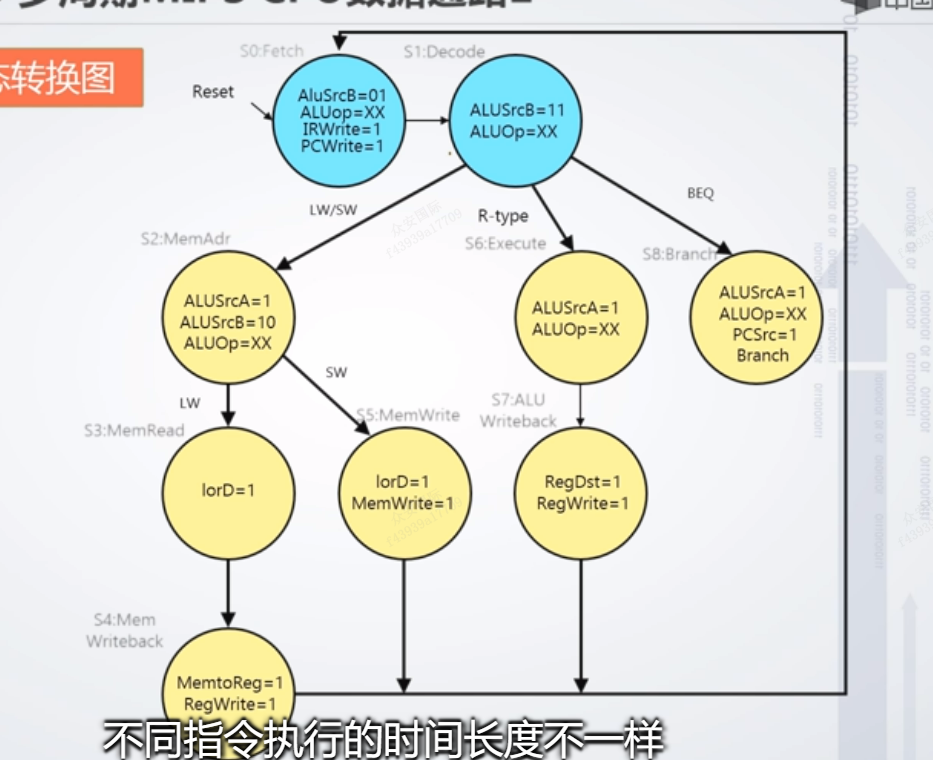

多周期状态转换图

将所有数据通路的不同状态构建为一个状态图,就可以形成多周期MIPS CPU数据通路的状态转换图

- 其中S0表示取指令,以PC为地址访问内存送到指令寄存器IR中同时PC = PC + 4取指令部分

- 第二个状态是指令译码阶段,去操作数,计算分支指令地址,取指令需要两拍蓝色部分

- 取完指令之后根据指令的功能进入到不同的状态,如果是访存指令进入到一个状态,如果是R型指令进入到另一个状态。访存需要三个指令周期,SW需要两个指令周期,R型需要两个,Beq需要一个

浙公网安备 33010602011771号

浙公网安备 33010602011771号