概述

最近在折腾IIC相关的程序。结合IIC协议,以及在GPIO模拟IIC的同时又对IIC有了新的认识。

只使用ADuc7126的GPIO实现了IIC主机的基本收发功能,并没有相关的仲裁等等。

资料

IIC

参阅的是这本网上流传的周立功整理的IIC协议pdf;

链接:https://pan.baidu.com/s/1hRbO0Pff8M3wVDzEixChoA

提取码:IIC0

IIC,有SDA、SCL两根线,线上各个器件引脚为“线与”的关系。且需要加上拉电阻。空闲状态下SDA、SCL均为1;则可以认识由0到1就是释放动作,由1到0就是占用动作。

IIC 主机模式下,基本动作有: 产生开始信号(S),产生停止信号(P),产生应答(ACK),不产生应答(NACK)

IIC基本动作

-

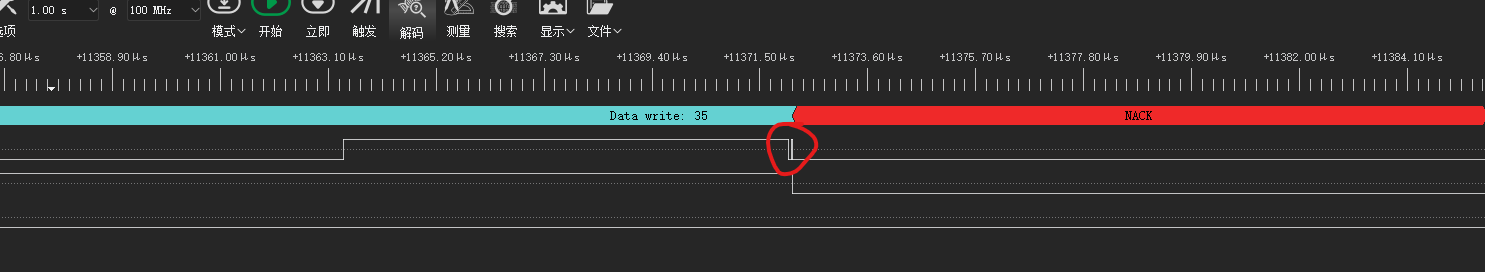

不产生应答(NACK)

之前一直不理解这个NACK,在某些资料和博客上,有将其认为是与(ACK)对应的信号,可能叫做“应答非信号”更加合适。

现在来看,如果将

(pdf P9)

细节

- IIC从机不会主动拉低SCL,但是可以延迟释放SCL。

![]()

(pdf P7)

(pdf P6)

程序实例

这里首先以IIC与AT24EEPROM芯片通信,以其随机连续读写为例。(因为这个过程中会涉及到IIC主机的所有基本操作)

IIC程序设计

首先,当然是模拟出各个基本的动作。另外还需要注意一下建立时间、保持时间及输出延迟的问题。需要在某些步骤之间,添加合适的延时,以期待足够的时间来生效。

其他

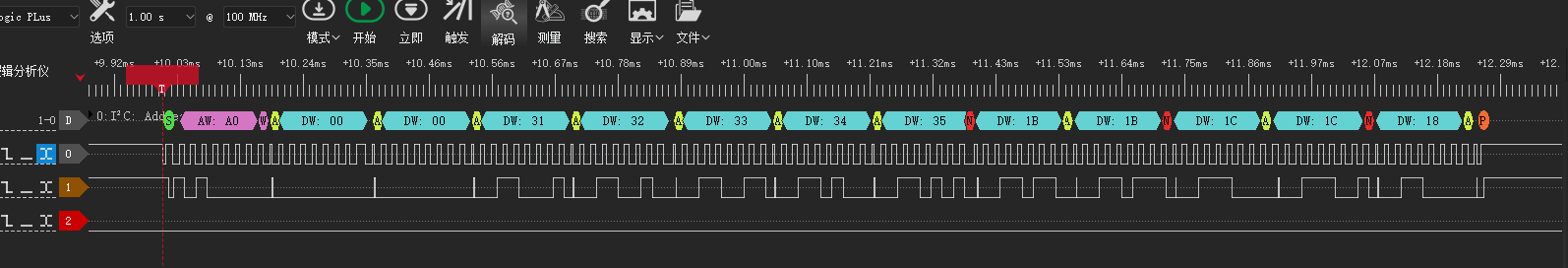

调试过程中,由于是用逻辑分析仪调试,测得的写时序老是发现有毛刺,而造成写数据错误。

(全图)

(局部)

一直认为是基本的IIC模拟出现了问题,以为是哪里延时不够,造成器件反应错误。

而且还是偶发性错误,毛刺大概在写字节时出现,概率为10%。而且大概有90%是出现在如图的一个字节末尾;少量出现在字节中间。

调了一下午,错误依旧,急的直挠头。

走投无路之下,反复找时序图细节规律时,偶然间发现那个高电平毛刺的长度一直是10ns,看见100MHz的采样率,一拍大腿,开始想到会不会跟逻辑分析仪有关。

这时直接用IIC总线读取刚才写入的数据,才发现完全没有问题。

从新连接了一下逻辑分析仪和IIC引脚,发现正常了,试了十几次问题也不复现。

大概是是逻辑分析仪接触不良或者是外界干扰的原因。

总结及感悟

工作以来,愈发感觉校园自由时光的珍惜宝贵。

身边寻常的事物,往往只有失去后才会察觉。

遗憾大学时没有钻研知识,光阴虚度。

大学时玩心太大,一事无成。虽有时也能感觉做技术的有趣之处,但奈何还是抵不过对STEAM的向往。

时光易逝人易老。

劝君莫惜金缕衣,劝君惜取少年时。花开堪折直须折,莫待无花空折枝。

浙公网安备 33010602011771号

浙公网安备 33010602011771号