计算机基础补充:电子技术基础 - 术语整理

这篇文章也是一时兴起,这几天我继续自己原来的计划,将 计算机组成原理、数据结构、操作系统 ,全部都再刷一遍,所有的真题,全都放到博客上来。

Q1:至于为什么这么干?

一方面,我们依托于 王道单科书 ,本来也没打算挑战现有的已经很流行的考研复习资料,基于这些材料, 我们 进一步理解、整理、精简,用于自己学习之用 。

Q2:为啥要整理数电、模电、通信原理和微机原理的术语呢?

主要由于 408 越来越难了吧。虽然送分题不少,但是很多问题不深入研究压根连入手的切入点都没有,笔者几经思考,决定还是拿出当年自己做咨询的力气,把这些基础课啃一啃,也算是对于行业知识继续夯实。

我自己的专业,应该于今年 Q4 回归正常轨道,业务方向可以在今年年底前基本锚定,是否能赚钱 —— 我们也不知道,我们希望,先争取一些用户,这些用户未必是最终付钱的客户,但是,他们是我们的用户。

为了鼓励各路 DS,也包括我,看一个我自己还挺喜欢的 TED。

https://www.bilibili.com/video/BV1GP411T7V6/?spm_id_from=333.337.search-card.all.click&vd_source=63764dd9776224d187bddddb05bf9f3f

学习吧!!少年!!

--------------- 分割线 -----------------

关于课程目的

我仔细读了读前序,作者康华光系华中科技大学博导。序言,讲清基本概念、基本电路的工作原理和基本方法。对主要技术指标,采用工程近似方法进行计算,针对专业的学生,还有进一步的要求。

作为爱好者,或者咨询师,暂且认为,本书主要目的,理解行业属于,了解基本电路。

关于本书目录

1.数字逻辑概论

2.逻辑代数与硬件描述语言基础

3.逻辑门电路

4.组合逻辑电路

5.锁存器和触发器

6.时序逻辑电路

7.存储器、复杂可编程器件和现场可编程门阵列

8.脉冲波形的变换与产生

9.数模与模数转换器

10.数字系统设计基础

第一章 数字逻辑概论

1.关于集成度分类,数字集成电路分为

2.按照结构工艺

双极型、MOS型、双极-MOS型

MOS,金属氧化物半导体

TTL 晶体管-晶体管逻辑门电路

3.数字电路

数字电路处理的是数字信号。数字电路又称逻辑电路,电路结构、功能特点不同于模拟电路,研究对象是电路的输出与输入之间的逻辑关系。采用的工具,逻辑代数,表达电路输入输出的关系,主要有真值表、功能表、逻辑表达、波形图。

数字电路设计,给定逻辑功能,要求确定输入、输出、选择适当逻辑器件。

4.数字信号和模拟信号

模拟信号:时间上连续变化的物理量,幅值也是连续变化的。例如,速度、压力等。

数字信号:与模拟信号相对的是数字信号。离散时刻取值,数值大小和每次的增减都是量化单位的整数倍。时间离散,对应的数值也离散。

5.数字逻辑、逻辑电平

数字逻辑:只用 0-1表示,简称数字逻辑。

电压介于 3.5-5伏特,表示1,高电平H;

电压介于 0-1.5伏特,表示0,低电平L。

注意,逻辑电平不是物理量。

6.数字波形

数字波形分为归零型和非归零型。

归零型:一个节拍(时钟周期)内,有脉冲代表1,无脉冲代表0;

非归零型:一个节拍内,不归零。更常用。

例如,某通信系统每秒传输1.5 * 10000 个比特,成为频率。其每位数据的时间(占用的时间,花费的时间……)为 1/(1.5*10000)。

7.占空比 q

占空比 q = 脉冲宽度 / 整个周期

从题目看,脉冲宽度取速度快的,因此取时间短的。

例如:周期数字波形高电平 6 ms ,低电平 10 ms。

解:波形脉冲宽度 = 6 ms (时间更短的)

周期 = 6+10 = 16 ms

占空比 q = 6 / 16 = 37.5%

8.时序图

数字电路中,常用时序图或者成为脉冲波形图,分析时序电路的逻辑功能。

9.进制

十进制、二进制。

中间省略逻辑代数

第三章 MOS逻辑门电路

按照器件结构不同,分为 NMOS,PMOS,CMOS三种。

砷化镓是继硅之后被发现的半导体材料。

1.输入、输出的高电平,低电平

这部分内容介绍,不同规格或者场景,高低电平的电压值会有差异。具体查书。

2.噪声容限

高电平容限 = 输出高min - 输入高min

低电平容限 = 输入低max - 输出低max

3.传输时延

4.MOS开关

MOS开关在数字电路中使用非常广泛,因为能完成出点开、关操作,速度和可靠性还比机械开关优越很多。

电流-电压图,有截止区和饱和区。该曲线越倾斜,说明电阻越小。

处于截止区,开关断开;处于可变电阻区,开关闭合。

特点,速度可能会慢。

5.CMOS反相器

由N沟道、P沟道两种 MOSFET 组成的电路称为互补 MOS 或 CMOS 电路。

要求输入的电源电压,要大于 N沟道和P沟道需求总和。

6.CMOS逻辑门电路

(A) 与非门

(B) 或非门

(C) 异或门

(D) 输入输出保护电路和缓冲电路

CMOS门电路输入端是MOS管的栅极,由于是很薄的 SiO,极易被击穿。因此,CMOS输入端,增加了二极管保护电路。

ShoelessCai 评注,就是二极管分流器,释放引脚静电荷,保护栅极绝缘层。

电路中有一个调节电阻,250欧姆左右。

7.CMOS 三态输出门、漏极开路门

第四章 组合逻辑电路

1.产生竞争冒险

所谓竞争冒险,即进行与或非基础逻辑门叠加的时候,由于有时间差,产生脉冲点。

其中,逻辑门的多个输入,同时正向、反向产生电流,如果"同时"受到挑战,即变化时间有差异,称为【竞争】。

因为竞争,可能产生干扰信号,称为【冒险】。

2.消去竞争冒险的方法

第一,发现竞争冒险,直接消去。

例如,F = (A + B)(A_ + C)=A *A_ + AC + A_*B + BC = AC + A_*B + BC

注意到,A*A_ 消去,只做器件时候,直接避免这类情况。

第二,增加乘积项,避免互补项增加。

例如,L = A*C + B*C_ ,这个电路在 A=1,B=1 的时候,有 L = C+C_

改成 L = A*C + B*C_ + AB ,不难发现,A=1,B=1 的时候,L = C+C_+1

此时,不会冒险。

第三,输出端并联电容器。

输出端并联滤波电容。

3.编码器

(A)定义:用二进制代替特定含义的信息,称为【编码】。具有编码功能的逻辑电路,成为【编码器】。

(B)原理。

普通编码器:4线-2线。简言之,输入端4个,输出端2个。输入 I0-I3,输出端 Y0-Y1;

优先编码器:普通译码器输入在输出的时候产生歧义,选择优先级高的。怎么确定优先级呢?主要看输入电平的顺序。例如,假设 I3 最后一个电平,如果输出产生冲突时候,先编码优先级高的。

4.集成电路编码器

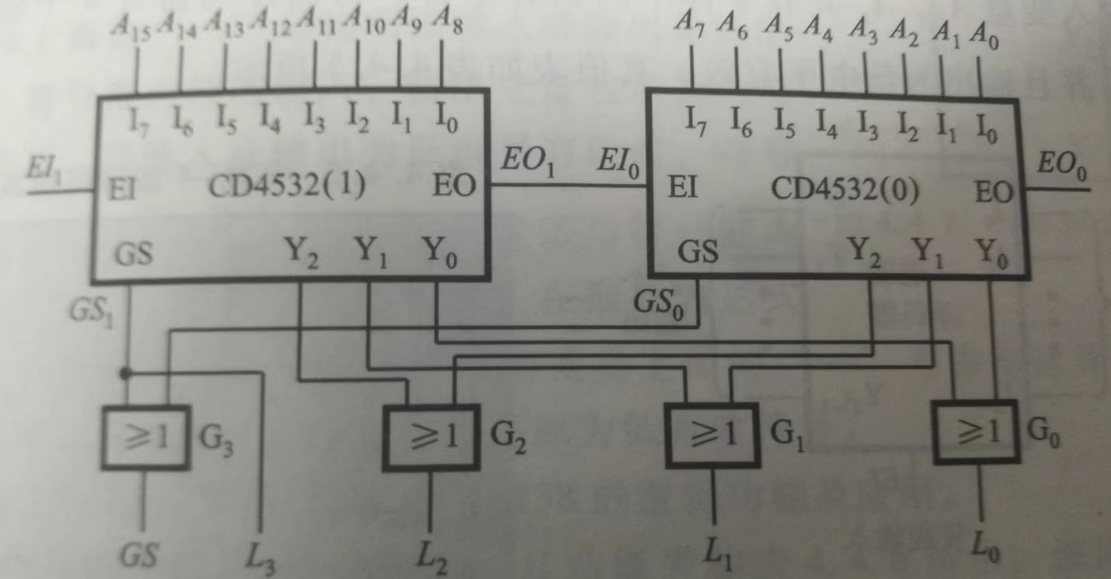

CMOS集成电路的优先编码器 CD4532 。8个信号输入端,3个输出端。这里注意译码器输入输出特点。

例如,16位输入优先编码器。A0端优先级别最低。

书上说,这类 TTL 已经不使用,如果我没理解错的话,就是这类电路不使用了。

5.译码器/数字分配器

(A)译码是编码的逆过程,功能是,将二进制转换成对应输出信号。具有译码功能的电路,称为译码器。分为两类(常用的两类):

第一,一系列代码都有一一对应的有效信号,称为【唯一地址译码器】,用于存储器单元地址的译码,即一个地址转成一个有效信号。

第二,将一种代码换成另一种代码。也称代码变换器。

关于唯一地址译码器

n个输入端,2^n 个输出端,1个使能输出端。

如果使能端为真,则只有一个输出端有效。

(B)集成电路译码器

二进制译码器,74138译码器,3-8译码器。

逻辑符号说明,注意低电平有效,此时输出端0有效,一个为0,其余为1。

(C)七段式显示器

通俗的讲,就是小时候暑假作业中,挪移火柴棒使得数字变化的那种。

(D)数据分配器

6.数据选择器

数据选择,经过选择,把多路数据中的某一段数据传送到公共数据线,实现数据选择功能的逻辑电路成为数据选择器。

相当于多个输入的单刀多掷开关。

7.集成电路数据选择器

常用集成电路有很多,有CMOS、TTL产品。 —— 这句话没太理解

关注 ShoelessCai.com 您值得关注。

浙公网安备 33010602011771号

浙公网安备 33010602011771号