Vivado 的电机控制

Vivado的FPGA创建电机控制:

设计流程:

FPGA的设计流程可以用盖房子的过程类比

代码实现,综合和布局布线时FPGA设计流程中的几个关键步骤:

代码实现:比如我要盖一座房子,我把房子的特点描述出来:比如面积100平米、带阳台、欧式装修风格、挑高3米、一室两厅一厨一卫、卧室木地板客厅瓷砖。。。等等要求,这个描述房屋特点的过程就好比我们用Verilog描述电路功能的过程。

逻辑综合:建筑师根据我们的要求画出施工图纸,施工图纸将我的需求数字化、具体化,比如这个墙有多高,门有多宽,窗户面积等等,这个过程就好比综合的过程,将房屋需求翻译成具体的数字化图纸,只不过综合是将电路功能翻译成门级网表,建筑师干的活就是综合工具软件干的活。

布局布线:工人拿会根据图纸(综合后网表),用砖、水泥、钢筋、木材等材料建造施工的过程就好比布局布线的过程。图纸规定了一面墙,但是没有规定具体用哪一块砖来砌墙,工人可以自主决定用哪些砖。布局布线是根据综合后的网表(施工图纸),利用FPGA芯片内部的可编程逻辑块(CLB),布线资源,时钟资源,存储资源等搭建电路的过程。

综合和布局布线的过程中会涉及到约束策略的问题,比如管脚约束、时钟约束、面积和速度优先级等。这些概念在盖房子的过程中也有对应,比如你可以跟建筑师要求阳台大小、卧室朝向、门窗高度等,采购建筑材料时,你也会控制成本和质量之间的平衡。这些都类似于综合和布局布线过程中的约束条件。

设计实现及分析(Implentation),对设计的逻辑和物理转换,Implentation setting :实现过程中的参数设置

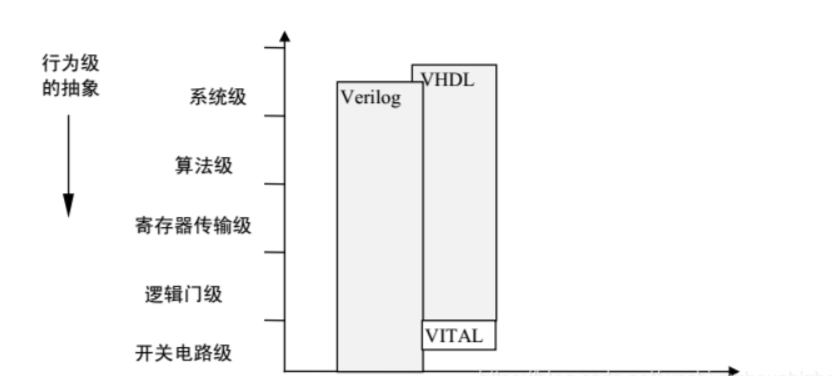

FPGA从上到下各个系统抽象模型依次为:系统级(System)———>>算法级(Alogrithem)————>>寄存器传输级(RTL)————>>逻辑级(Logic)———>>门级(Gate)———>>电路开关级(Switch)

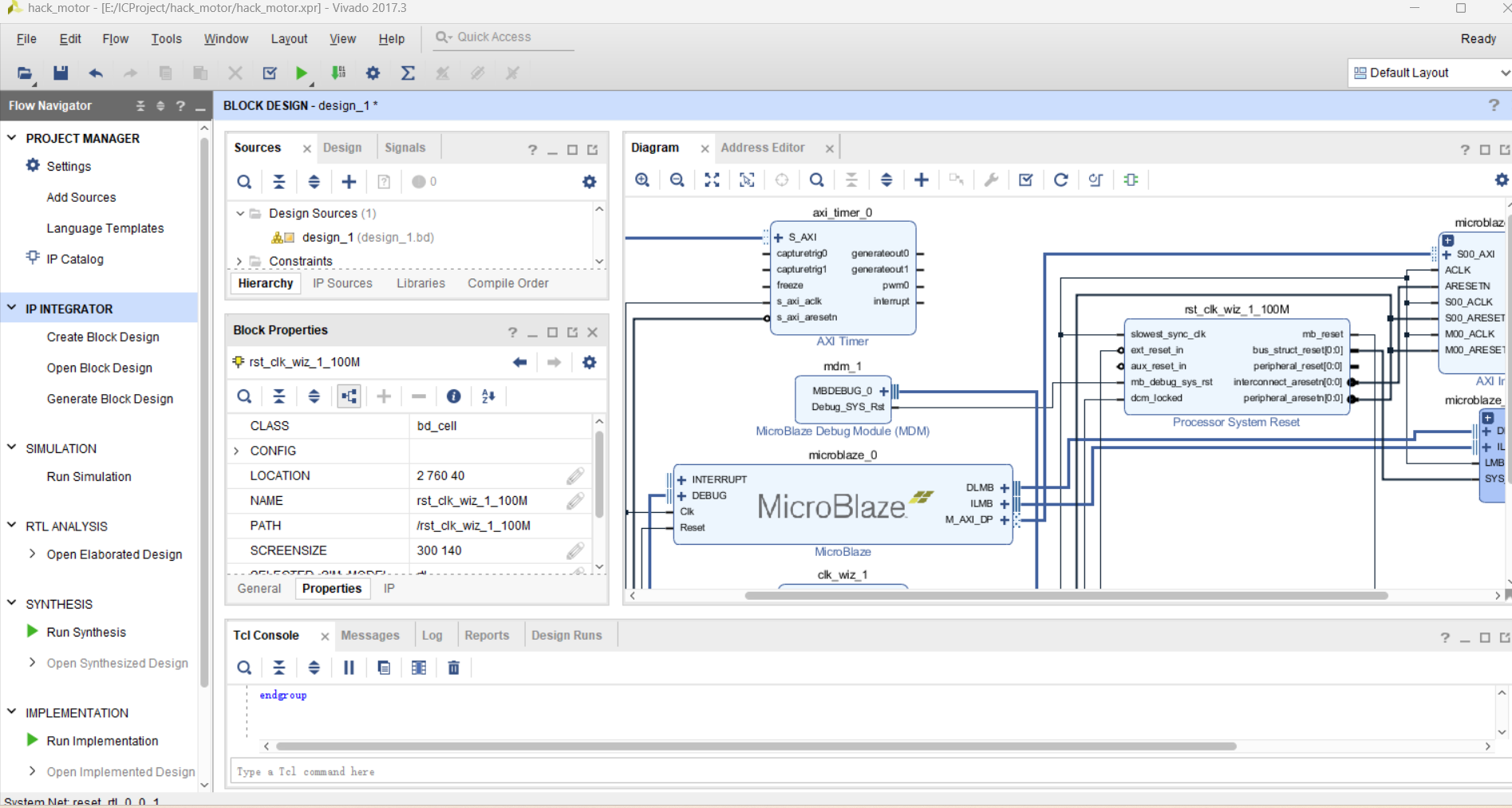

新建项目hack_motor,然后创建block design,最后添加 IP 库添加 MicroBlaze 处理器(运行块自动化连接,选择本地内存大小为32KB并取消选中中断控制器),AXI 定时器添加。

浙公网安备 33010602011771号

浙公网安备 33010602011771号