电流源与偏置电路(一)吴老师Bias电路review

又来返璞归真了.....今天是电流源笔记,基本就是吴金老师这篇基本Bias电流源电路的<Review:多支路偏置电路的静动态分析方法>的通读版本吧。

首先,想象一下我们现在需要一个电流源,怎么做,恒gm-current source吗?

由电阻和二极管或二极管连接MOS管组成的单支路bias电流源看起来比较简单能做出来,而且只要VDD略高于MOS管的阈值电压,这个电路就能工作起来,这说明这种电路可以在低压条件下使用。例如用电阻分压做一个bias出来:Vb=(R2/R1+R2)VDD,对吧,电阻按比例把layout做好,看起来P和T没什么问题,但是V的问题很大,电源变化几乎可以完全传输到输出,又比如电阻和二极管连接的MOS组成的简单bias,看起来输出是低阻的,然而电流源(VDD到Vout的路径上可能只有一个二极管)的电阻也不大,因此电源抑制也很差。但是,对于具有两个或多个耦合支路的自偏置结构,可以用高输出阻抗的恒流源来代替传统的线性电阻,这样变成高阻抗电流源与低阻抗二极管串联在单个支路中,主要的电源噪声可以降到电流源上,从而产生独立于V的稳定输出电流。所以我们排除了使用单支路的做法,至少这里得用二支路耦合起来自偏置吧。

由此产生今天的讨论:从二支路自偏置电流源到三支路再到多支路分析方法的小扩充

一、多支路自偏置电流源的静态分析

1、DeltaV/R型

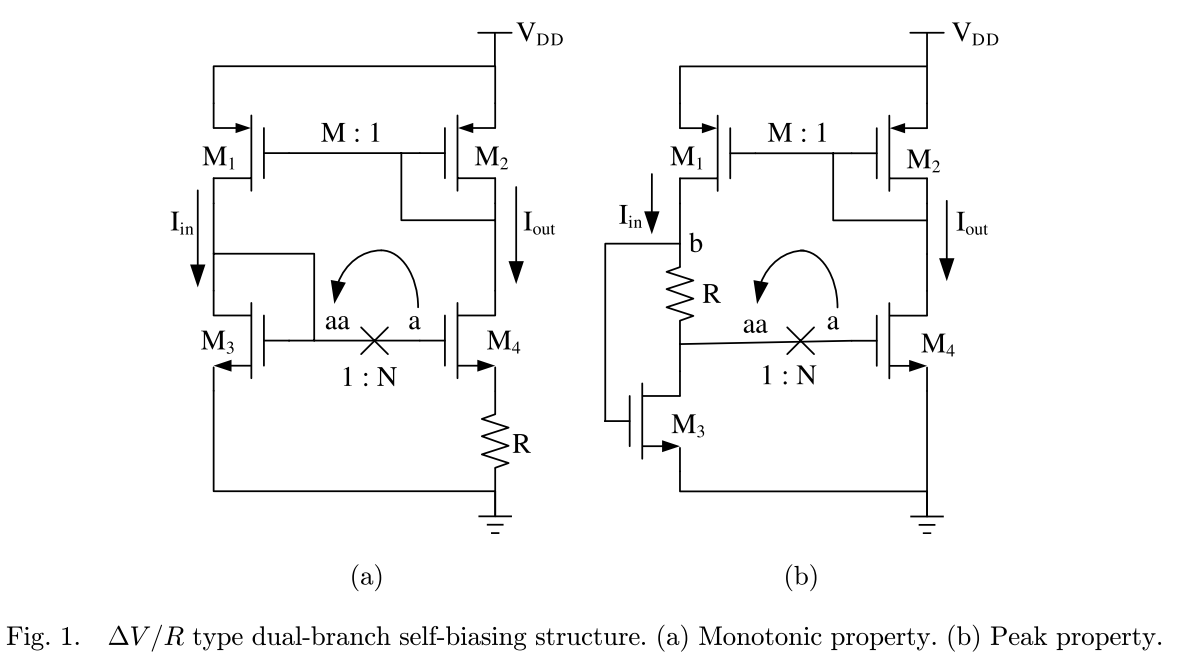

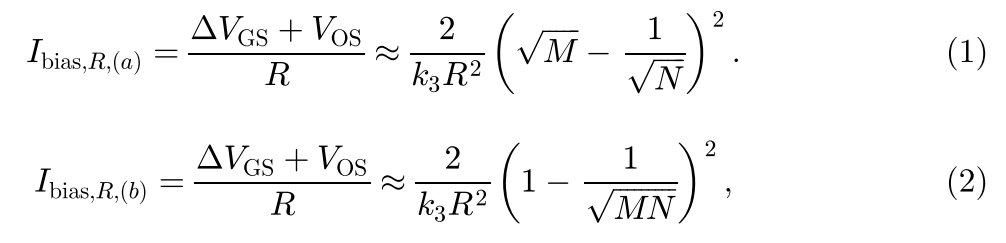

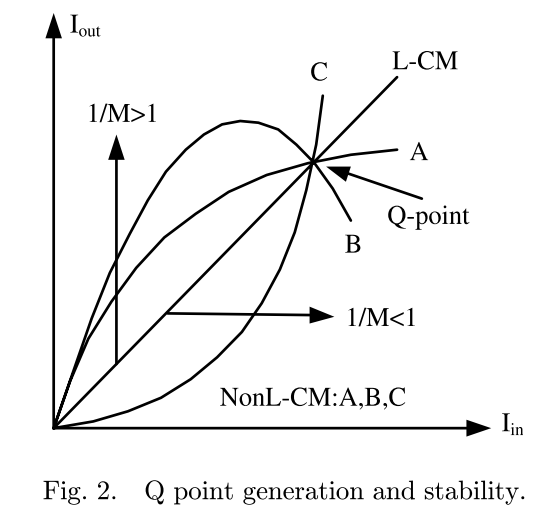

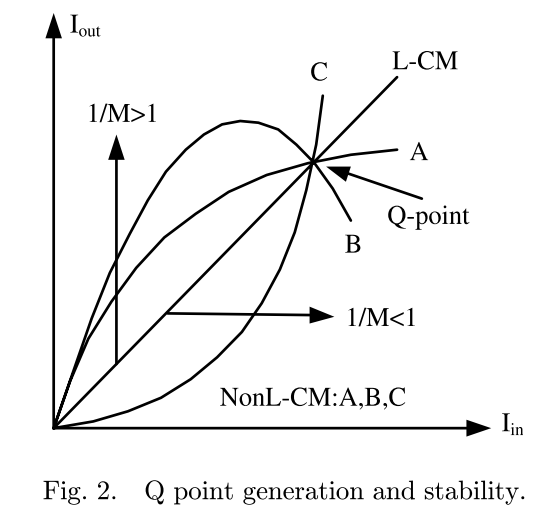

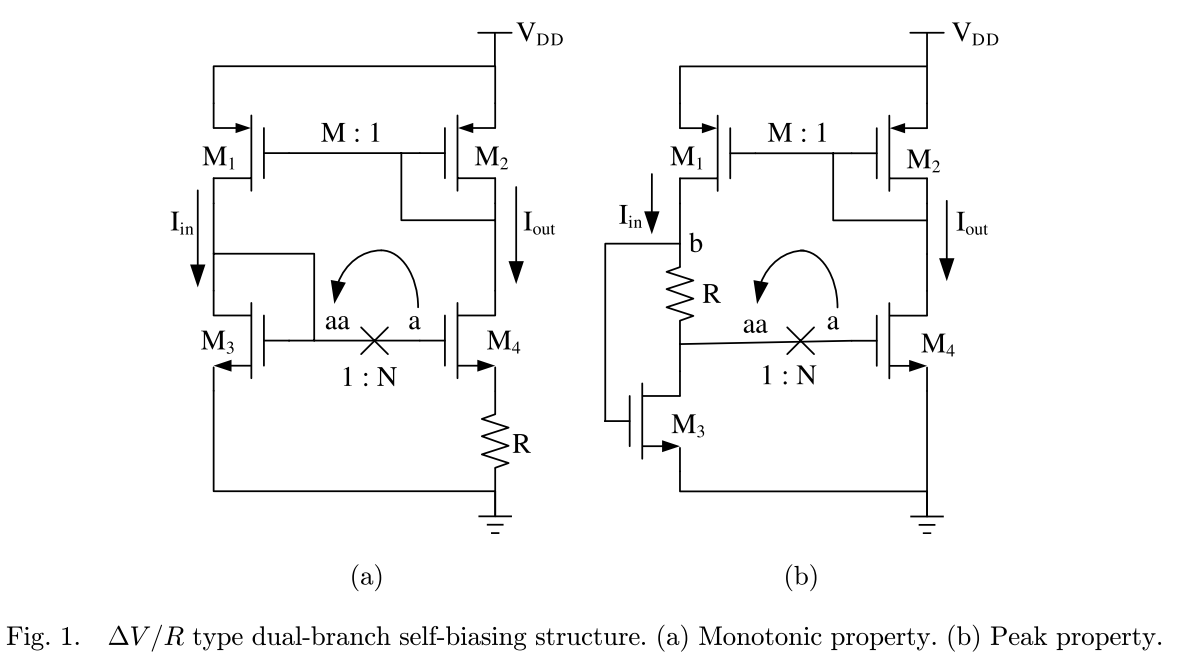

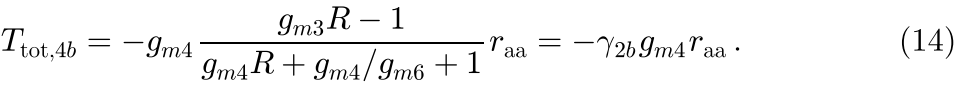

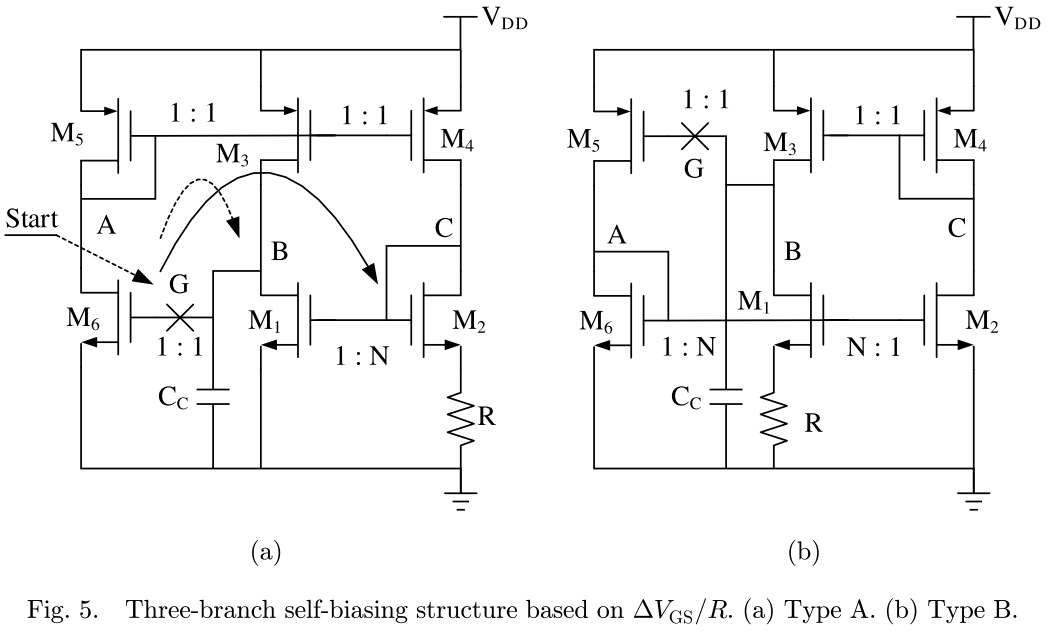

如图1所示,典型的V/R型双分支自偏置结构适合小静态电流产生。DeltaV的通常在几十毫伏的范围内,远远小于VGS或VBE,这里的R还可以是工作在三极管区下的无源电阻或有源电阻。在图1中,由传输比为M的P型CM传输电流,下面由电流检测电阻和比例为N的N管组成。如图2所示,这两条电流转移曲线的唯一交点Q为此自偏置电路的静态工作点。

(a)为单调型自偏置电流源,(b)为峰值型自偏置电流源

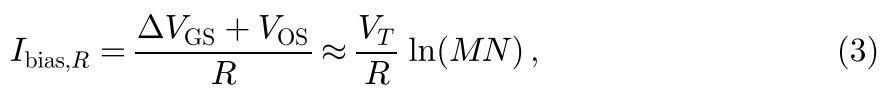

所有管子偏置在饱和区,假设管子总的vos很小,很容易算出:

(1)这里的解是Q点,当然手算一下实际上还有忽略了的零解(根号的时候)。另一个可以关注的点是,发现有些同学说他的N管region到了3,怎么办?其实可以简单想想,我们希望bias电流源的功耗足够低,因此很多时候都会将R取大又不愿倒比我们的N管,因此N管就很容易进入亚阈值区。进入亚阈值区会怎样?沟道电流从漂移变成了扩散,类似于bjt,所以此时的电流更多地类似于:

当然,你想要这样的效果就可以把亚阈NMOS换成npn,这就是CM钳位的PTAT电流源初步。

(2)这个电流源的系统误差在哪,最明显的是M3和M4的VDS不一致,Iout看起来是一定会小于Iin的。还有就是M3的阈值电压会比M4小,这是阈值电压失配。想改善这个系统误差,一个是反过来CM由NMOS给,这样PMOS用SB短接,消除掉阈值电压的系统失调,并且CM用cascode CM抵抗VDS差。随机失调只能靠大的管子了,但再怎么说这个电流源作为初学者去做也不会把面积做小就是了。可能大家第一次接触这个电路就知道他有个名字叫constant-gm电路,因为:

(3)这里需要再讨论一下这个电路的PVT。很多地方把(a)电路叫Widlar自偏置电流源。

我们都很熟悉的电流公式是:Iout = 2/kn(W/L) 1/Rs2 (1-1/sqrtK) 这里就这么简单打出来,当然我们因为太熟悉所以看起来也不难看。

首先要明确的是,这个电流公式是忽略了很多效应才得到的,一个是求出的零解,一个是NMOS的衬偏效应,一个是PMOS CM的CLM效应。看起来是完全与电源AVDD无关的电流,实际加入非理想效应可以算算S,算下来这个电流是完全与AVDD有关的,并且得出AVDD越大,产生的电流越大。另一个我们讨论他的温度特性,由于kn kp中的μn μp都是与温度成负相关的,大概写成μn∝T^-n,而μp∝T-(n+1),且Rs若使用poly-sab型,也是与温度成负相关。最终整体结果是T越大,产生的电流越大,而且把电阻翻上去,PMOS的SB短接消衬偏的那种形式的温度斜率理论上会稍微更大一些。(PTAT电流源,且仍受VDD影响较大)

(4)启动问题:

L-CM即上面P管的线性CM,NonL-CM即下面的N管的非线性CM。A为单调型自偏置电流源即constant-gm电路,B为峰值型自偏置电流源。

假设有N>1/M,即M4的电流密度>M3,类比于Banba基准要求产生DeltaVBE的BJT电流密度大一样的。在小输入电流区,非线性CM曲线都位于线性CM曲线的上方,这表明Q的唯一交点可以确定地形成,确定输出电流。对于(a),我们都知道,最简单的启动方案就是gate-gate之间插入二极管形成电源到地的通路。

2、复杂非线性CM的电流源

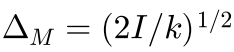

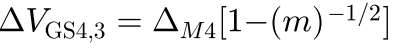

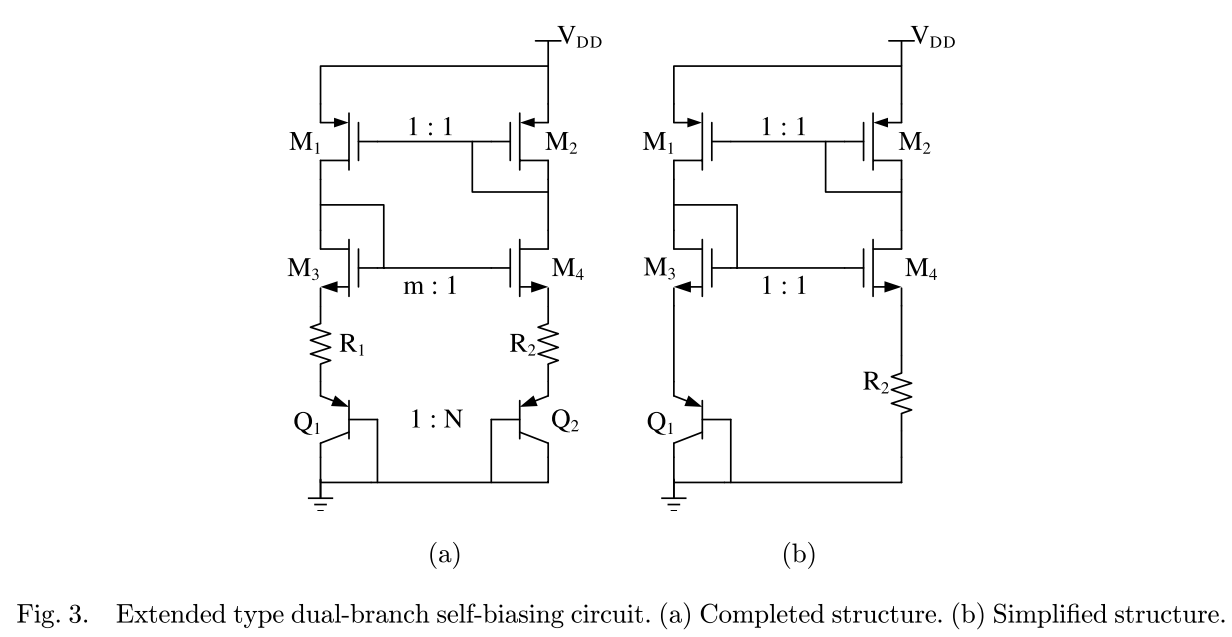

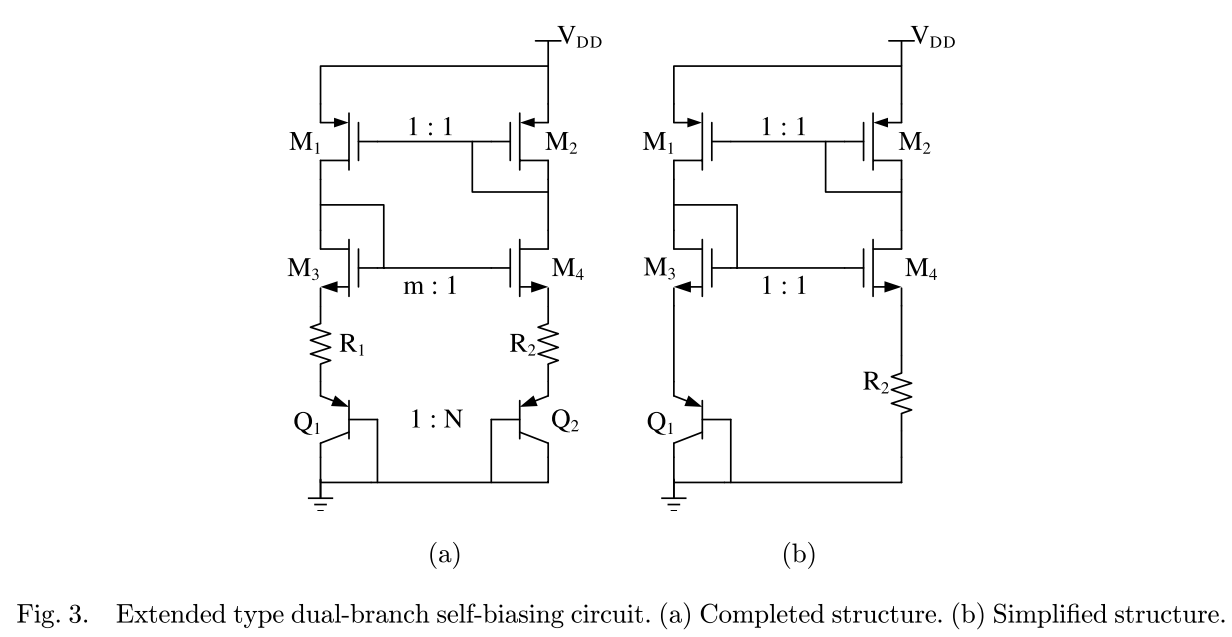

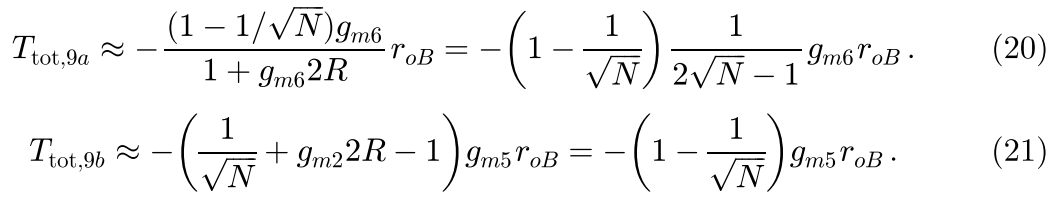

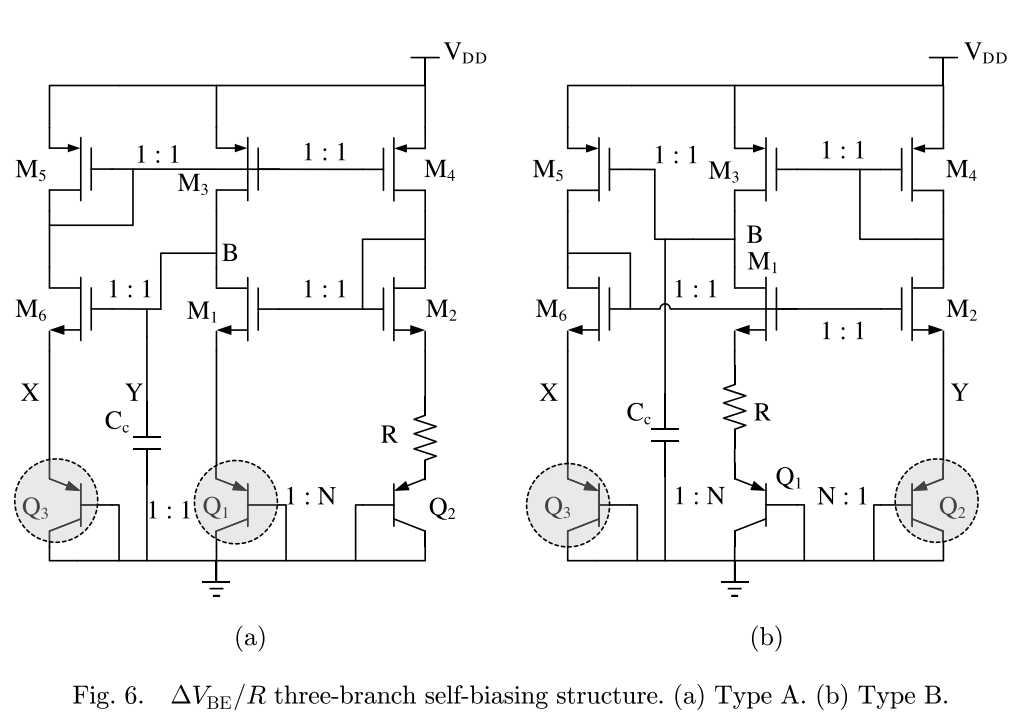

这里的“复杂”的意思是DeltaV1+DeltaV2/R的意思,刚才在1中只看了最简单的DeltaV/R即DeltaVGS/R型电流源,这里作扩充。首先,掌握CMOS工艺中的横/纵向bjt的剖面图、特点、要求是基本知识,不写了。吴老师意思是,接下来要用pnp了。这里给到一个带PNP管的Ibias产生电路的实例。为了功耗和电流的match好点,Pmos的CM用的1:1,M3和M4的NMOS对用m:1,m>1。M4的过驱动电压为

则M4的过驱动电压会比M3高

假设Vth一致,这就是VGS之差。

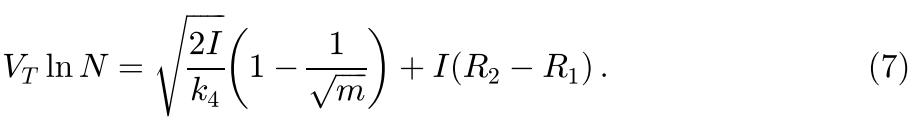

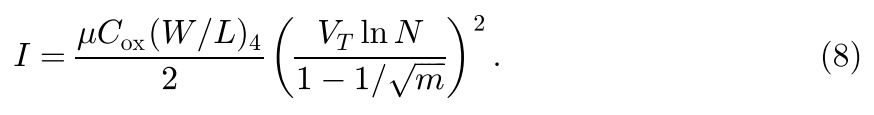

因此,R1上端电压比R2高一个Delta过驱动电压。又由于下面PNP管取1:N,因此,VQ1比VQ2高一个VTlnN。完整写成:

VEB1+IR1+VGS3=VEB2+IR2+VGS4——>VEB1-VEB2=I(R2-R1)+VGS4-VGS3——>VTlnN=I(R2-R1)+DeltaVGS4,3

当m=1且R2>R1时,即右边第一项为0,产生的电流I就是一个很好的基于DeltaVBE的PTAT电流。(BJT作用)

当N=1且R1>R2时,即左边项为0,产生的电流就是一个基于DeltaVGS的电流。

当N>1且m>1且R1=R2时,即右边第二项为0,相当于Q1增加的V被M3减小的V补充,因而产生的电流由DeltaVBE和DeltaVGS共同决定:

由于μ正比于T的-3/2次方(虽然我一直记得是un正比于-1次方,up正比于-2次方),VT正比于1次方,因而产生的电流正比于T的1/2次方,即根号关系。这看起来没什么意思,但是如果我们故意去增加一下R的量,例如公式右边第三项使其不为0,取个R2,另R1=0,那么我们就可以微调TC,这就十分有意思了。

当我们取N=8时,VTlnN=54mV,那么右边第一项就不能超过这个54mV(还要考虑到给第二项让一点空间)。首先m不能太大,太大了M3在corner下容易进入亚阈值,但是m如果太小,产生的电流就会增大,当我们想要Bias电路电流消耗不是很大时这里就是问题。一般,N=8时的trade-off大概是让m取到1~2中间,例如1.5。

失配:看起来会比图1的电流源对失配引起的mismatch来说大一些。

当我们去掉R1和Q2或者R2和Q1时,就会得到图3(b)的电路,这电路看起来简单一些,就是VBE/R类型的电流源,很像最开始说的constant-gm电流源。这里的问题是,去掉R1和Q2和去掉R2和Q1会得到两个不同的电路,哪个是对的呢(也属于鸿爷课上的经典问题)。答案就是图(b),原因是BJT的交流小信号电阻很小,比R小得多,而整个的正反馈环路需要有个电阻去degeneration一下M4管子的gm使Loop Gain得到进一步降低。例如图(b)的正反馈环路增益大约为:gm1 (1/gm3+RQ) gm4/(1+gm4R2) /gm2=(1/gm3+RQ)(1/R2)<<1。反之可以简单推一下另一种情况大概是R2/RQ的增益,这甚至>1,电路根本无法建立。

3、V/R型

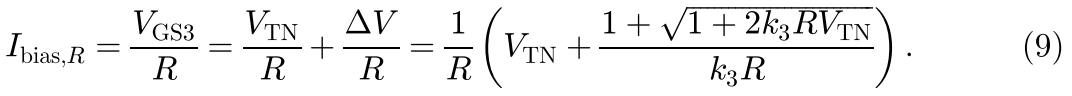

这种VGS或者VBE电压直接落在电阻上by real or virtual short的结构就是V/R-type的电流源。由于V>>DeltaV,因此这种结构很适合做大一点的电流源,例如图3(b)

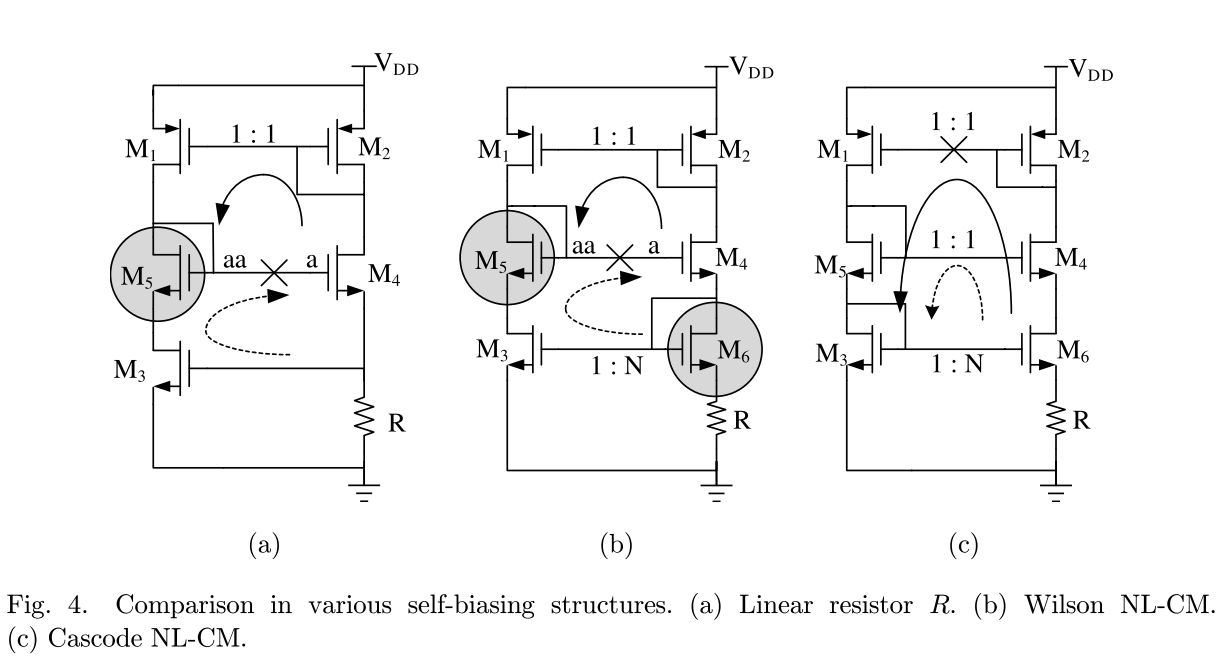

图3(b)就是一种virtual short形成的V/R电流源,这种电流源很依赖virtual的ideal。还有一种就是直接物理上的real shorted形成的V/R电流源,例如图4(a)

观察输出电流公式(9),最小输出电流为VTN/R,这完全独立于输入电压,VOV<<VTH,因此输出电流大小差不多也就那样。

V/R-type也可以变成DeltaV/R-type,就像上面DeltaV/R-type可以通过删除Device来变成V/R-type一样。图4(b)增加了M6,提供不同的比例增加DeltaV,这个电路的反馈回路和图1的constant-gm电流源不一样,因此电阻R的位置也是不一样的。

由于系统的限制,静态分析方法很难用于电路重构。对于同一静态点,某些变化的结构不可能是稳定的。对于图4(b),通过去除M4和M5并改变PMOS线性CM的输入输出方向而改变的电路是不稳定的。同样对于图3,类似于VBE1=R2产生的VBE2=R1型改变的电路是不稳定的。因此,为了区分这些相似的电路或进行有效的优化,动态特性分析方法是非常必要的。

二、电压域/电流域的环路分析方法

对于没有任何外部信号注入的自偏置电路,由耦合支路形成的反馈环可能是稳定的,也可能是不稳定的。因此,可以通过反馈回路的信号响应来直接评估自偏置电路的稳定性。

1、电流域的Neff分析方法

众所周知,系统的稳定性与反馈回路的极性密切相关。然而,对于多极电路,如果信号频率变化很大,系统的极性可以在负极和正极之间移动。因此,对于闭环系统结构,在任何情况下都必须有足够的相位裕度(PM)和增益裕度(GM)来维持系统的稳定性。

小信号环路增益的电流域分析方法特别适用于二分支自偏置结构。图2所示的双支路电路的直流电流转移曲线可用于在特定的直流点以切线斜率提取相应的交流电流增益。对于非线性电流传递曲线,交流电流增益Neff随直流工作点的移位而连续变化。当输入电流极小时,非线性CM变为增益因子为n的线性CM(类似于mos管线性区的近似方法),而对于线性电流传递曲线,斜率或交流电流增益总是恒定的,等于电流传递比M。最后,将两条CM曲线在静态工作点的切线斜率的乘积确定为反馈回路的交流电流增益。

L-CM即上面P管的线性CM,NonL-CM即下面的N管的非线性CM。A为单调型自偏置电流 源即constant-gm电路,B为峰值型自偏置电流源。

这种通过分析交流电流增益来判断环路稳定性的方法,可以通过举例来验证:定义Ti,loop=MNeff为环路电流交流增益。

图1(a)说了是单调型的电流源,当N>1/M时,曲线A在小电流区的斜率Neff=N比线性CM的斜率大很多对吧,当然这个斜率N会随着电流的增大而减小,因此如图2所示可能会相交于点Q,且Neff<<1/M,于是有Ti,loop=MNeff<<1,环路的GM就是满足的。显然,由于电流环始终是正反馈的,并且,在超小电流区附近的环路增益最大值远大于1,因此该电路的稳定性会被一个比较大的M退化。该电路容易启动。 (理解为在小电流区T>>1使得电路启动,当电流增加起来之后T<1保证稳定性) 实际上,对于具有可靠启动电路的自偏置结构,利用启动电路提供的外部暂态电流迫使环路从原点(零)到静态点Q,从而获得并维持稳定的静态运行状态。

对于图2中具有峰值输出电流的非线性曲线B,交点可以位于该峰值位置的前面或后面。随着输入电流的增加,电阻器R两端的压降不断增大。在小输入电流区,电阻两端的压降可以忽略不计。输出晶体管M4的栅极电压增加,因此输出电流也将增加。在大电流区,M3的栅压被VGS钳位,且随着输入电流的增大,电阻R上的压降增大。因此,M4的栅极电压降低,导致输出电流降低。最大输出电流时的斜率为零,环路增益的极性由小电流区的正极移至大电流区的负极。如图2所示,对于较大的M和R,曲线B将与峰值后面的直线CM曲线相交。此时,负回路增益可能大于1。稳定性得到改善,启动机制类似于图1(a)。

电路的稳定性与电路结构和关键器件的尺寸密切相关。特别是,作为电流检测器的电阻R的位置不是自由的。在图1(a)中,如果将电阻移到M3的源处,并且M3和M4的W/L比变成N:1,非线性曲线将从A移动到位于线性CM曲线下方的C。如图2所示,Q点处的正反馈环路增益可能会超过1,而小电流区的环路增益远小于1,因此改变后的结构永远不会启动到静态点,也很难在Q点处停留或固定。

电流回路分析方法有助于对物理的理解。然而,对于非线性CM电路,特别是对三支路电路的分析,推导小信号增益的方法相对复杂。幸运的是,可以用更方便的电压环分析方法来代替,电压环或电流环模型得到的结论完全相同。实际上,对于具有单反馈回路的双分支电路,电压环增益完全等于电流环增益。因此提出下一种更简单清晰的分析方法:

2、电压域的Tloop分析方法

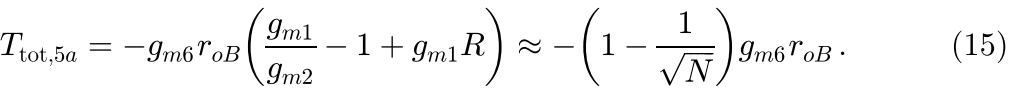

(1)依旧是看图1的constant-gm电流源的例子:

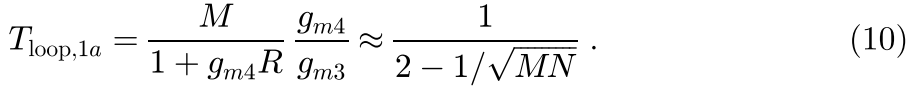

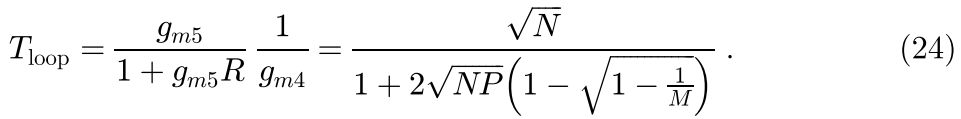

整个环路增益就是两级CS放大器,由于R的degeneration使得整个环路增益很小,这个很好推:

当MN>>1时,Tloop<<1,最小的Tloop极限为0.5,因此这种GM并不是很小的电路稳定性是相对比较差的。

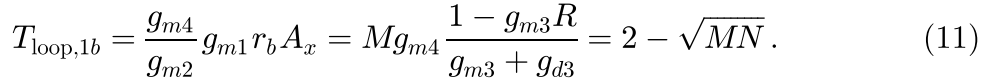

(2)图1(b)的峰值电流源也容易分析,画小信号易得到b点处的交流电阻为Rb=(R+ro3)/(1+gm3ro3),因此传到aa处的电压Vaa=Vin-(Vin/Rb)R,从b到aa的电压增益很容易推出来为(1-gmR)/(1-R/ro3),总的Tloop也很好算:

若R=0,电路退化为循环的电流镜而已,若R=1/gm3,则Tloop=0。

因此这个电路的Tloop会随着R的变化而变化,从正反馈变为负反馈。很小的R带来整反馈,很大的R,至少大于1/gm3即MN>4,带来负反馈,1/gm3是界限。这个电路的稳定性就很容易设计得比constant-gm电路的好很多。

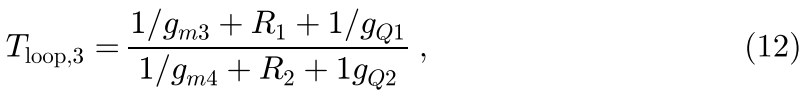

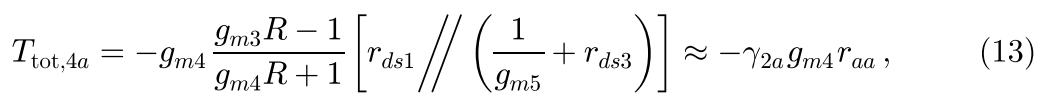

(3)图3的V/R-type和DeltaV/R混合型电路也能分析一下:

非常简单:

gQ=I/VT,且这个值只受电流和温度决定,BE结面积与这无关。而gm要与电流和管子尺寸有关。假设支路电流均衡,则gQ1=gQ2,gm3/gm4=sqrt m。因此,当m>1且N>1时,即1/gm3<1/gm4,若取R1<R2总是能满足T<1的稳定条件,这与上述的讨论结果一致(最极限的就是直接把R1去掉)

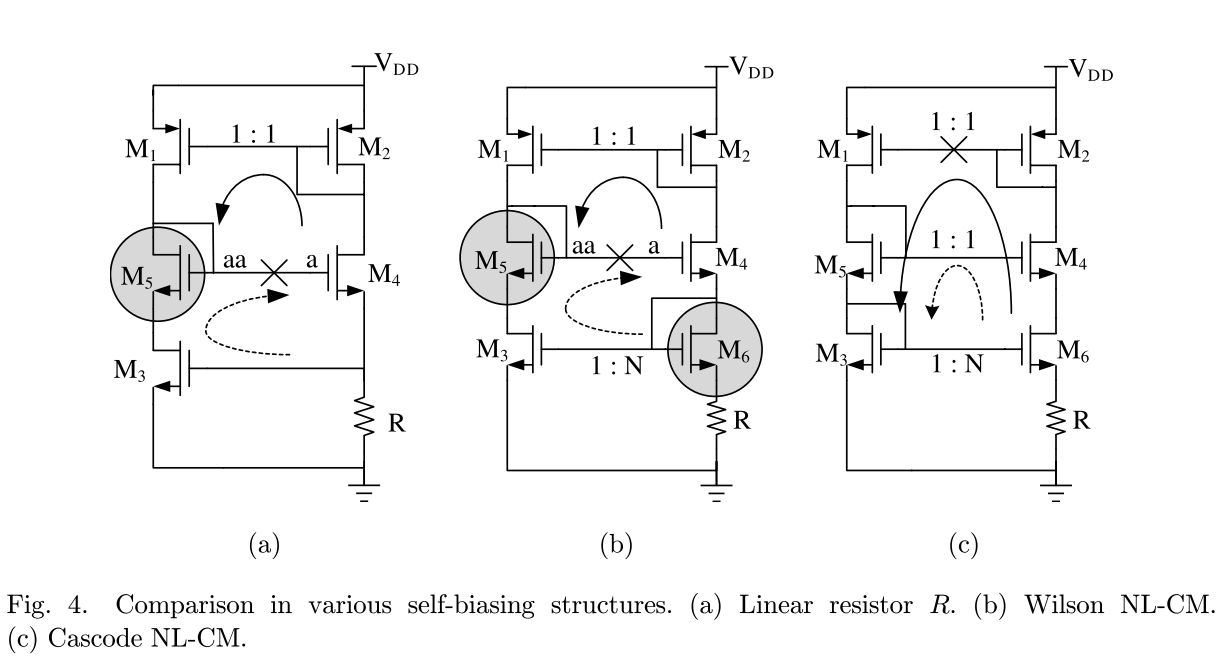

环路的断点应选择在增益级的信号路径可以闭合的位置。对于具有共享元件的多回路电路,通常选择由不同回路共享的节点作为断点。因此,可以很容易地处理耦合环路增益的线性叠加。如图4所示,选择M4的栅极(Aa/a)作为两个耦合回路的断点。上环是由两个CS级构成的正反馈环,下环是由源随器(CD)级和单个CS级组成的负反馈环。除了M4和M5的共享分量外,一个环路中的器件可以通过负载效应而改变另一个环路的增益。如图4(a)所示,在底部环路中,电阻器R作为源极跟随器工作。但它实际上会使上环中M4的跨导退化。因此,负反馈比正反馈更强。(说明分析两个环都需要全部元件一起考虑到)。整体环路增益为上环下环的叠加

raa为节点aa的阻抗,这非常高阻,由M1和M3的rout决定到。gmR=2VGS3/R>>1。若M3和M4完全相同,则r2a=1约。

图(b)同样可以得到:

由于r2a>r2b,因此图(a)比图(b)的稳定性高很多。图4(b)中电阻R的位置与图1(a)中的位置不同的原因是,与二极管连接的M6的源极相连的R可以保持其负回路增益。然而,图1(a)R的位置,R与放大器晶体管M4的源极连接可以显著降低其正环增益。

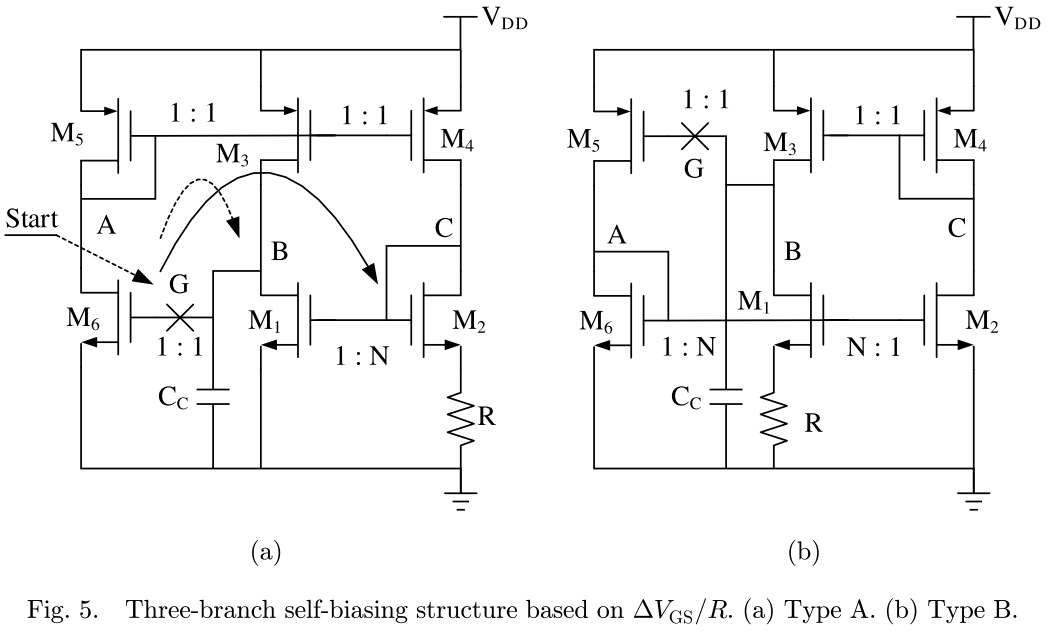

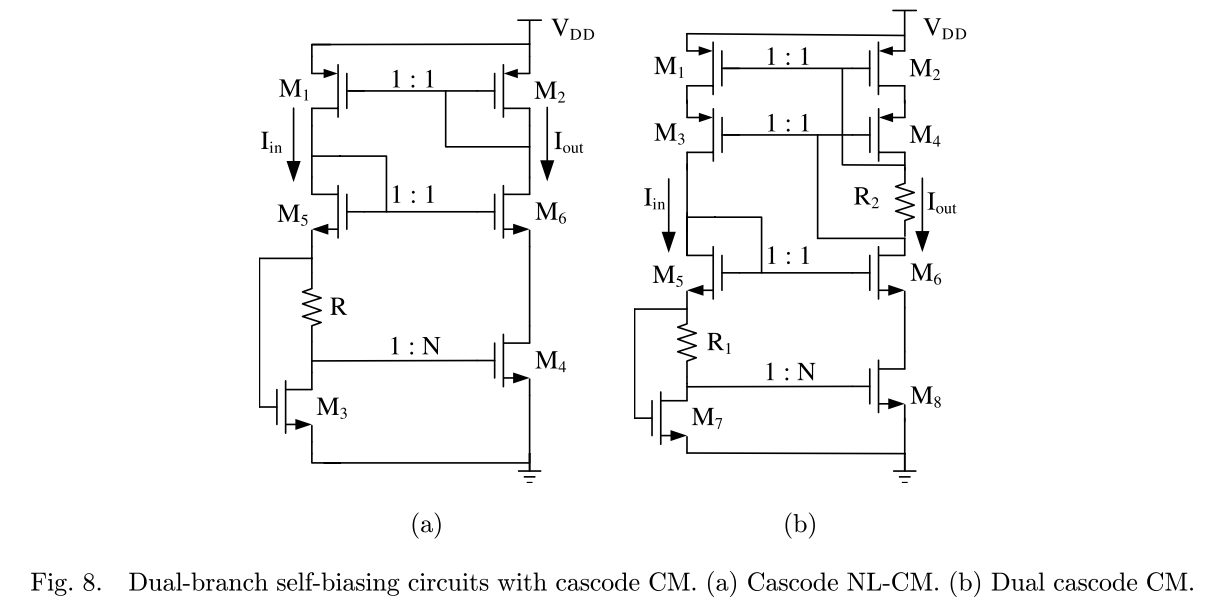

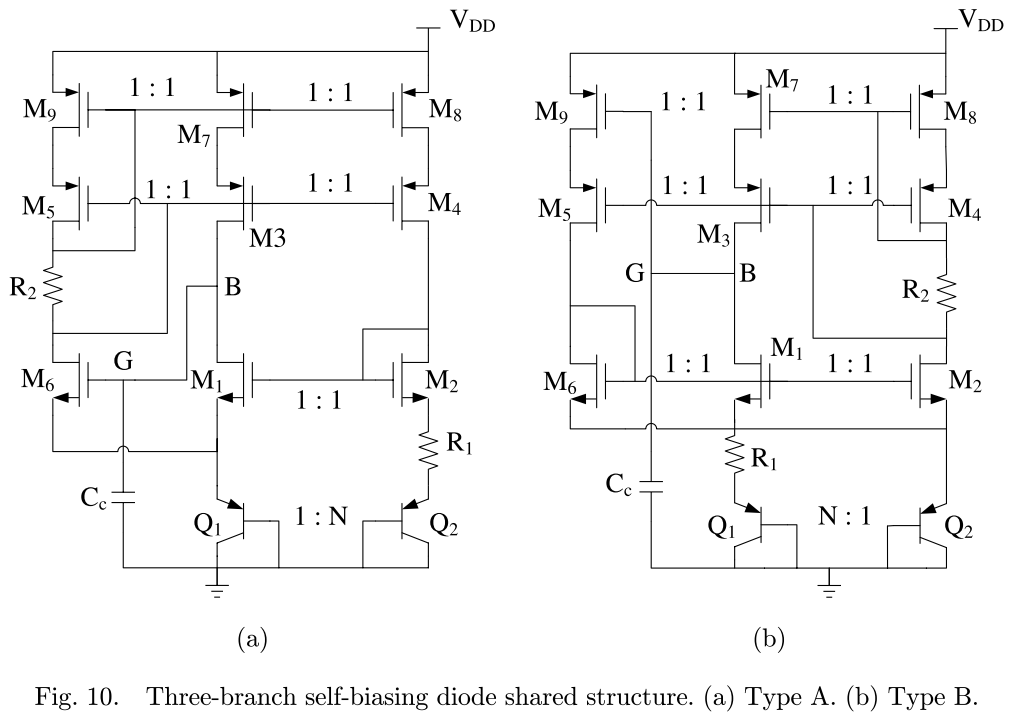

3、电压域方法分析三支路电流源

在不改变输出静态电流的情况下,通过引入高阻抗支路,将V/R型双支路自偏置电路扩展为三支路结构。如图5所示,电路中有两个cascade级联环路。通常,输出阻抗高的支路由两个局部环路共享,剩余的CS支路位于局部负环内。由于MOS二极管的低输出阻抗,两个CS级的电压增益都很小,并且通过高输出阻抗支路的信号路径对于两个局部反馈环路是互补的。

正环和负环的电压增益分别记为Ap和An,总的Tloop=An+Ap。

先看图(a),从高阻点G处断环,小环路是M6的CS+M3的CS组成的正环路Ap,大环路是M6的CS+M4的CS+M1的CS组成的负环路An。算起来:

简单分析就是:M1的CS的高增益级以及M6的二极管连接CS被两个环路共用,负环路多的另一部分为M4组成的CS,由于R的存在使其增益>1,于是这个电路就能稳定。

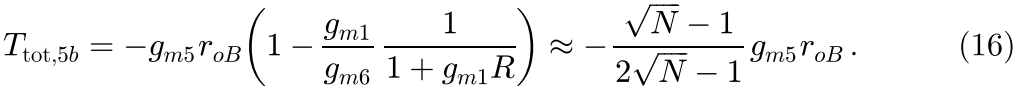

再看图(b),同样的,在唯一的高阻点G处断环,小环路是M5的CS+M1的CS的正环路Ap,大环路是M5的CS+M2的CS+M3的CS的负环路An:

如上所述,电阻的位置对系统的稳定性至关重要。M4支路的增益约为1,并且不对称的高阻抗支路对两个环路的不同增益有贡献。在正反馈通道中,M1被用作放大器,源极电阻R引起的跨导退化将导致环路增益的降低。在负反馈通道中,使用M3作为放大器,而电阻R可以适当放大输出阻抗。因此,可以获得整个系统的净负反馈。环路增益可以通过减小静态电流来增加,这有利于提高稳定性。

对于相同的N(N>1),图5(a)的总环路增益比图5(b)的略大,表明在相同的工作条件下,图5(a)的环路增益更稳定。 对于三支路自偏置电路,低频下的主导极点位于高阻抗输出的节点B。另外两个高频次级极分别由两个MOS二极管组成。为了实现可靠的PM,使用位于节点B的电容来有效地减小反馈环路的GBW,导致所有二次极点被推到远离环路带宽的位置。

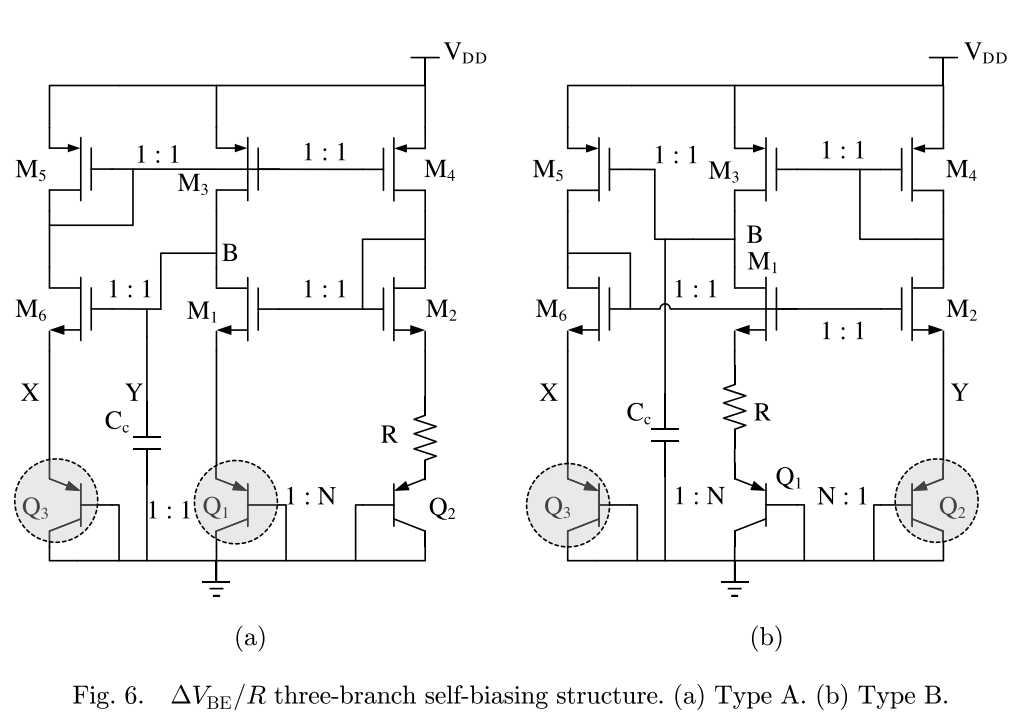

另外,图(6)给出两种DeltaVBE/R电路的三支路结构:

三支路自偏置结构的暂态特性一般好于双支路自偏置结构。此外,与两支路自偏置电路相比,电压匹配性能有了显著的改善,offset明显降低。

当然这里有个问题是,三支路电路在小电流时具有较弱的负反馈特性,使得他比二支路结构更难启动。

四、Bias电流源进阶例子

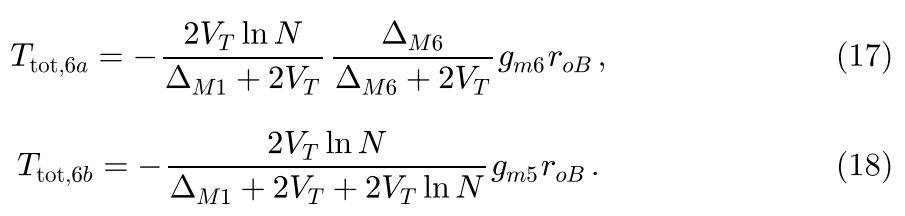

1、使用线性cascode CM

普通的线性CM由于VDS的mismatch,电流匹配性较差。如果用共源共栅电路,电流匹配性能将得到显著改善。如图7所示,PMOS线性CM由宽摆幅共源共栅结构构成。由于共源共源共栅结构的输出阻抗显著提升,静态电流检测的精度和电源抑制比能力都得到了提高。然而,由于MOS二极管的低阻抗包含在每个支路中,因此环路电压增益几乎不变。共源共栅晶体管引入的第二个正反馈回路相对较弱,通常情况下可以忽略不计。因此,在回路分析中,共源共栅CM可以被视为一个整体,就像传统的线性CM一样。环路增益(10)和(11)对于图7所示的共源共栅自偏置电路仍然没变。

这就是图(1)中的PMOS CM改了一下。

在图7(a)中,使用辅助电阻RB来偏置共源共栅晶体管。由于RB上可能的电压降被限制在Delta~VTP的范围内,所以最小电源电压略有增加。在图7(b)中,使用附加支路来偏置共源共栅晶体管,增加了总电流消耗。

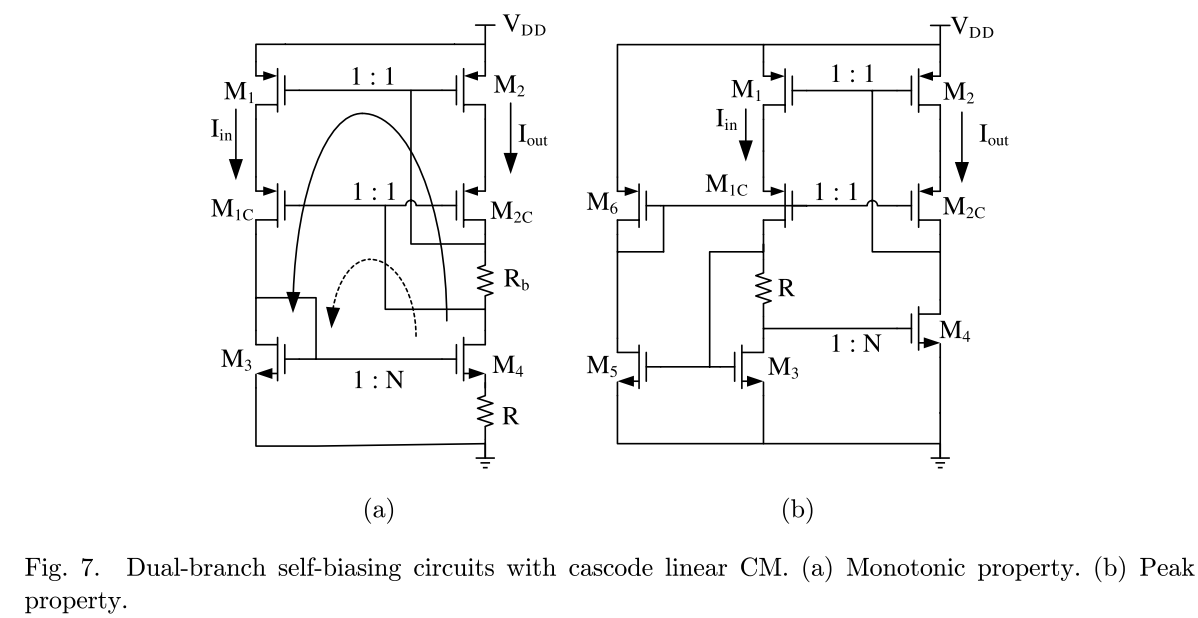

类似地,NMOS非线性CM也可以扩展到共源共栅结构。如图8所示,采用具有两个相同的NMOS晶体管M5和M4的电压镜来构成N型非线性共源共栅电路。与图7所示的电路相比,环路增益和电源抑制比特性保持不变,但电流匹配特性和最小电源电压略有退化。

2、电路元件共享的方案

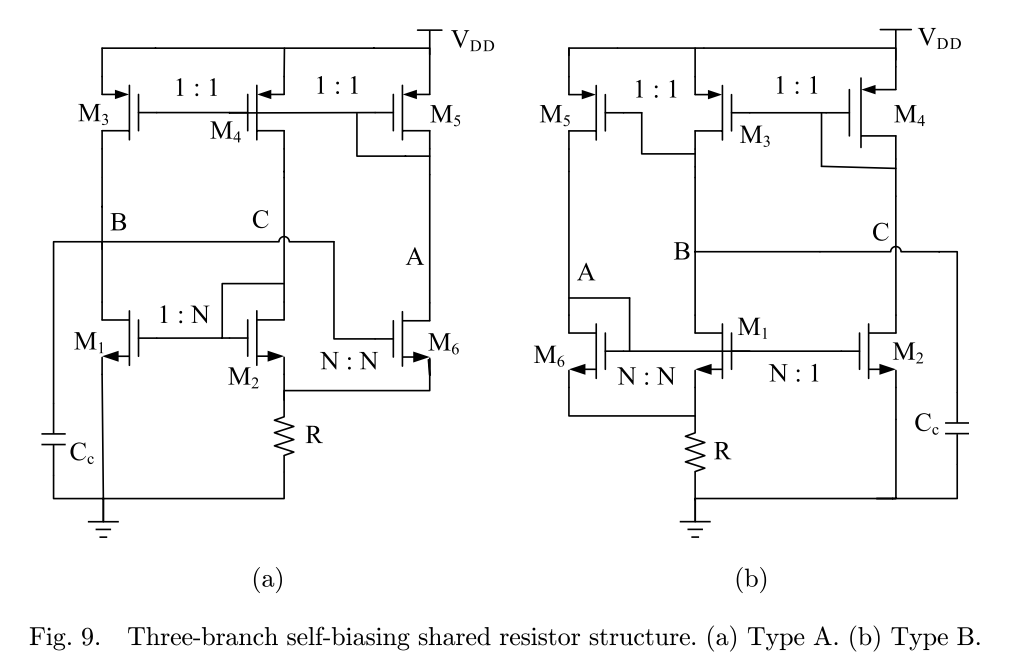

在多支路自偏置结构中,电流检测电阻可以由两个支路共享,以节省面积。如图5所示,如果两个共享支路中的电流相同,则可以将电阻R减半以保持输出电流不变。修改后的电路如图9所示,电流匹配的性质与M6的大小密切相关。

在图9(b)中,M6和M1的W/L必须相同,才能设置相同的支路电流。但在图9(a)中,为了节约面积,M6的W/L可以小于M2。通过VB电位的自调节,两支共用支路的电流仍可大致相等。总的来说,图9(b)的电路在电流匹配性能上优于图9(a)的电路。

通过将两个分离支路的共享电阻加倍,可以利用decoupling analysis方法。如果每条支路的电流几乎相同,类似于(15)和(16)的环路增益可以写出来:

如上述方程所预测的,两个电路的环路增益在相同的范围内。事实上,共享结构中存在额外的信号路径,并且共享结构的实际动态特性可能与decoupling analysis方法预测的结果略有不同。

在图6中,在相同电流的情况下,两个大小相同的双极型晶体管的发射极电压几乎相同。因此,这两个虚拟短路节点可以物理连接,而此时并联起来的的两个晶体管可以看作是一个具有双发射极面积的晶体管。与原电路相比,改变后的电路动态特性变化可以忽略不计。为了节省面积,共用晶体管的发射极面积可以按比例减半到1(就是咱也别2了,就还是1吧)。然后,用于产生VBE的两个不同晶体管的有效面积比也从N:1增加到2N:1。在保持电阻R不变的情况下,静态电流略有增加,offset电压也有所降低。图10中给出了这样思路的升级版,还把上面NMOS的CM改成了Cas的。偏置电流和环路增益与图6中的电路相似,在这种情况下,只需将公式中的比例N加倍为2N即可。

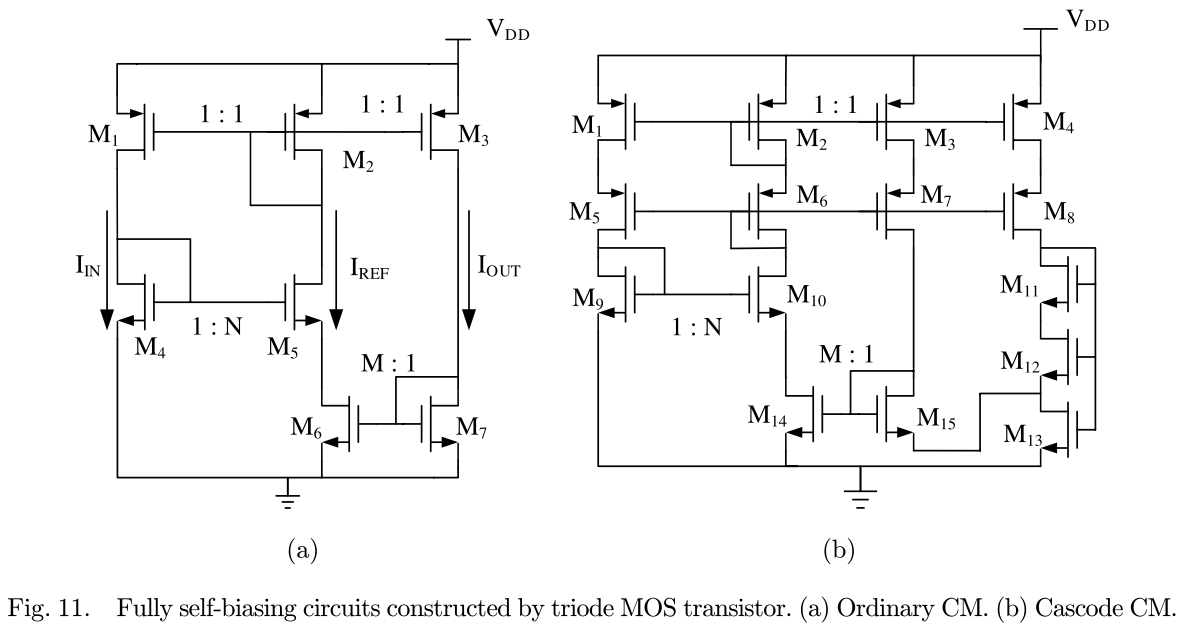

3、全MOSFET的自偏置电流源

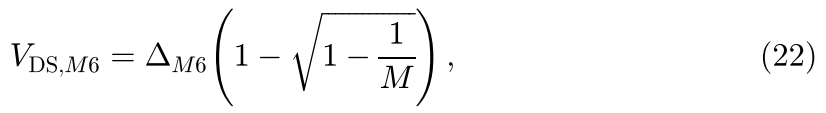

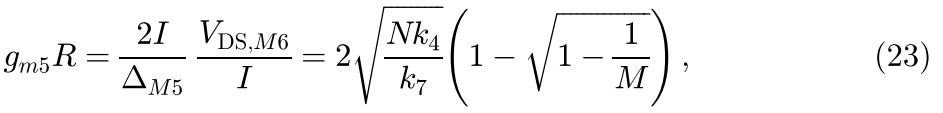

为了节省面积和限制过大的变化,自偏置电路中的线性电阻R可以用深线性区偏置MOS晶体管代替。通常,三极管NMOS晶体管的栅极可以由电源VDD等大电压驱动,也可以由输入电流很大很固定的CM驱动。通过这种方式,三极管MOSFET可以被确定地工作在深线性区,并且等效的线性电阻Ron基本上是固定大小的。因此,该电路的性能可以与图1(a)的constant-gm源完全相同。另一种偏置三极管MOSFET的方法是通过电路的内部电流或电压,如图11所示。假设M6和M7之间的尺寸比M远大于1,且所有支路电流几乎相同,则图11(a)中的晶体管M6将在三极管区下工作,M6的VDS可由下式给出:

若M>>1,VDS,M6<<DeltaM6,那就进入线性区,我们很容易算出来这个电路产生的参考电流的大小。

在图11(a)中,偏置三极管MOSFET的栅极电压来自内部电路,因此三极管线性电阻取决于支路电流水平。然后,该电阻又定义支路电流。在瞬态过程中,由于支路电流一直在变化,所以电阻不断变化,直到电流变得恒定。输出电流可根据nMOS晶体管的大小进行调节,大的N、M和小的(W/L,M7)有利于产生大的输出电流。由于电路中的非理想因素在支路电流中起着重要的作用,因此唯一的静态输出电流很难明确地表示出来。但是,gm5R可以表示为:

所以好像依旧是constant-gm实现了。

假设W/L,M4/W/L,M7=P,由于辅助正环偏置三极管M6非常弱并且可以忽略,所以由两个原始主导支路确定的环路增益可以由下式写入

显然,较小的M和较大的P较好地改善了系统在某个N下的稳定性,此外,看起来这个电路是非常容易受到mismatch的影响的。

在图11(b)中,采用共源共栅结构来增强所有PMOS线性CMS的电流匹配,从而消除了系统mismatch对支路电流的影响,提高了电源抑制比。与复合MOS二极管底部连接的M13总是被限制在线性阻区内。当该三极管电阻连接到M15晶体管的源极时,由具有相同电流的两个支路驱动的电阻大约加倍。这样,即使以相对较小的比率M,也可以形成显式的非线性CM,以便于将M14晶体管作为线性电阻来偏置。由于所有的MOS三极管的电阻都与内部电流有关,因此电路的特性与图11(a)非常相似。但精确度要好得多。减小两个晶体管的尺寸可以得到M13和M14的大电阻,这有利于提高电路的稳定性。

浙公网安备 33010602011771号

浙公网安备 33010602011771号