基于DRV8701的电机驱动设计

栅极驱动芯片DRV8701使用的一些注意事项🤠

引脚配置和功能

| 引脚名 | 引脚编号 | 功能 | 配置 |

|---|---|---|---|

| EN | 14 | 输入PWM | |

| PH | 15 | 控制方向 | |

| VM | 1 | 电源 | 连接至电动机电源;将VM和GND之间并联0.1μF的陶瓷电容和最小为10μF的陶瓷电容 根据驱动电流可能需要额外的电容 |

| GND | 5/16/PPAD | 地 | |

| VCP | 2 | 电荷泵输出 | 通过16V、1μF陶瓷电容连接到VM |

| CPH | 3 | 电荷泵切换节点 | 为CPH和CPL之间连接一个0.1μF的X7R电容耐压高于VM |

| CPL | 4 | ||

| DVDD | 8 | 3.3V逻辑电源稳压器 | 通过6.3V,1-μF陶瓷电容连接到GND |

| AVDD | 7 | 4.8V模拟电源稳压器 | 通过6.3V,1-μF陶瓷电容连接到GND |

| nSLEEP | 13 | 设备休眠 | 将逻辑拉低以使器件进入High-Z的低功耗睡眠模式;内部下拉 |

| IDRIVE | 12 | 栅极驱动电流设置引脚 | 电阻值或电压强制通过此引脚设置栅极驱动电流 |

| VREF | 6 | 模拟参考输入 | 控制电流调节,配置引脚电压在0.3V-AVDD |

| nFAULT | 9 | 故障引脚 | 出现故障时输出低电平,漏极开路输出需要外部上拉 |

| SNSOUT | 10 | 比较输出 | 当驱动电流达到斩波阈值时拉低逻辑低电平;漏极开路输出需要外部上拉 |

| SO | 11 | 分流放大器输出 | 此引脚上的电压等于SP电压乘以AV加上一个偏移量;此引脚上的电容不得超过1 nF |

| SN | 20 | 分流放大器负输入 | 通过电流检测电阻连接到SP并连接到GND |

| SP | 21 | 分流放大器正输入 | 通过电流检测电阻连接到低侧FET管源极和SN |

| GH1 | 17 | 高端栅极 | 连接到高端FET栅极 |

| GH2 | 24 | ||

| GL1 | 19 | 低端栅极 | 连接到低端FET栅极 |

| GL2 | 22 | ||

| SH1 | 18 | 相节点 | 连接至高端FET源极和低端FET漏极 |

| SH2 | 23 |

(1)VCC不是DRV8701上的引脚,但是对于漏极开路输出nFAULT和SNSOUT,需要一个VCC电源上拉。系统控制器电源可以用于该上拉电压,或者这些引脚可以上拉到AVDD或DVDD。

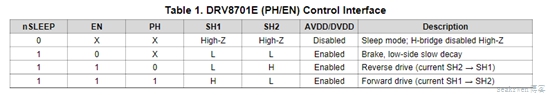

DRV8701E由PH / EN接口控制。下表给出了驱动单刷直流电动机时的完整H桥状态。请注意,表中没有考虑DRV8701E内置的电流控制。正电流是在xOUT1→xOUT2方向上定义的。

IDRIVE

可以通过设置IDRIVE电阻值或强制将电压施加到IDRIVE引脚来调整H桥输出(SHxpins)的上升和下降时间。 如果选择较高的IDRIVE设置,则FET栅极电压将更快地斜坡化。FET栅极斜坡直接影响H桥输出的上升和下降时间

这是SeakrWen的博客,欢迎转载,但请注明出处。

浙公网安备 33010602011771号

浙公网安备 33010602011771号