时序收敛:基本概念

对于FPGA而言,时序收敛是一个很重要的概念。在我看来,时序约束是必要的,但不是在最重要的,我们应该在设计初始就考虑到时序问题,而不是完全的靠约束来获得一个好的结果。但我认为,对FPGA时序的分析能力是理解其运行机制的必要条件。之前也简单看过这方面的内容,却没有很正确的认识。这两天看了看UG612和相关内容,记录在此,这应该有一系列文章,现已基本完成。

系列目录

建立时间和保持时间(setup time 和 hold time)

OFFSET约束(OFFSET IN 和OFFSET OUT)

Clock Skew , Clock uncertainly 和 Period

1. FPGA时序的基本概念

FPGA器件的需求取决于系统和上下游(upstream and downstrem)设备。我们的设计需要和其他的devices进行数据的交互,其他的devices可能是FPGA外部的芯片,可能是FPGA内部的硬核。

对于FPGA design来说,必须要关注在指定要求下,它能否正常工作。这个正常工作包括同步时序电路的工作频率,以及输入输出设备的时序要求。在FPGA design内部,都是同步时序电路,各处的延时等都能够估计出来,但是FPGA内部并不知道外部的设备的时序关系。所以,Timing constraints包括

- 输入路径(Input paths )

- 寄存器-寄存器路径(Register-to-register paths )

- 输出路径(Output paths )

- 例外(Path specific exceptions )

这正好对应了上图中三个部分,Path specific exceptions 暂时不提。

Input paths对应的是OFFSET IN约束,即输入数据和时钟之间的相位关系。针对不同的数据输入方式(系统同步和源同步,SDR和DDR)有不同的分析结果。

Register-to-register paths 对应的是整个FPGA design的工作时钟。如果只有一个时钟,那么只需要指定输入的频率即可。如果有多个时钟,这些时钟是通过DCM,MMCM,PLL生成的,那么显然ISE知道这些时钟之间的频率、相位关系,所以也不需要我们指定。如果这些不同的时钟是通过不同的引脚输入的,ISE不知道其相位关系,所以指定其中一个为主时钟,需要指定其间的相位关系。

Output paths对应的是OFFSET OUT 约束,和OFFSET IN约束很类似,不过方向相反。

2.输入时序约束

The input timing constraints cover the data path from the external pin or pad of the package of the FPGA device to the internal synchronous element or register that captures that data.

输入时序约束控制外部引脚到内部模块的路径。采用OFFSET IN来指出输入时序约束。也就是说OFFSET IN定义了时钟沿河被采集数据的关系(相位)。这里我们关心两类不同的输入方式,系统同步输入和源同步输入。(对于SDR和DDR,即单数据速率和双数据速率而言,区别只在于一个时钟周期的采样次数,不做说明)

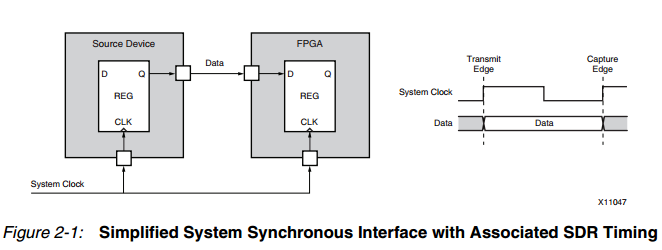

System Synchronous inputs

系统同步输入,指由同一时钟传输和捕获数据,如下图所示。

上图可以看出,FPGA和输入源设备是同源的,共用一个系统时钟。这一个系统时钟在源设备触发输出数据,同时还作为FPGA的时钟接收输入的数据。因此源设备只需要提供输入的数据就可以了。

Source synchronous inputs

源同步如下图所示(这里是DDR,同时在上升沿和下降沿采样)

源同步和系统同步的最大区别在于源设备(Source Device)在输出数据的同时,输出了一路和数据同步的时钟。FPGA采用这一路时钟来进行数据的采样。

这两种输入方式看起来有很大的差别,但是OFFSET IN约束的写法是一致的,后文将详细明。

3.寄存器-寄存器的时序约束

寄存器-寄存器的约束,在同步时序电路中,就是周期的约束。对于完全采用一个时钟的电路而言,对这一个clk指定周期约束即可。但是如果采用了多个时钟,那么情况就复杂了。多个时钟中的“多个”,可能由DCM等倍/分频得到,也有可能FPGA外部就引入了两个时钟信号,还有可能是其他情况。这里Xilinx将其分成了以下几类

- 自动相关同步时钟域

- 手动相关同步时钟域

- 异步时钟域

自动相关同步时钟域(DLL,DCM,PLL,MMCM)

因为它是自动的,从字面意思上看就是自动分析。当我们例化了一个DCM,DCM的输入输出信号之间的关系就已近确定了,譬如频率关系和相位关系。当指定了DCM输入时钟的频率和相关信息之后,再去指定输出的相对关系就有画蛇添足的感觉了,因为这些关系以及在生成DCM的时候确定了。对于PLL,MMCM来说也是一样的。

手动相关同步时钟域

对应上文的“自动”,这里的“手动”指需要人为指定时钟之间的关系。在什么情况下,ISE套件无法知道时钟之间的关系?如果两组时钟都是由FPGA外部引入的,那么它们之间的相位关系是未知的,需要认为指定。时钟之间的相位关系都是相对的,因此这个过程需要指定一个主时钟,之后定义其他时钟和主时钟之间的相对相位关系。

NET “PrimaryClock” TNM_NET = “TNM_Primary”;

NET “RelatedClock” TNM_NET = “TNM_Related”;

TIMESPEC “TS_primary” = PERIOD “TNM_Primary” PeriodValue HIGH HighValue%;

TIMESPEC TS_related” = PERIOD “TNM_Related” TS_Primary_relation PHASE value;

异步时钟域

xilinx无法分析,具体参考ug612。

4.输出时序约束

输出就是输入的逆,因此分析的过程是类似的,分类也是类似的。针对时钟的不同,有系统同步和源同步两种。此处不再详细说明。

系统同步SDR

源同步DDR(一般来说不给约束就可以)

5. 总结

时序收敛的目的是让FPGA design 按预设的逻辑正常的工作。

为了使其正常工作,需要考虑至少三处:FPGA内部的寄存器-寄存器时序要求,FPGA输入数据的时序要求,FPGA输出信号的要求。

2、3、4节的介绍目的在于简述可能遇到的不同情况,旨在说明约束实际上是告诉ISE套件通过设计本身的逻辑不能看出来的关系和要求。

![clipboard[1] clipboard[1]](http://images0.cnblogs.com/blog/663760/201408/282306386264723.png)

![clipboard[6] clipboard[6]](http://images0.cnblogs.com/blog/663760/201408/282306395639335.png)

![clipboard[7] clipboard[7]](http://images0.cnblogs.com/blog/663760/201408/282306402989179.png)

浙公网安备 33010602011771号

浙公网安备 33010602011771号