FPGA VHDL 速查手册

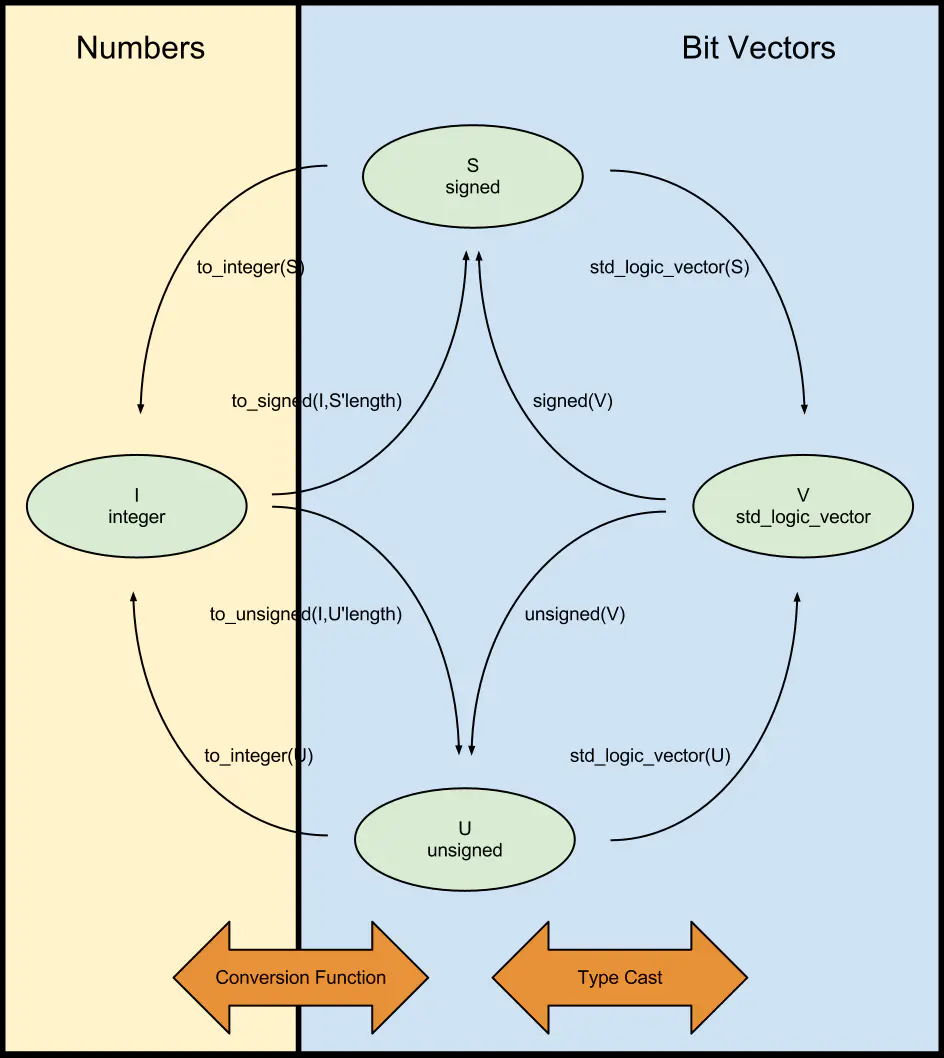

1 数据类型转换

2 常用库

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

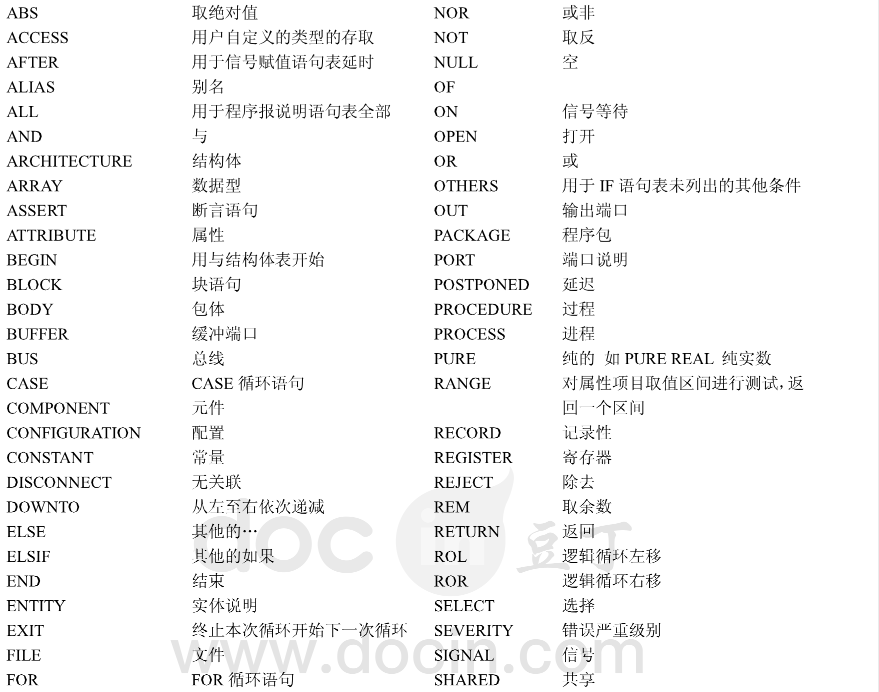

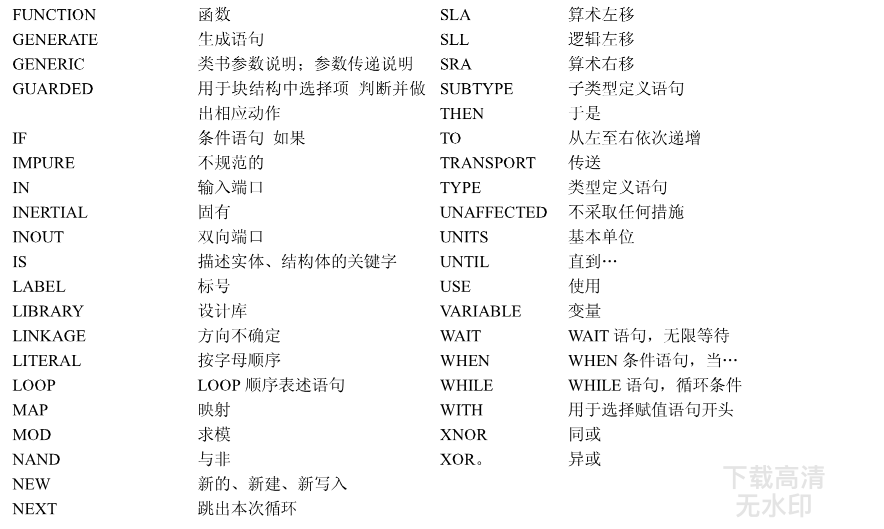

3 关键字

4 简单的例子

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use ieee.numeric_bit.all;

entity vhdl_top is

port(

i_key : in std_logic_vector(3 downto 0);

o_led : out std_logic_vector(3 downto 0)

);

end entity vhdl_top;

architecture bhv of vhdl_top is

component not_gate is

port(

i_key : in std_logic_vector(3 downto 0);

o_led : out std_logic_vector(3 downto 0)

);

end component;

begin

u_not_gate : not_gate

port map(

i_key => i_key,

o_led => o_led

);

end bhv;

5 并行语句

5.1 简单赋值

architecture bhv of xx is

signal a : std_logic;

signal b : std_logic;

begin

a <= '0';

b <= a;

end architecture;

5.2 条件赋值(when else)

architecture bhv of xx is

signal a : std_logic;

signal b : std_logic;

signal sel : std_logic;

signal y : std_logic;

begin

y <= a when sel='0' else b;

end architecture;

5.3 条件赋值(with select when others)

architecture bhv of xx is

signal a : std_logic;

signal b : std_logic;

signal sel : std_logic_vector(1 downto 0);

signal y : std_logic;

begin

with sel select

y <= a when b"01"

b when b"10"

'0' when others;

end architecture;

5.4 并行过程调用

architecture bhv of xx is

signal a : std_logic;

signal b : std_logic;

signal sel : std_logic_vector(1 downto 0);

signal y : std_logic;

procedure proc_sel(

signal a : in std_logic;

signal b : in std_logic;

signal sel : in std_logic_vector(1 downto 0);

signal y : out std_logic

)

is begin

if sel = b"01" then

y <= a;

elsif sel = b"10" then

y <= b;

else

y <= '0';

end if;

end procedure;

begin

proc_sel(

a => a,

b => b,

sel => sel,

y => y

);

end architecture;

浙公网安备 33010602011771号

浙公网安备 33010602011771号