Xilinx ISE Design Suit 10.1快速上手

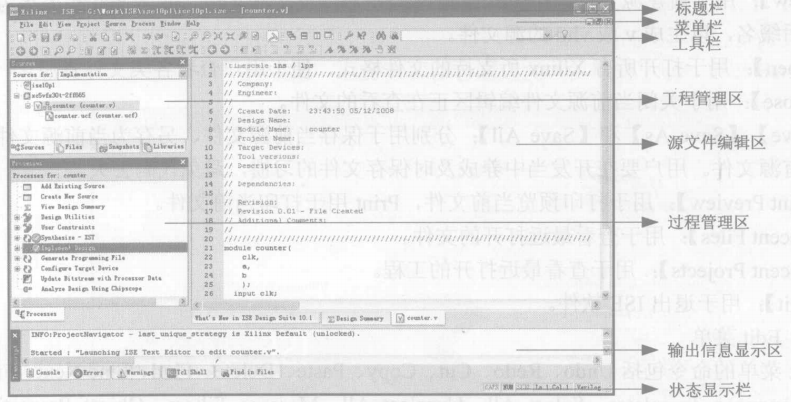

ISE Design Suit 10.1界面布局

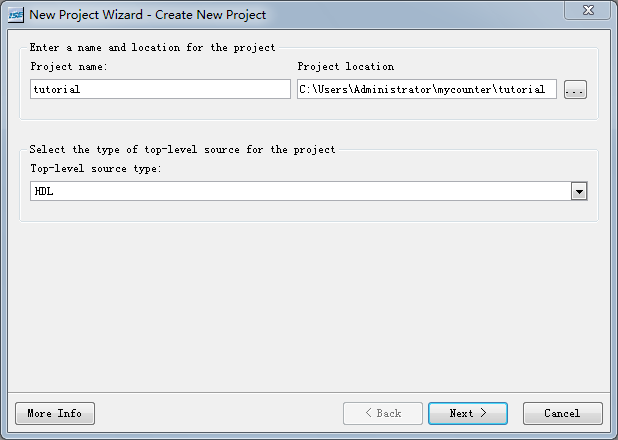

1、创建工程

---->点击File > New Project... ,在弹出的对话框按图填写

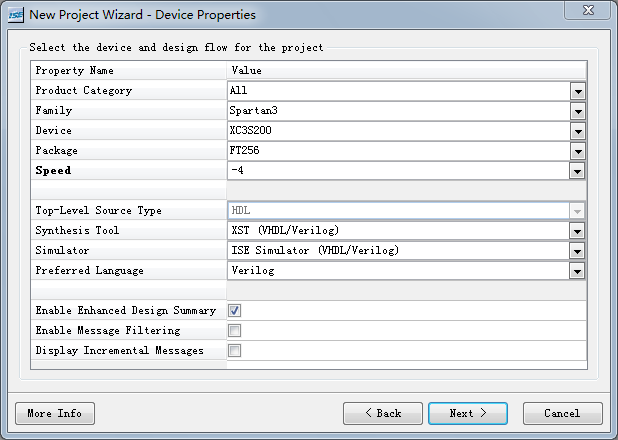

---->点击Next ,在弹出的对话框按图填写

---->一路点击Next,最后点击Finish

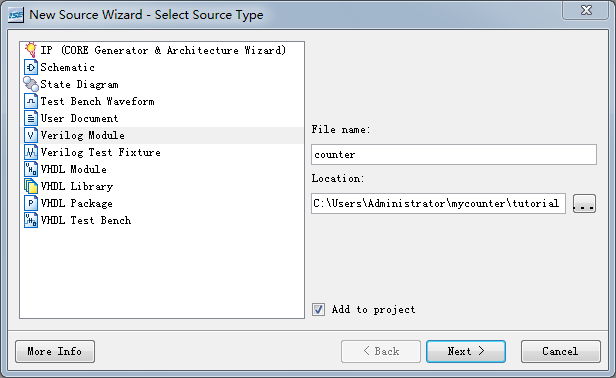

2、建立HDL源文件---->以Verilog为例

---->右键单击工程管理区空白处,在弹出的快捷菜单里选择New Source...

---->在弹出的对话框点击Verilog Module,文件名写入counter,如图

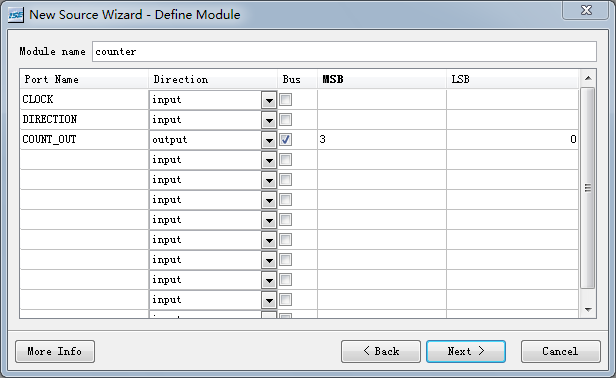

---->按照下图进行填写

---->一路点击Next,最后点击Finish

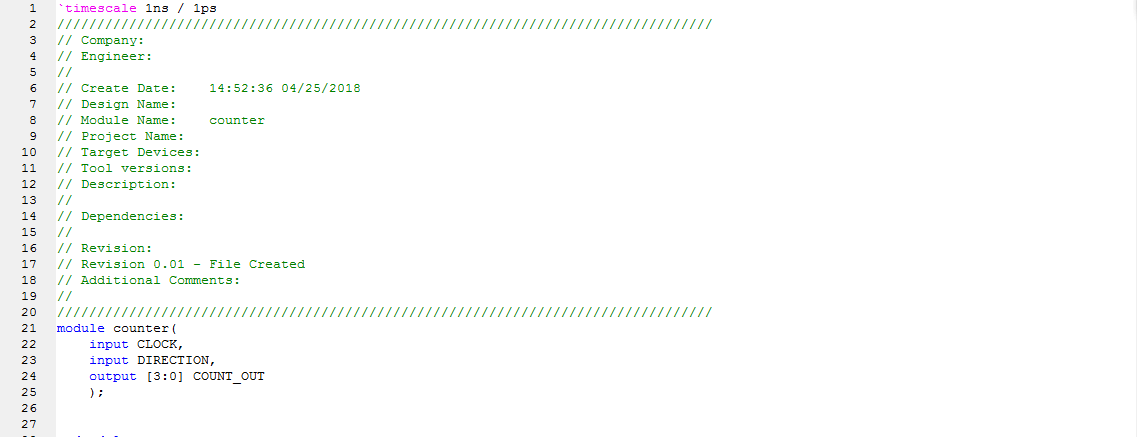

---->源文件如图所示

---->使用代码模板完成设计

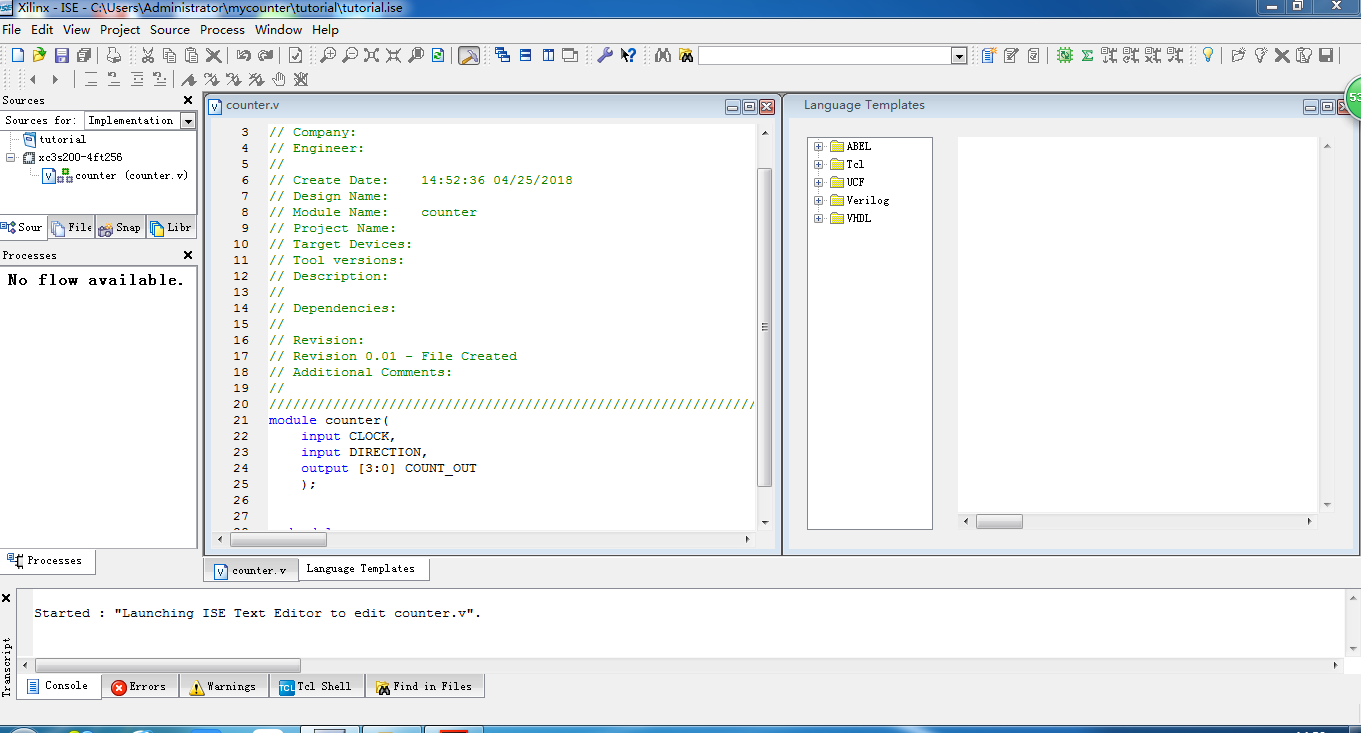

---->点击Edit → Language Templates… 弹出Language Templates对话框,点击Window → Tile

Vertically使源码文件与模板文件同时可见,如图

---->点击“+”号,找到如下模板Verilog → Synthesis Constructs → Coding Examples → Counters → Binary →

Up/Down Counters → Simple Counter

---->点击Edit → Use in File 或Use Template in File工具栏图标将模板复制到源文件里,如图

---->编辑代码文件,如下所示

module counter(input CLOCK; input DIRECTION; output [3:0] COUNT_OUT; ); reg [3:0] count_int = 0; always @(posedge CLOCK) if (DIRECTION) count_int <= count_int + 1; else count_int <= count_int - 1; assign COUNT_OUT = count_int; endmodule

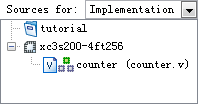

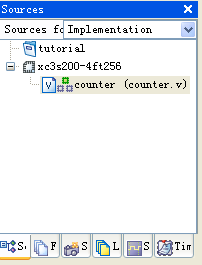

---->按照图示设置为Implementation

---->选中源文件,如图所示

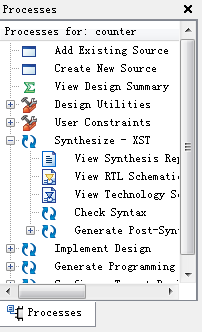

---->展开Synthesize - XST并双击Check Syntax,如图

---->仿真---->选中HDL文件如图

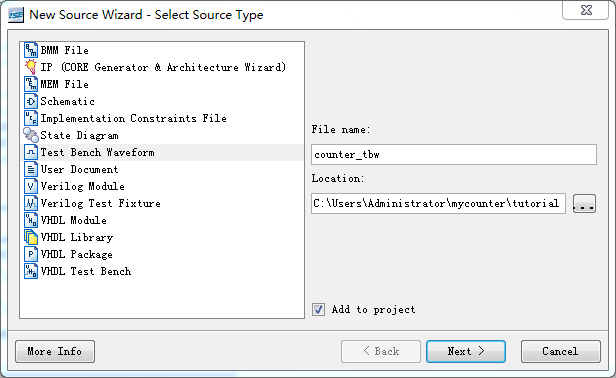

---->点击Project → New Source 并选中Test Bench WaveForm ,并按图填好

---->一路点击Next,然后点击Finish

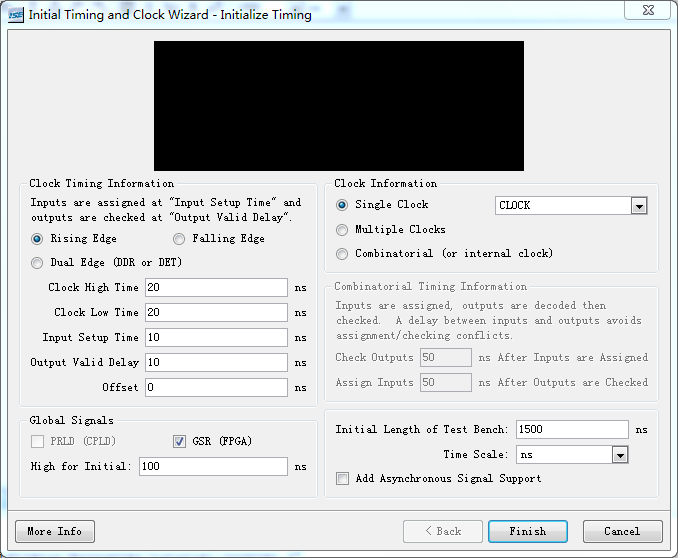

---->在弹出的对话框设置---->时钟频率---->25MHz

---->建立时间---->10ns

---->输出延迟时间---->10ns

---->按照如图设置并点击Finish

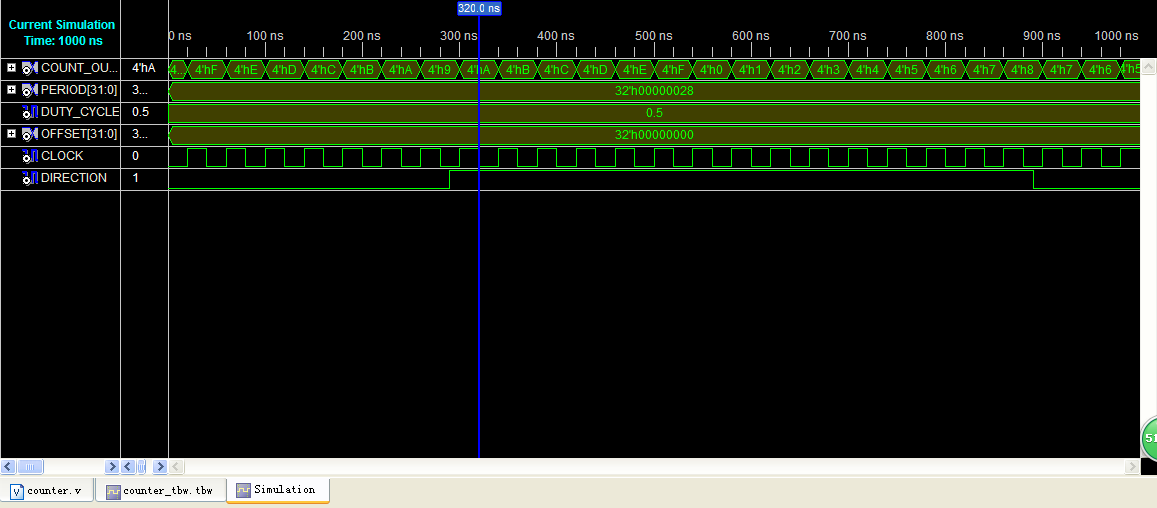

---->出现了波形图如图,蓝色的阴影代表输入建立时间

---->选择Behavioral Simulation ,如图,可以查看仿真波形文件

---->按照如图所示,双击Simulate Behavioral Model 运行仿真

---->仿真结果如图---->根据波形图验证加减功能是否正确

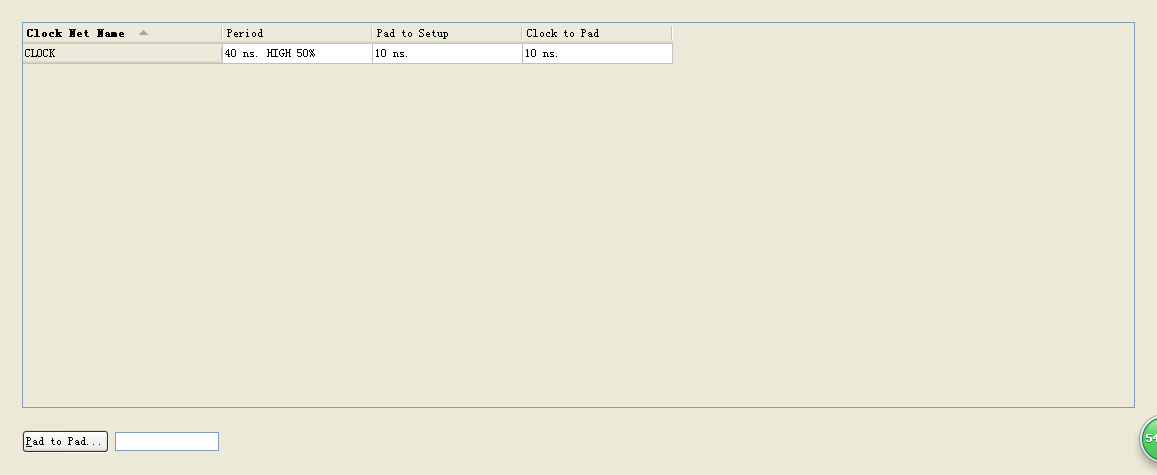

---->创建时序约束---->时序约束

---->时钟周期约束

---->偏移约束

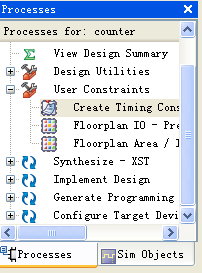

---->选中Implementation,选择源文件counter,如图

---->按图所示双击Create Timing Constraints 生成用户约束文件(UCF)

---->弹出对话框询问是否添加到工程,点击是,counter.ucf被添加到对话框并自动打开约束编辑器

---->如下图填好

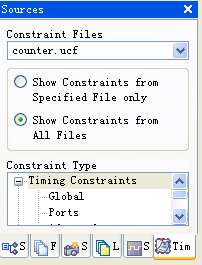

---->如图,点击Timing Constraints,查看并保存约束文件

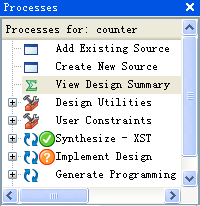

---->执行设计---->选择counter源文件,如图

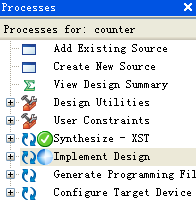

---->双击View Design Summary 查看设计报告,如图

---->双击Implement Design 如图---->执行成功后,上面会有一个绿的检查标志

---->点击All Constraints Met 查看时序约束报告,如图

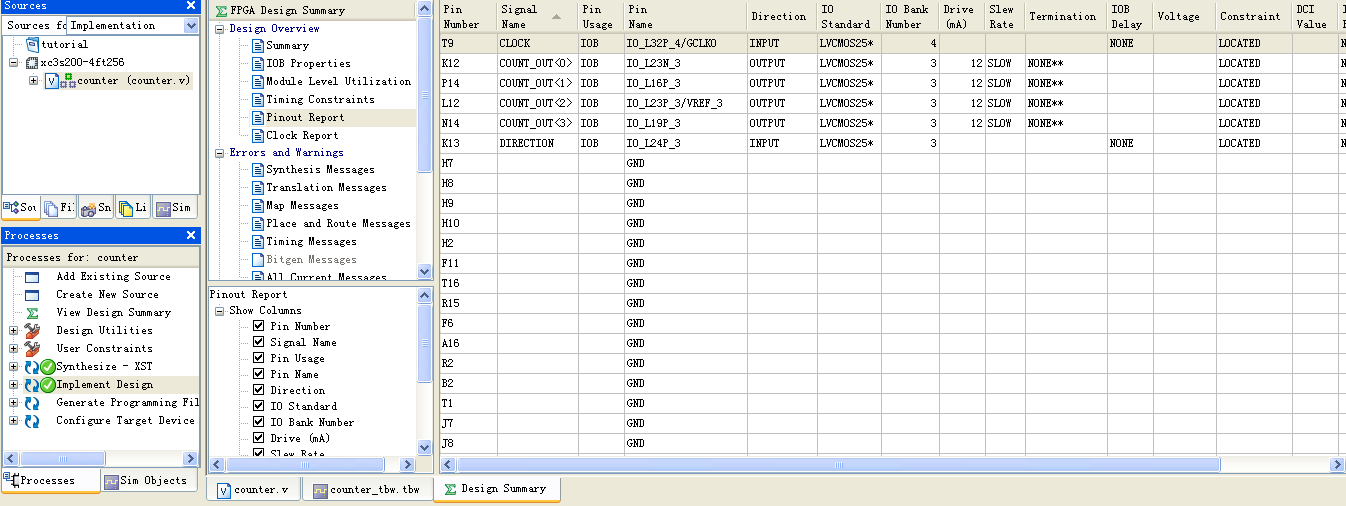

---->指定引脚分配约束---->在Source Window选中counter源文件并双击Floorplan Area/IO/Logic - Post Synthesis

打开Xilinx Pinout and Area Constraints Editor 对话框,如图

---->选择Package View如图,并按图输入引脚名

---->保存文件,选择XST Default <> ,并点击OK

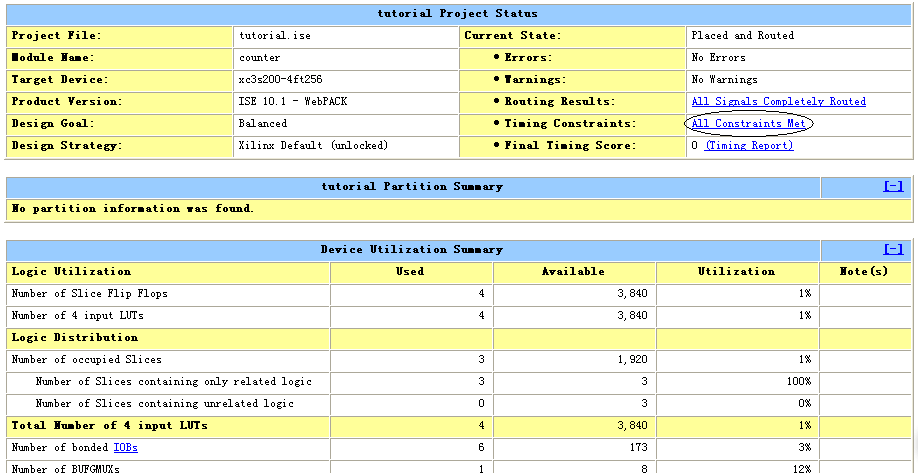

---->重新执行设计并验证引脚位置---->双击View Design Summary

---->选择Pinout Report 并选择Signal Name 栏进行排序

---->双击Implement Design 重新执行设计

---->双击Pinout Report 并选择Signal Name 栏进行排序,结果如图

---->下载程序

浙公网安备 33010602011771号

浙公网安备 33010602011771号