FPGA配置电路设计

Cyclone IV E FPGA要能够正常的工作,除了需要合理的供电外,还需要有正确的配置电路。

Cyclone IV E FPGA是基于SRAM的结构的,而SRAM中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到SRAM中,然后FPGA才能够正常的运行。

Cyclone IV E支持5种配置方式,分别为

主动串行方式(AS)(Active Serial)

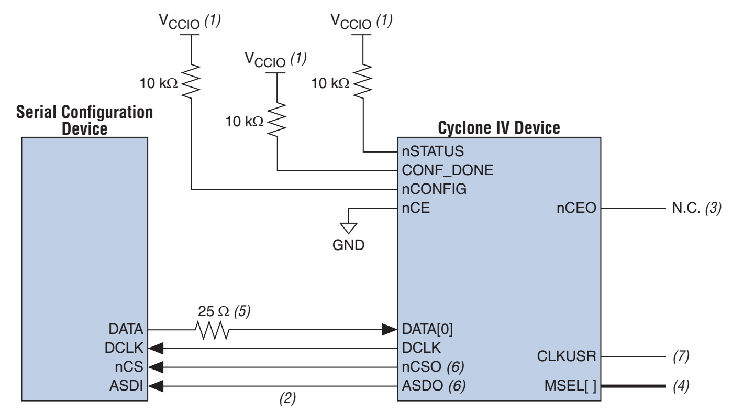

在FPGA主动串行方式(AS)下,由FPGA主动输出控制和同步信号给专用的串行配芯片 (EPCS系列或兼容芯片),在串行配置器件收到命令后,把配置数据发送到FPGA,完成配置过程。

配置器件可使用原厂提供的专用EPCS芯片(EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),也可以使用通用的串行SPI FLASH芯片如M25P40、M25P16、W25Q16等。

由于电路简单,成本低廉,该种方式在中小容量FPGA系统中使用较为广泛。下图为AS配置方式时的应用电路。

可以看到,使用该种配置方式,配置器件和FPGA之间只需连接4根信号线即可实现。DATA为配置数据传输线,DCLK为串行数据时钟传输线,nCS为器件选中信号,ASDI为命令和数据输出引脚。

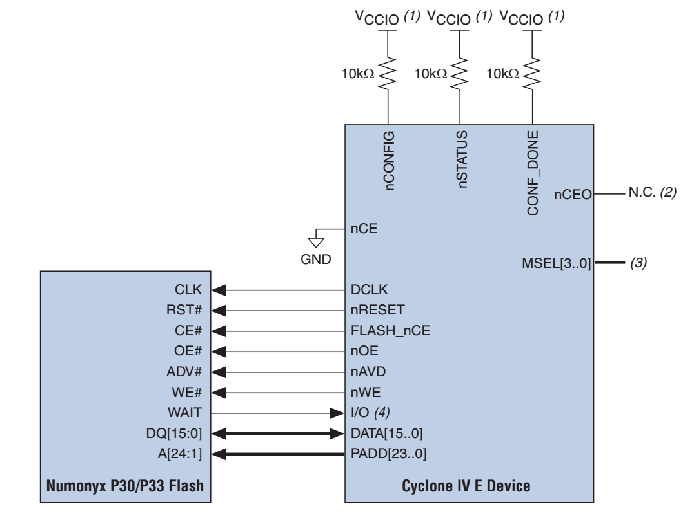

主动并行方式(AP)(Active Parallelism)

主动并行方式和主动串行方式类似,区别在于主动并行方式使用并行接口FLASH存储器作为配置器件,并行接口FLASH存储器与FPGA的配置接口如下所示:

该种方式配置器件和FPGA连接需要耗费较多的FPGA管脚,但是能够显著提升配置数据的的传输速度,对于资源容量较多的FPGA器件,其配置文件的尺寸也相应的较大,因此在对配置过程的时间要求较高的场合,一般使用AP配置方式。对于较低逻辑容量或较少管脚封装的FPGA器件中,一般不支持AP配置方式。

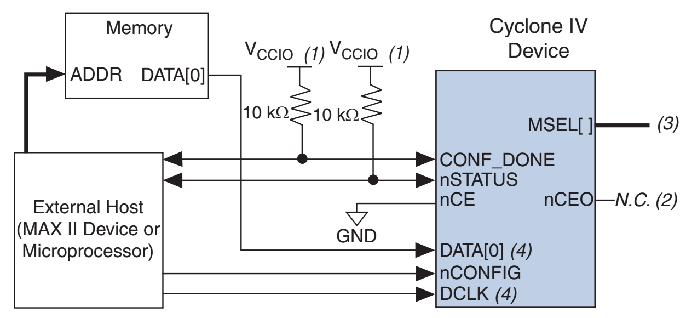

被动串行方式(PS)(Passive Serial)

所有Altera FPGA都支持该方式。可以由Altera的下载电缆、Altera的EPC系列配置芯片,或是智能主机(微处理器或CPLD)来配置。在PS配置时,FPGA配置数据从存储器(可以是EPC系列配置器件或其它Flash器件)中读出,写人到FPGA的DATA0接口上。数据由DCLK时钟信号引脚的上升沿打入FPGA,每个DCLK时钟周期输入1位数据。下图为PS配置方式时的应用电路,该模式下用一个外部的主机如MCU或者CPLD配合存储器实现。

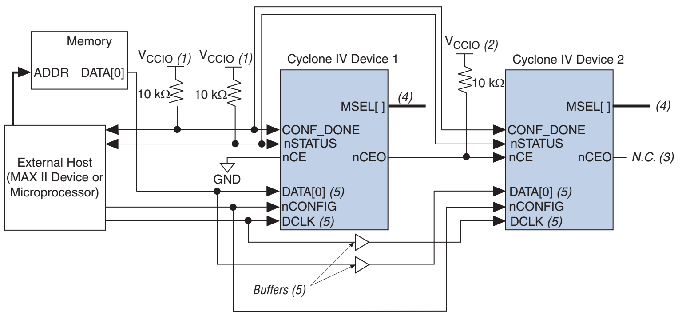

其中nCONFIG是配置启动信号,该信号的一个低电平脉冲启动一次FPGA的配置。DCLK为串行数据时钟,DATA0为串行数据线,nCE为被配置器件选则信号,在整个配置链路只配置一片FPGA的情况下,nCE引脚可以直接接地,表明一直选中。在多片FPGA串行级联情况下,该引脚接到上一级的芯片的nCEO脚上。nCEO脚是选择输出脚。当一个器件被配置完成后,该引脚输出低电平,选中级联的下一级器件,以启动对下一级器件的配置。如果整个链路上只有一片器件,该引脚悬空即可。

下图为典型的一个PS模式配置多片级联的FPGA的应用电路。

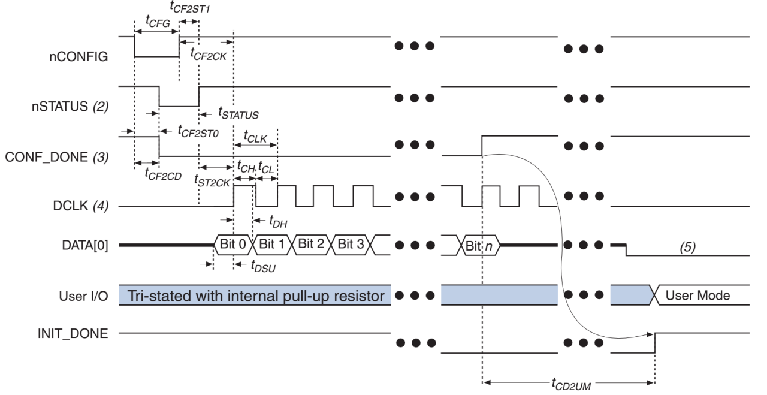

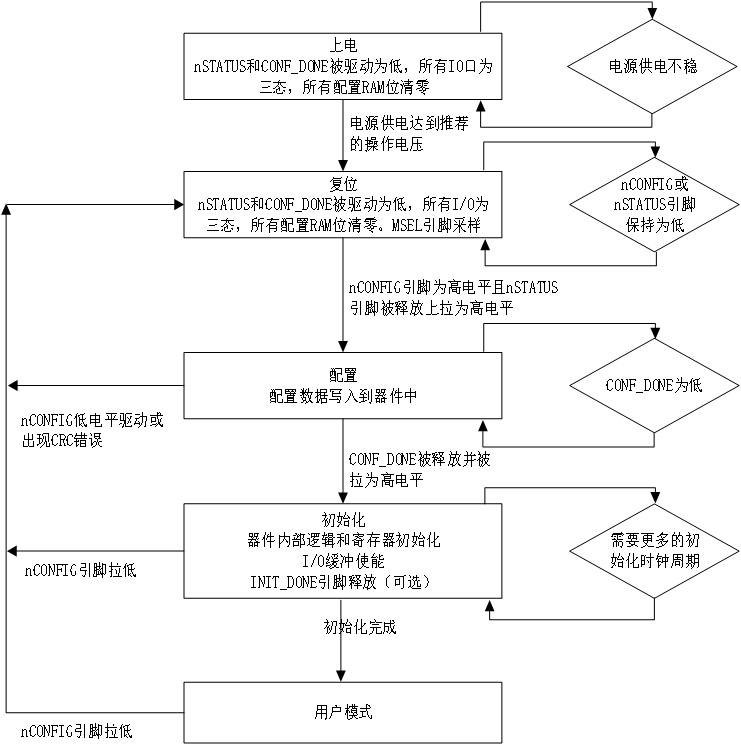

FPGA的配置包括3个阶段:复位、配置和初始化。当nCONFIG引脚信号为低时,FPGA 处于复位状态。从下图可看出,FPGA的nCONFIG引脚上一个低电平到高电平的上升沿将使开漏的nSTATUS引脚被释放,nSTATUS引脚被外部上拉电阻上拉为高电平,FPGA 进入配置模式,开始接收配置数据。在所有配置数据都加载到FPGA后,进人初始化模式 (Initialization),在初始化完成后,进人用户模式(User—Mode)。在配置模式和初始化模式 下,FPGA 用户 I/O 处于高阻态,对于Cyclone 系列器件,用户I/O有内部弱上拉。当进入用户模式后,用户 I/O就按照用户设计的功能工作。

FPGA在上电后,nCONFIG引脚为低电平先进行复位,所有配置RAM内容都清空,I/O 口处于高阻态(或内部弱上拉)。FPGA的状态引脚nSTATUS和CONF_DONE引脚输出低 电平。当nCONFIG引脚产生一个低电平到高电平的上升沿后,FPGA进人配置模式。FPGA会首先采样配置模式(MSEL)引脚的信号状态,以决定采用何种配置模式。随后,FPGA 将释放开漏输出的nSTATUS引脚,使其由外部上拉电阻拉到髙电平,这时表示FPGA可以接收配置数据了。在配置之前和配置过程中,用户I/O 口都是高阻态(或内部弱上拉)。 接收配置数据时,配置数据由DATA(并行配置时为DATA[7..0])引脚送入,配置时钟信号由DCLK引脚送入,配置数据在DCLK的上升沿被锁存到FPGA中。当FPGA成功接收完所有配置数据后,FPGA将释放开漏输出的CONF_DONE引脚,CONF_DONE被外部上拉电阻上拉为高电平,CONF_DONE,表明配置完成并进入 FPGA的初始化。在初始化过程中,内部逻辑、内部寄存器和I/O寄存器将被初始化,I/O驱动器将被使能。之后,FPGA完成进入用户模式的操作,所有内部逻辑以及I/O都按照用户的设计运行。 INIT_DONE引脚上的信号可以指示初始化是否完成。INIT_DONE是一个可选的信号,如使用该功能,需要在Quartus II中指定。 在完成配置后,DCLK和DATA引脚不应悬空,而应被拉成固定高电平或低电平。 从上文分析可知,只要人为地在外部将nCONFIG引脚拉低一段时间,然后再拉髙,便能 重新启动一次配置。所以市面上有些开发板厂家就在nCONFIG脚上接了一个轻触开关到地,按下开关便能将nCONFIG拉低,然后释放,即可启动一次配置。

JTAG配置方式

JTAG协议制定了一种边界扫描的规范,边界扫描架构提供了有效的测试紧密PCB板上元件的能力。边界扫描可以在不使用物理测试探针的情况下测试引脚连接,并在器件正常工作的过程中捕获运行数据。对于FPGA,我们也可以使用JTAG电路来将配置数据送入器件中。对于Altera FPGA,Quartus II软件自动生成用于使用JTAG下载器配置的.sof文件。这种配置方式也是我们在开发和调试的过程中使用最多的方式。

JTAG的指令高于一切其他配置模式,也就是说,JTAG配置方式可以打断其他配置方式的配置过程。

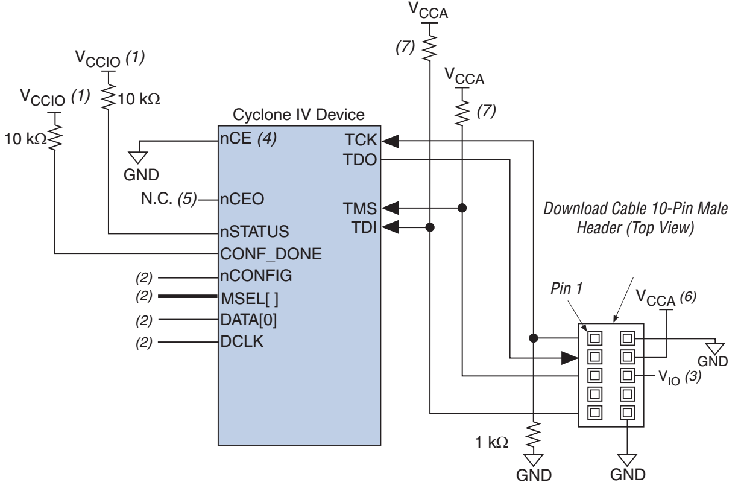

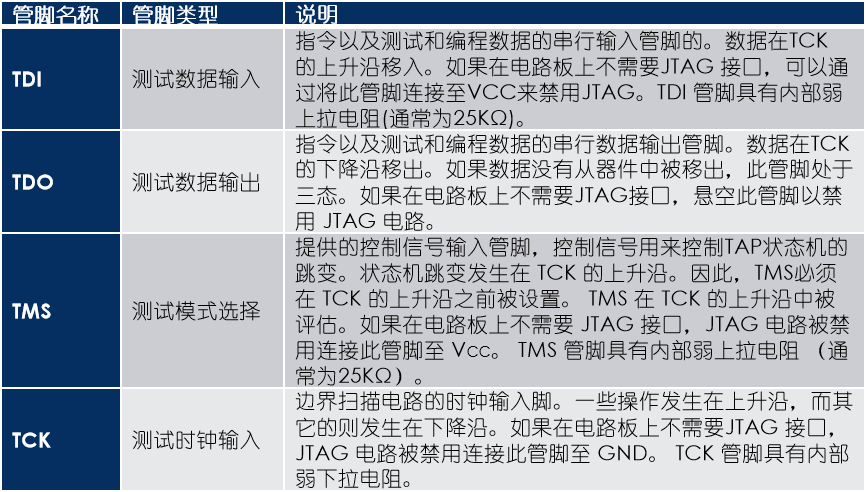

对于在 JTAG 模式中的器件操作所需的四个管脚为TDI、TDO、TMS和TCK。在了解JTAG配置之前,先对这四个管脚的功能进行下介绍。

使用JTAG配置一个器件时,编程软件(Quartus Programmer)会旁路所有其它的器件。在旁路模式下,器件通过一个旁路寄存器将编程数据从 TDI 管脚传至 TDO 管脚,该方案的目的就是在编程软件编程器件的时候能够实施校验。即通过TDI送入器件的配置数据会在一个时钟周期之后呈现在TDO上。Quartus II 软件在完成配置后验证成功的 JTAG 配置。在配置结束后,软件通过JTAG端口检查CONF_DONE的状态,以确认配置是否完成。如果 CONF_DONE不为高,那么 Quartus II 软件就获悉配置是失败的。如果 CONF_DONE 是高的,软件就确定配置是成功的。在使用JTAG TDI 端口连续发送配置比特流之后, TCK 端口计入一个额外的时钟周期以执行器件的初始化。

配置方案选择与设置

Cyclone IV E器件支持多种配置方式,那么器件在上电或者收到配置启动信号(nCONFIG)后,就需要通过一定设置才能确定究竟使用哪种方式完成配置。在器件上,由专用的四个信号MSEL[3..0]来设置配置方式。需要注意的是,较小的 Cyclone IV E 器件或封装选项(E144 和 F256 封装)不具有 MSEL[3] 管脚。在不具备 MSEL[3] 管脚的 Cyclone IV E 器件,不支持使用3.0V或2.5V电平标准的主动串行快速上电复位 (AS Fast POR)配置方案和主动并行(AP)配置方案。要配置这些设备与其它支持的配置方案,根据下表中的MSEL设置选择 MSEL[2..0] 管脚。

可以看到,当确定使用一种配置方案的时候,根据配置引脚(DCLK、DATA)所在IO Bank的IO供电电压不同,MSEL的设置也不一样。例如希望使用AS标准方式配置,当配置电压标准为3.3V时,MSEL[3..0] = 0010,而当配置电压标准为3.0V或2.5V时,MSEL[3..0] = 0011。所以,确定MSEL的前提应该是确定配置电压标准。具体到E144或者F256的封装上,由于没有MSEL3,当确定使用AS方式方式配置时,如果配置电压为3.3V,则应该设置MSEL[2..0] = 010,当确定使用PS方式配置时,如果配置电压为3.3V,则应该设置MSEL[2..0] = 000。需要注意的是,对于MSEL信号,要么直接连接到VCCA(2.5V),要么直接连接到GND,不得悬空或者串接电阻。

如需详细对每个知识点探查,可查看《Cyclone IV Device Handbook》文档中相关章节,以获得更加细致的描述。

浙公网安备 33010602011771号

浙公网安备 33010602011771号