FPGA_IO Bank供电方案

Cyclone IV E FPGA器件中,每个器件的IO口都分成了8组,每一组称为一个IO Bank。

同一个Bank中的所有IO供电相同,各个Bank的IO供电都可以不同,IO供电支持1.2V、1.5V、1.8V、2.5V、3.0V、3.3V多种电平标准。

具体的可根据该Bank上的IO功能确定

如某个IO Bank上连接的是DDR2存储器,则该IO Bank的供电要求为1.8V。

若某IO Bank被确定为使用LVDS功能,则该IO Bank的供电需要被配置为2.5V。

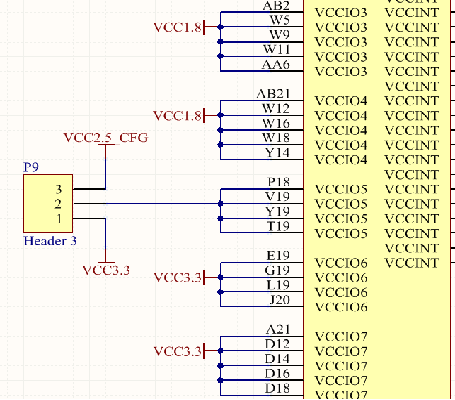

IO供电在器件中被标注为VCCIOx,其中x为IO Bank编号。

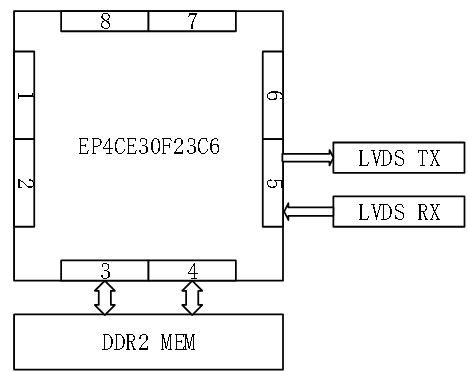

如下图为带DDR2和LVDS接口的开发板IO供电电路,由于Bank3、Bank4被设计用于连接DDR2 SDRAM存储器,因此VCCIO3和VCCIO4连接到了1.8V的供电电源上。

Bank5被配置为LVDS或普通扩展IO,当Bank5上的IO作为通用IO口时,可以使用3.3V供电,当Bank5上的IO用作LVDS功能时,则只能使用2.5V供电,因此使用P9实现VCCIO5的供电电压进行切换。

在开发板或最小系统板等类型产品中,IO 口的供电电压根据系统的实际应用,可能会不同,因此在必要的情况下,可能需要某些IO 口的供电电压能够在使用的时候根据需要设置或调整。

关于IO口供电电压的调整,上述介绍了基于跳线的一种简易切换方式。

使用跳线直接切换是一种简易的方式,适合于供电切换可选项比较少的情况(如只需在2.5V和3.3V中切换)。

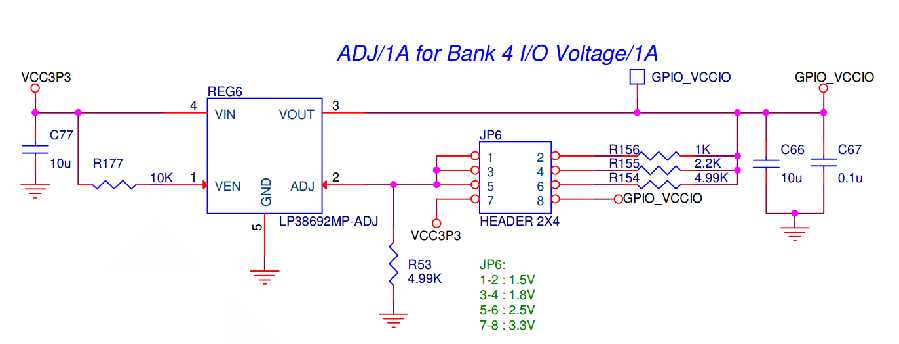

另一种推荐的切换方式是使用可调降压电路,通过跳线直接切换不通的分压反馈电阻来设置降压电路的输出值。

例如对于上述提到的NCP1529,可以通过跳线选择接入电路的不同的R1阻值来实现不同电压输出。此种方式在面对需要调整的选择比较多时,比较方便。如下图JP16,通过短接不通的短接线,就能选择接入反馈电路的分压电阻的阻值,从而设定不同的GPIO_VCCIO的电压值。

浙公网安备 33010602011771号

浙公网安备 33010602011771号