在WCH的官网可以搜索相应的芯片型号如“585” “592”便可以下载DS手册和EVT开发包,在EVT开发包的PUB文件夹下有芯片的原理图。

设计注意点如下:

一.电源部分:

1.供电电压

VIO33/VDD33供电引脚部分芯片支持1.7v供电,通常最低2.3v,最大供电电压为3.6v,详细数据可见DS手册参数章节。

2.电源设计易错点

VDICID数字电源和VDCIA 模拟电源引脚需通过导线连接,原理图节点连接法在某些layout平台可能会报错,设计时可以统一下命名节点。

VINTA引脚为ADC和BLE基准电压,只需接电容到GND即可,不可以接到VCC上,正常电压是1.035v-1.065v之间。

3.DCDC和LDO

芯片内部工作电压比较低,一般外部供电是3.3v,不同的降压方式效率有所不同:

DCDC方式:电流低功耗小,需要贴L1电感,一定程度上降低蓝牙RX的接收灵敏度;

LDO方式:电流高功耗大,无需贴电感只需VSW和VDCID并联或接0欧姆电阻,降低成本。

默认例程中均使用LDO方式,使用DCDC方式需将宏定义DCDC_ENABLE设置为TRUE。

DCDC方式功率电感选择:

CH573/1 CH583/2 ---22uH/DCR<=2ohnm/额定电流>=100mA(WCH的开发板用的是顺络SPH202012H220MT/YNR2016-220)

CH585/4 CH592/1 ---10uH-22uH/DCR<=1ohnm/额定电流>=50mA(DCR也可稍大,DCR越大,DCDC效率稍有降低)

4.PCB设计注意点

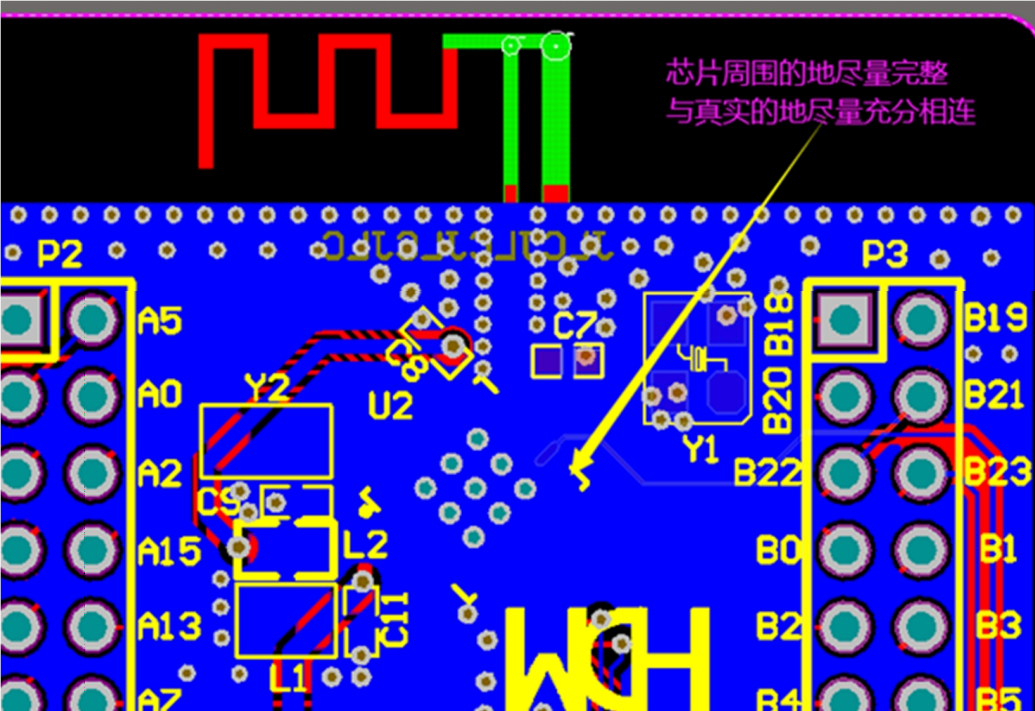

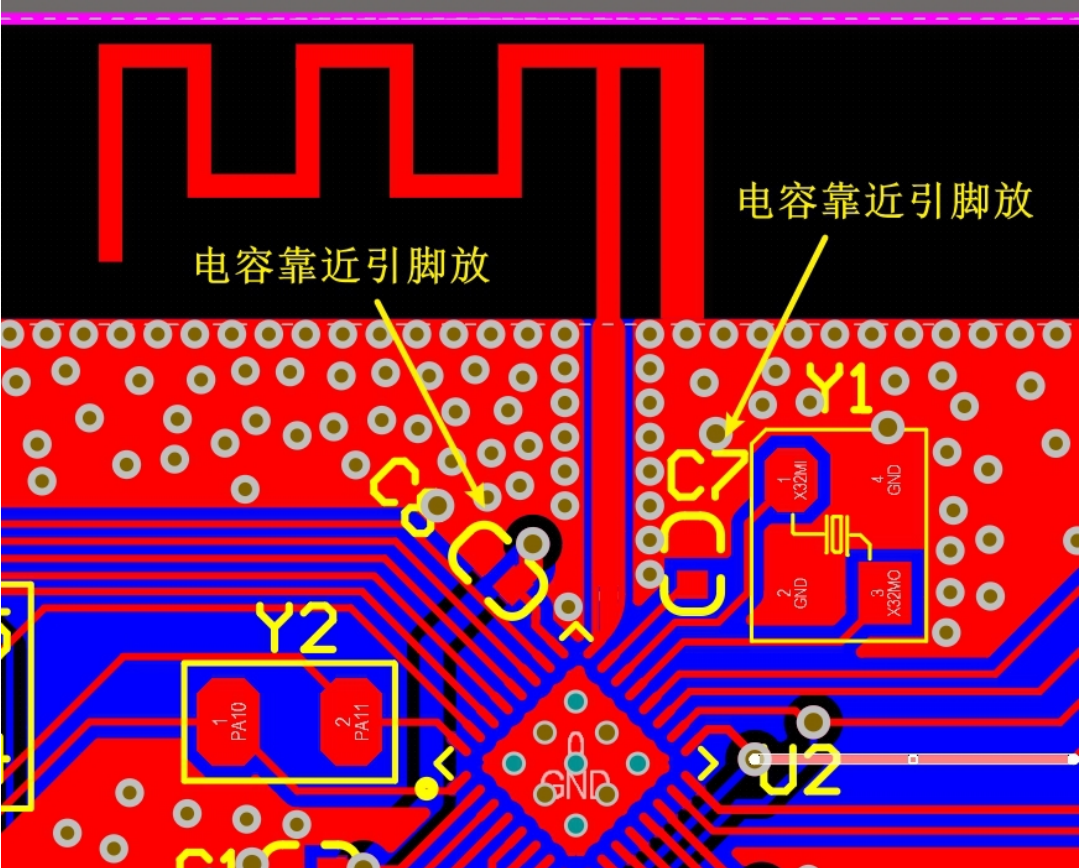

C1 C7 C8 C11这四颗电容在PCB绘制时需靠近芯片引脚放置,电容的GND端走最短回路到芯片的GND。

二.时钟部分:

1.高频晶体

Y1必须要接且需要是32MHz,无需外接匹配电容,推荐参数:32MHz/10pf/10ppm

使用32Mhz/10ppm/12pF会导致默认偏差20ppm左右,需要代码开始加入HSECFG_Capacitance(HSECap_20p);

2.低频晶体

Y2选接,无需外接匹配电容,推荐参数:32.768KHz/12.5pf/20ppm

若对RTC精度要求不高(内部误差一天约2分钟,接Y2误差一天约2秒钟),不需要蓝牙主机功能可以不接Y2。

需要蓝牙主机功能和uA级别低功耗必须接Y2。

3.有源晶体

上述的晶体均为无源晶体,高频晶体也可以接有源晶体做校准板,

有源晶体接法:有源晶体输出脚串联150pF电容到芯片X32MO引脚上(是的,你没看错是X32MO,不是X32MI)

三.外设部分

1.LED灯珠

LED1和LED2均没有和GPIO相连,测试时可将任意GPIO通过杜邦线连接到LED引脚上进行点亮测试。

2.KEY按键

2.S2和S3分别的硬件复位引脚PB23(接低电平有效)和默认BOOT引脚PB22(接低电平有效)。

四.复位引脚

PB23为复位引脚,可在isp下载时选择开启和关闭,若使用该引脚的串口等功能则需要将RST关闭。

五.量产烧录引脚

1.USB烧录

预留任意一组USB都可以进行下载,USB下载需要上电时BOOT引脚接地触发所以BOOT引脚必须要留出,

2.UART烧录

预留PA8/PA9这组串口进行串口烧录,UART串口烧录可以免按键烧录,可以不预留BOOT引脚,第一次打板建议将BOOT引脚留出备用。

3.SWD烧录

预留PB14/PB15引脚,此烧录方式可用于调试,量产脱机烧录器工具不支持使用此接口烧录CH5xx芯片,且需要使用USB或UART接口通过ISP开启,故USB/UART接口必须选其一留出。

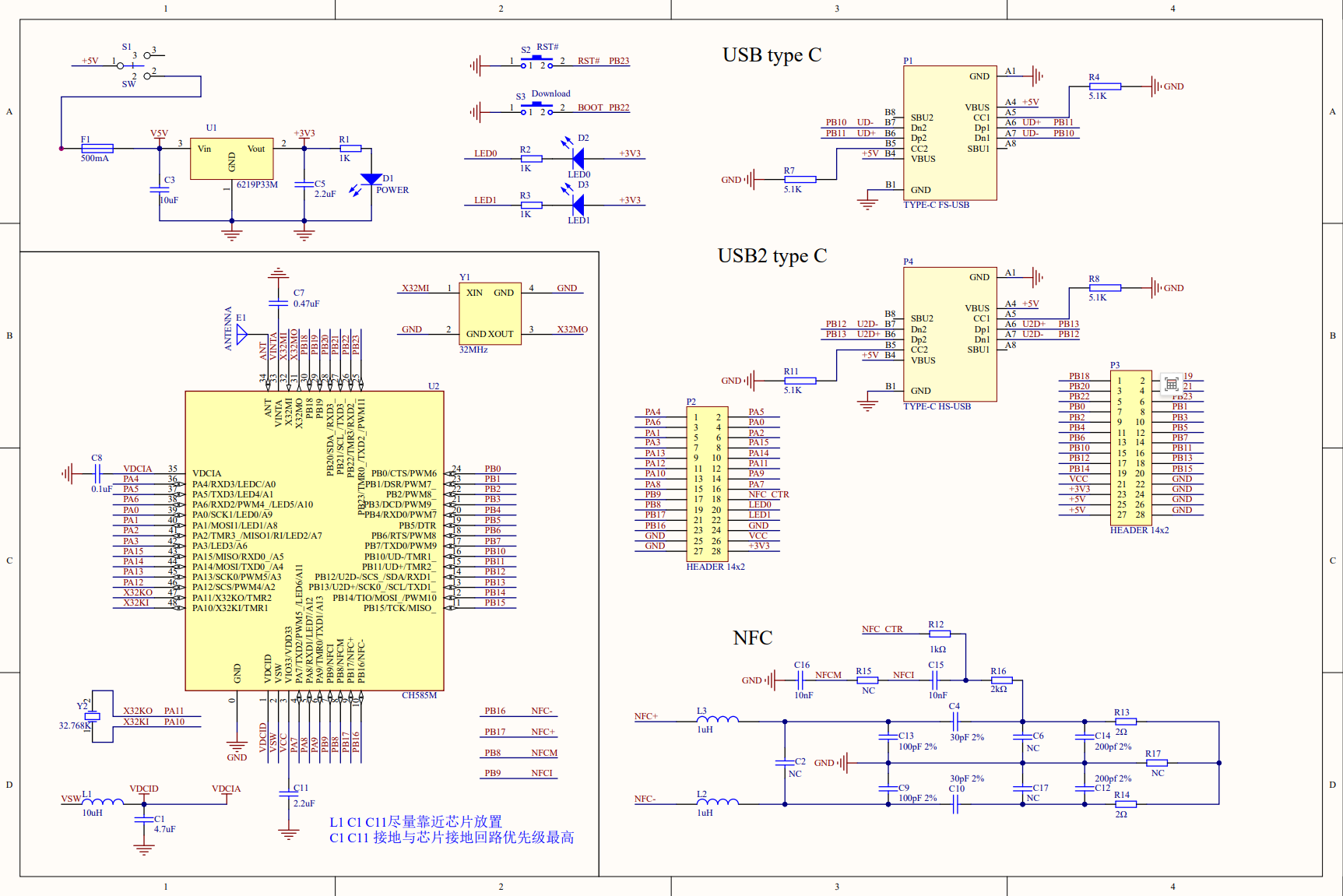

六.原理图设计

上图为585EVT PUB文件夹下的原理参考。

七.PCB设计

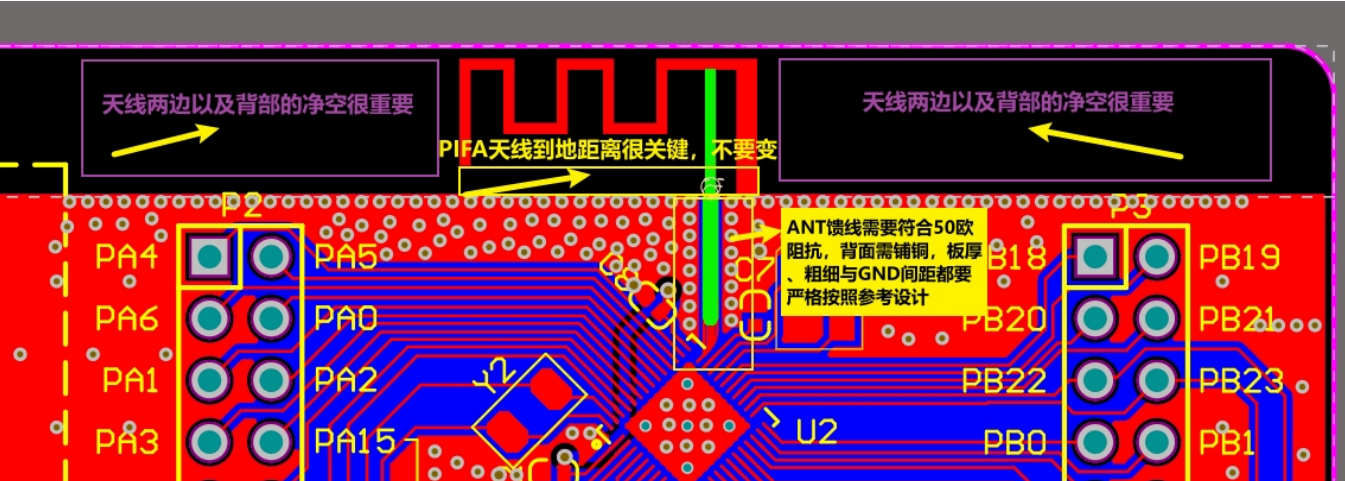

1.天线设计

ANT引脚到天线部分的馈线需要符合50欧姆阻抗匹配,可以在此链接获取不同板厚和大小天线封装:SCHPCB.ZIP - 南京沁恒微电子股份有限公司

2.芯片地设计

芯片底部铺铜,打多个过孔到背部公共地,以保证良好的电流回路。

过孔大小适中,兼顾散热和焊接。

如铺铜面积较大,考虑中间留适当空隙再相连,以免焊锡分布不均影响接地。

3.元器件布局

芯片电源引脚VIO33/VDICD/VDCIA/VINTA引脚上的电容靠近引脚放置。

浙公网安备 33010602011771号

浙公网安备 33010602011771号