ds180 7 Series FPGAs Data Sheet: Overview

一、通用描述

Xilinx 7系列FPGA包含四个家族,针对不同系统需求提供全面支持。从低成本、小尺寸和高容量应用到高性能连接带宽、逻辑能力和信号处理能力的应用,都能找到合适的解决方案。

四个FPGA家族简介

- Spartan®-7 系列:主打低成本、低功耗、高性能I/O。提供小型封装,适合需要最小PCB面积的设计。

-

Artix®-7 系列:针对低功耗应用场景,支持高速串行收发器和高吞吐量的DSP与逻辑运算。

-

Kintex®-7 系列:性价比最佳

-

Virtex®-7 系列:提供最高系统性能与容量

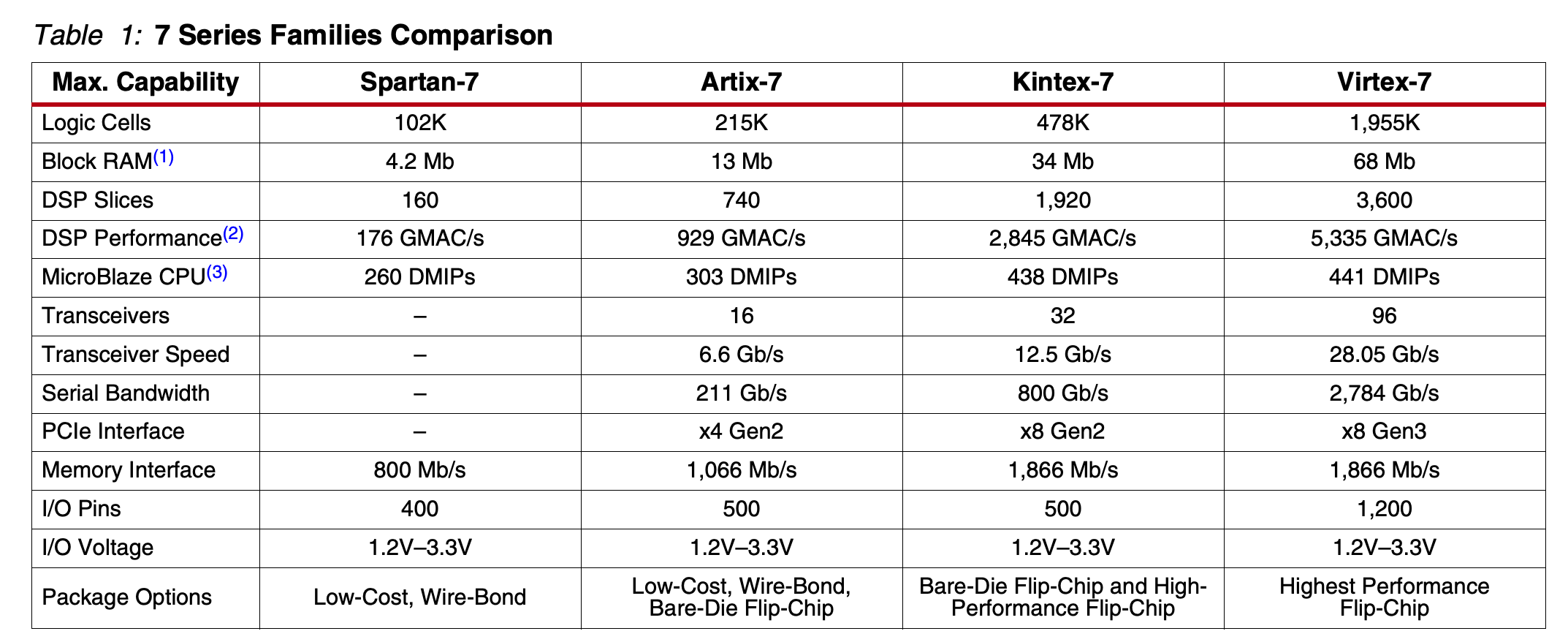

系列对比如下表

其中常用型号为Spartan-7 XC7S25(约60元),Artix-7 XC7A35T(约120元)以及Kintex-7 XC7K325T(约420元),XC7S25缺少部分收发器,但已经适用于大多数场景,在预算控制的情况下,一般来说资源使用情况在85%以下不需要太多的时序优化操作。

二、主要功能特性总结

-

先进FPGA逻辑架构:基于6输入查找表(LUT)技术

-

块RAM资源:36 Kb双端口Block RAM,内置FIFO

-

I/O接口:SelectIO™ 技术,支持高达DDR3 1,866 Mb/s 接口

-

高速串行通信:内置多千兆位收发器,速率范围从600 Mb/s 到 6.6 Gb/s(部分型号可达28.05 Gb/s)

-

模拟接口:用户可配置的XADC模块,包括两个12位1MSPS ADC,以及片上温度和电源传感器

-

数字信号处理(DSP):DSP Slice 包含25x18乘法器、48位累加器和预加法器,支持高性能滤波器设计

-

时钟管理:CMT(时钟管理模块),结合PLL 和 MMCM,提供高精度、低抖动时钟控制

-

嵌入式处理器:支持MicroBlaze™软核处理器,快速部署嵌入式系统

-

PCIe接口:提供集成PCIe模块,支持最多x8 Gen3 Endpoint和Root Port设计

一、堆叠硅互连技术(SSI 技术)

- 用于 Virtex-7 系列 FPGA,实现超高容量。

- 多个 Super Logic Regions 通过无源中介层连接。

- 支持超过 10,000 条跨 SLR 连接。

- 具有低延迟、高带宽和低功耗优势。

- 支持大量超长布线资源(SLL)和高性能时钟线。

- 实现比传统制造方法更高的逻辑密度。

- 缩短高容量 FPGA 的上市时间并降低风险。

二、可配置逻辑块(CLBs)、切片(Slices)和查找表(LUTs)

- 每个 LUT 是 6 输入查找表,支持分布式 RAM 或移位寄存器(SRL)。

- 4 个 LUT + 8 个触发器组成一个 Slice。

- 两个 Slice 组成一个 CLB。

- 最多 50% 的 Slice 可以用作分布式 RAM 或 SRL。

示例说明:

- Spartan-7 中 XC7S50 有 52,160 个逻辑单元(Logic Cells),意味着约 13,040 个 Slice。

- 每个 Slice 可灵活用于组合逻辑、寄存器、RAM 或移位寄存器。

三、时钟管理(Clock Management)

- 每个 CMT 包含一个 MMCM 和一个 PLL。

- 支持频率合成、相位偏移、低抖动生成。

- 支持三种滤波模式:低带宽、高带宽、优化模式。

- MMCM 支持分数倍频和精细相位调节(最小步进 11.2 ps @ 1600 MHz)。

时钟分布类型:

- BUFG(全局时钟缓冲)

- BUFR(区域时钟缓冲)

- BUFIO(I/O 专用时钟)

- BUFH(水平时钟缓冲)

- BUFMR(模块级时钟缓冲)

- 高性能时钟路径

四、块 RAM(Block RAM)

- 每块为 36 Kb,可拆分为两个独立的 18 Kb 块。

- 支持双端口访问,每个端口宽度可达 72 位。

- 支持同步操作、编程数据宽度、FIFO 控制器。

- 支持 ECC 错误检测与纠正(单比特纠错、双比特检错)。

示例说明:

- XC7VH870T 有最多 1,880 块 Block RAM,总容量高达 67.68 Mb。

- 可用于缓存、图像处理、通信协议中的数据缓冲。

五、数字信号处理模块(DSP Slice)

- 包括预加法器、25 x 18 乘法器、加法器、48 位累加器。

- 双 24 位加减/累加等SIMD操作。

- 支持对称滤波优化,减少 DSP 使用数量达 50%。

- 支持模式检测器,用于舍入和逻辑功能。

示例说明:

- 在 FIR 滤波器设计中,使用预加法器可以显著减少乘法器资源消耗。

- 可用于 FFT、卷积、图像处理等高性能信号处理任务。

六、输入/输出(I/O)功能

- 支持 DDR3 接口速率高达 1,866 Mb/s。

- I/O 类型:HR(1.2–3.3 V)和 HP(1.2–1.8 V)。

- 支持差分标准(LVDS、BLVDS、SSTL、HSTL)。

- 支持 T_DCI(3态数字控制阻抗)用于板上终端。

- 支持 ODELAY/IDELAY(延迟校准)和 ISERDES/OSERDES(串并转换)。

七、高速串行收发器(Gigabit Transceivers)

📌 支持速率:

| 收发器类型 | 最大速率 |

|---|---|

| GTP | 6.6 Gb/s |

| GTX | 12.5 Gb/s |

| GTH | 13.1 Gb/s |

| GTZ | 28.05 Gb/s |

- 支持低功耗模式(芯片间接口优化)

- 支持自动均衡(CTLE、DFE)

- 支持编码(8B/10B、64B/66B)

- 支持 Out-of-Band 信令(OOB),适用于 PCIe、SATA 等协议。

示例说明:

- 实现 100Gbps 通信接口

- 光模块接口

- 背板通信

- 高速 ADC/DAC 接口

八、PCIe 集成模块

- PCI Express Base Spec 2.1 或 3.0

- 支持 Gen1(2.5 Gb/s)、Gen2(5 Gb/s)、Gen3(8 Gb/s)

主要功能:

- 支持 Endpoint 和 Root Port 模式

- 支持 SR-IOV(单根虚拟化)

- 支持 AER(高级错误报告)、ECRC(端到端 CRC)

- 支持 AXI4 / AXI4-Stream 接口

示例说明:

- FPGA 作为 PCIe 设备接入主机

- 实现 FPGA 到 FPGA 之间的高速互联

- 网卡等外部设备连接 FPGA

九、配置与安全性

支持方式:

- SPI(x1/x2/x4)

- BPI(x8/x16)

- Master/Slave 模式

- 支持 MultiBoot(多启动)和安全更新

安全机制:

- 256-bit AES 加密

- HMAC/SHA-256 认证

- 内部 eFUSE 存储密钥

- 支持部分重配置(Partial Reconfiguration)

特色功能:

- 断电后重新加载

- DRP 接口可用于动态修改 MMCM、PLL、XADC 等模块参数

- 支持 Bitstream 读回与验证

十、模拟接口模块(XADC)

- 两个 12 位、1MSPS 的 ADC

- 支持最多 17 个外部模拟输入通道

- 内置温度传感器(±4°C)和电源监控(±1%)

- JTAG 接口可实时获取测量数据

示例说明:

- 温度监测、电压监控

- 模拟信号采集

- 工业控制、嵌入式系统中的状态监控

十一、封装与引脚信息

- 引线键合(Wire-bond)

- 倒装芯片(Flip-chip)

- 裸芯倒装(Bare-die flip-chip)

- 支持 Pb-free 和 Pb 封装选项

示例说明:

| 封装名 | 引脚数 | 尺寸 | 支持器件示例 |

|---|---|---|---|

| FLG1155 | 1155 | 35 × 35 mm | XC7VH580T |

| FLG1931 | 1931 | 45 × 45 mm | XC7VH870T |

各系列功能对比

| 属性 | Spartan-7 | Artix-7 | Kintex-7 | Virtex-7 |

|---|---|---|---|---|

| 主打特点 | 成本敏感、小尺寸 | 低功耗、串行收发器 | 高性价比 | 最高性能、最大容量 |

| 最大逻辑单元 | ~100K | ~300K | ~1M | ~2M |

| 最大 DSP Slice 数量 | ~1,100 | ~3,000 | ~8,000 | ~12,000 |

| 高速收发器 | 不支持 | GTP/GTX | GTP/GTX/GTH | GTP/GTX/GTH/GTZ |

| PCIe 模块 | 无 | 有 | 有 | 有 |

| XADC | 部分支持 | 支持 | 支持 | 支持 |

| Block RAM | ~4,320 Kb | ~8,000 Kb | ~50,000 Kb | ~67,680 Kb |

| 封装 | 小型封装为主 | Flip-chip | Flip-chip | Flip-chip + SSI |

版权声明: 本博客所有文章除特别声明外,均采用 CC BY-NC-SA 3.0 许可协议。转载请注明出处!

浙公网安备 33010602011771号

浙公网安备 33010602011771号