ModelSim仿真教程 Label: Research

首先激活modelsim然后打开modelsim

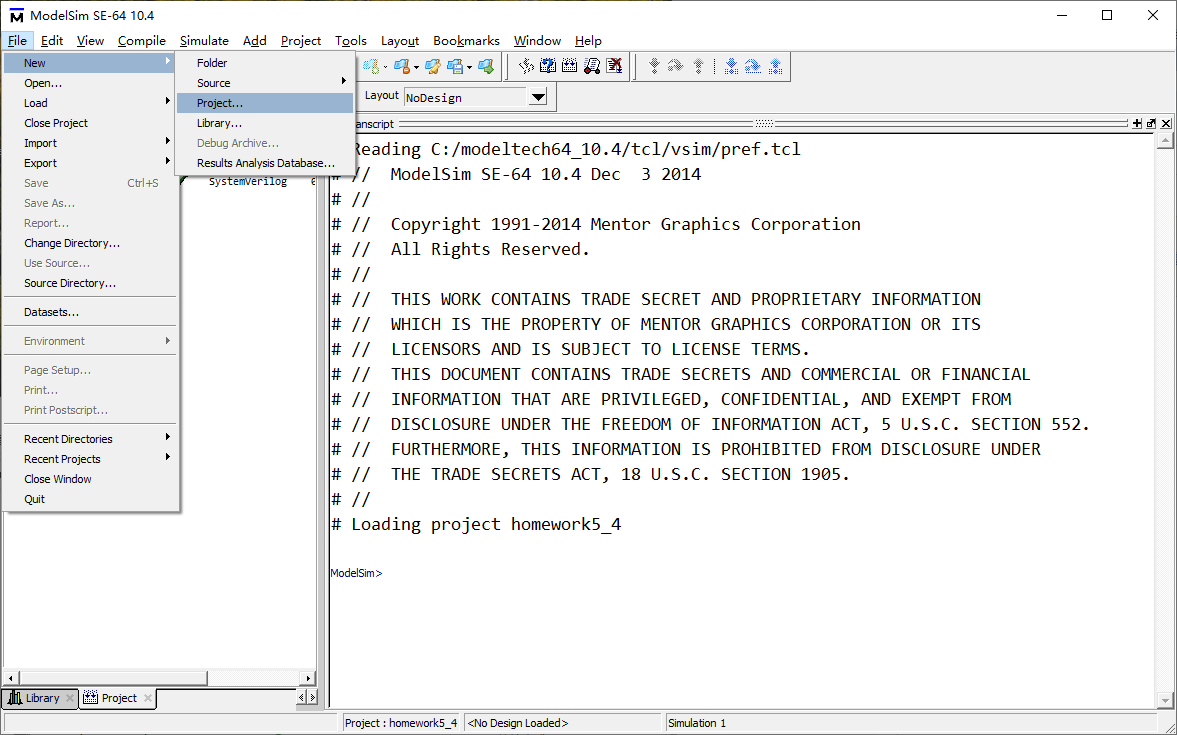

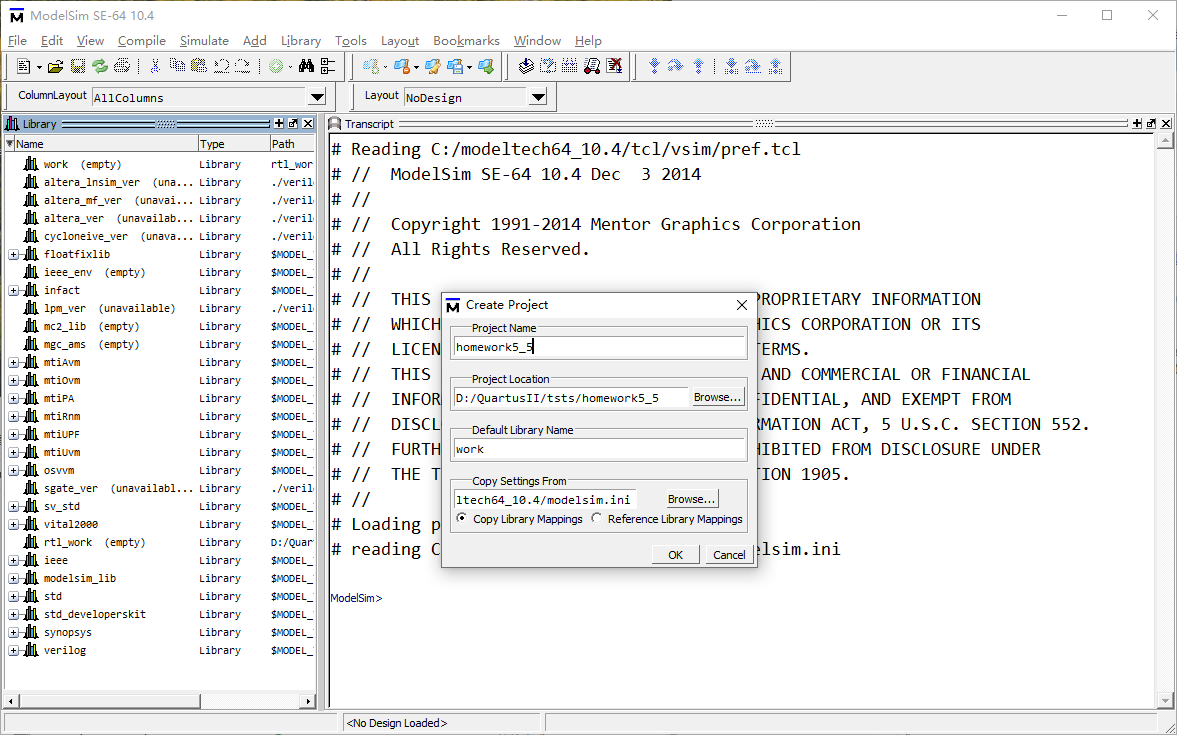

新建project

选择要使用的语言,这里使用systemverilog

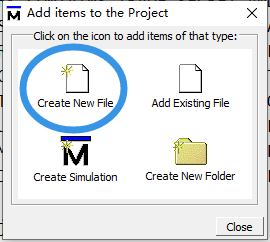

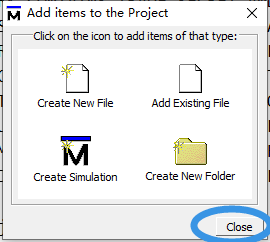

对于初学者,可以只使用一个文件编写主要模块和testbench(tb文件),所以这里直接关闭窗口

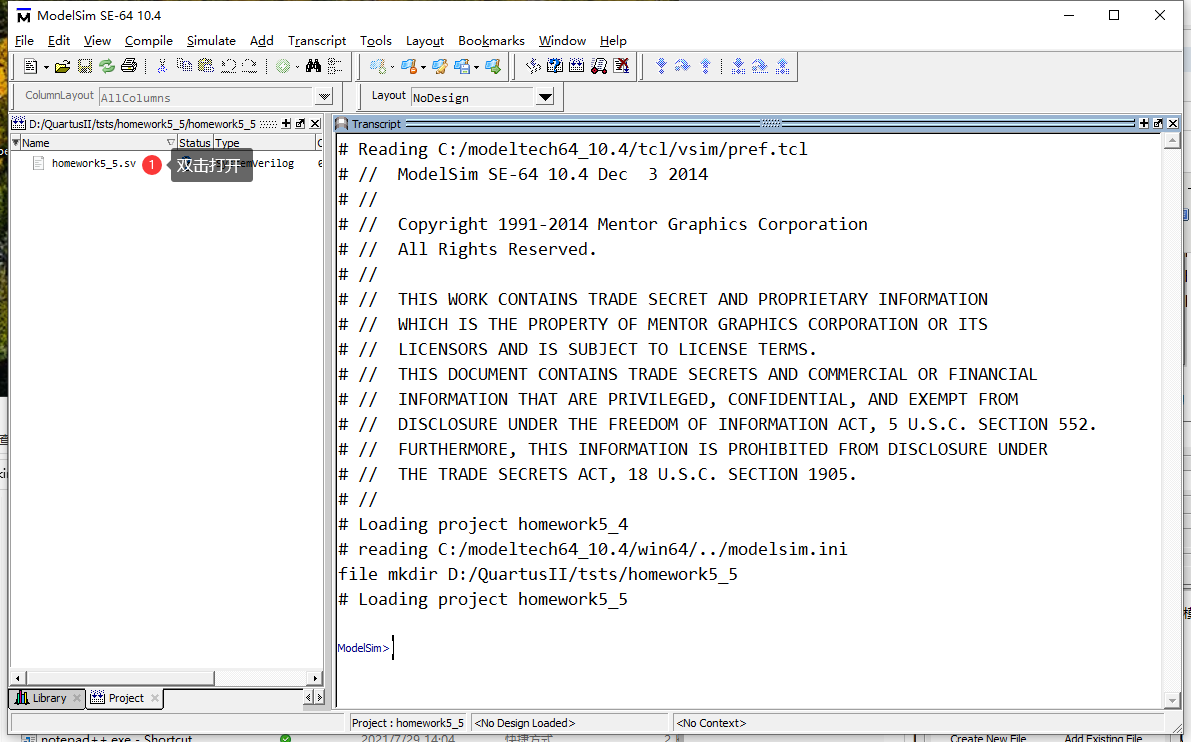

双击打开

填入测试代码

package definitions;

parameter version = "1.1";

typedef enum {ADD, SUB, MUL} opcodes_t;

typedef struct {

logic [31:0] a, b;

opcodes_t opcode; //opcode ADD, SUB MUL

} instruction_t;

typedef union {

logic [31 : 0] u_data;

logic signed [31 : 0] s_data;

} data_t;

endpackage

//import definitions::*;

module homework5_5(

// import definitions:: instruction_t IW,

input logic read,

output logic [31:0] result);

import definitions:: *;

enum logic {ON=1'b0, OFF=1'b1, HZ=1'bz, UN=1'bx} fo_st;

endmodule

`timescale 1 ns/ 1 ns

module homework5_5_tb();

logic read;//tb这里不要写input和output

logic [31:0] result;

// assign statements (if any)

homework5_5 i1 (//注意这里的引用要和主模块名称一致

// port map - connection between master ports and signals/registers

.read(read),

.result(result)

);

initial

begin

read=0;

result=0;

$display("variable");

end

always

begin

#10;

result++;

read+=2;

if ($time >= 1000) begin

$finish ;

end

end

endmodule

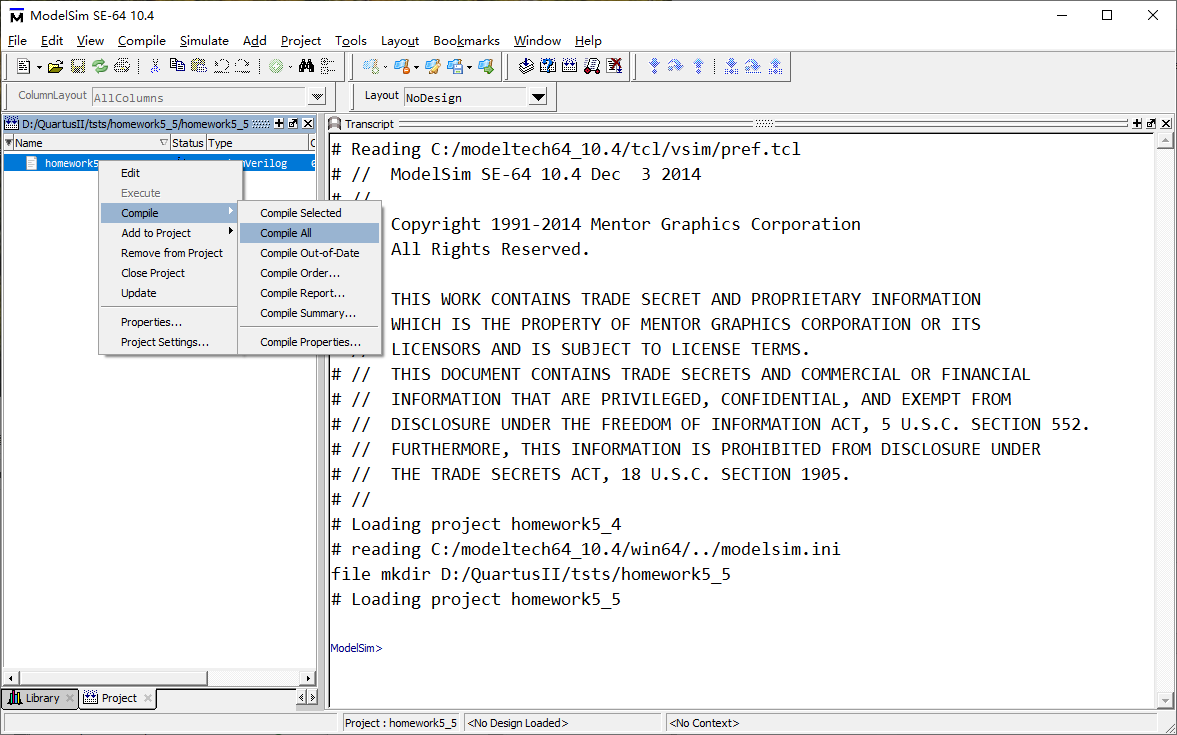

保存,右击,编译所有

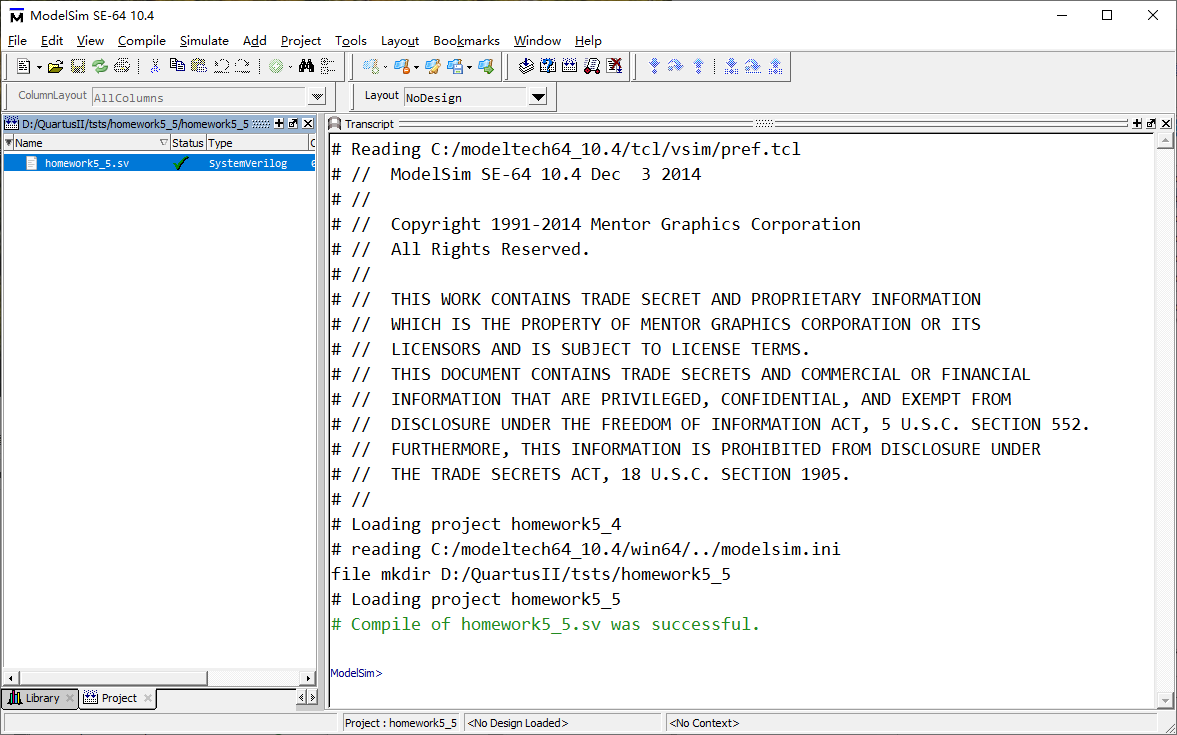

提示编译成功

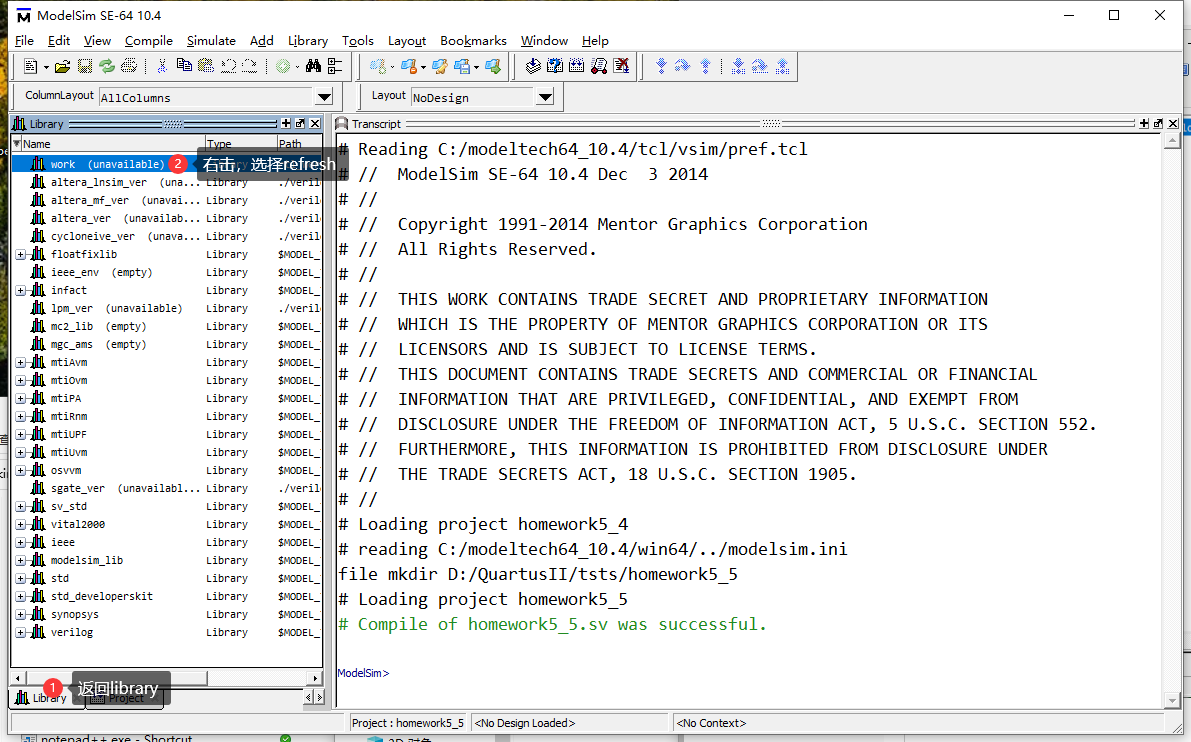

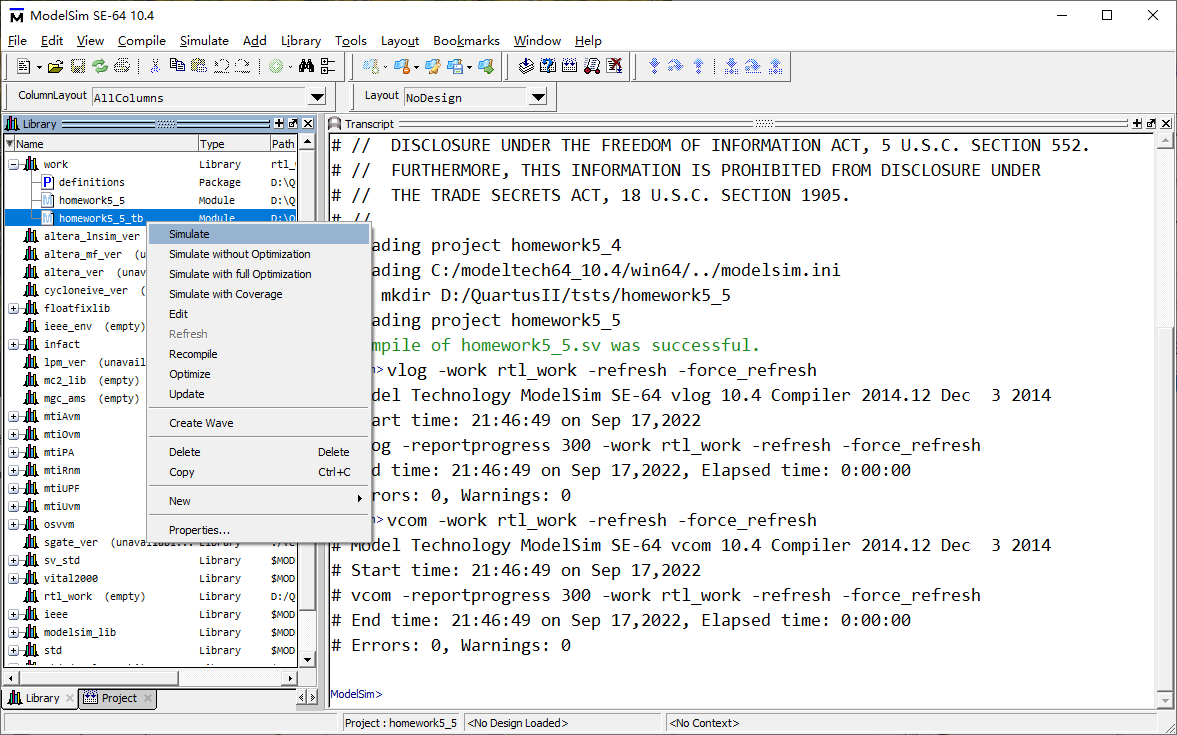

返回library,刷新工作区(如果不返回工作区刷新,有时候会报错Error loading design或者can't read "Startup(-L)": no such element in array)

右击tb模块,选择仿真(一定要选择tb模块来仿真,因为目的是为了测试)

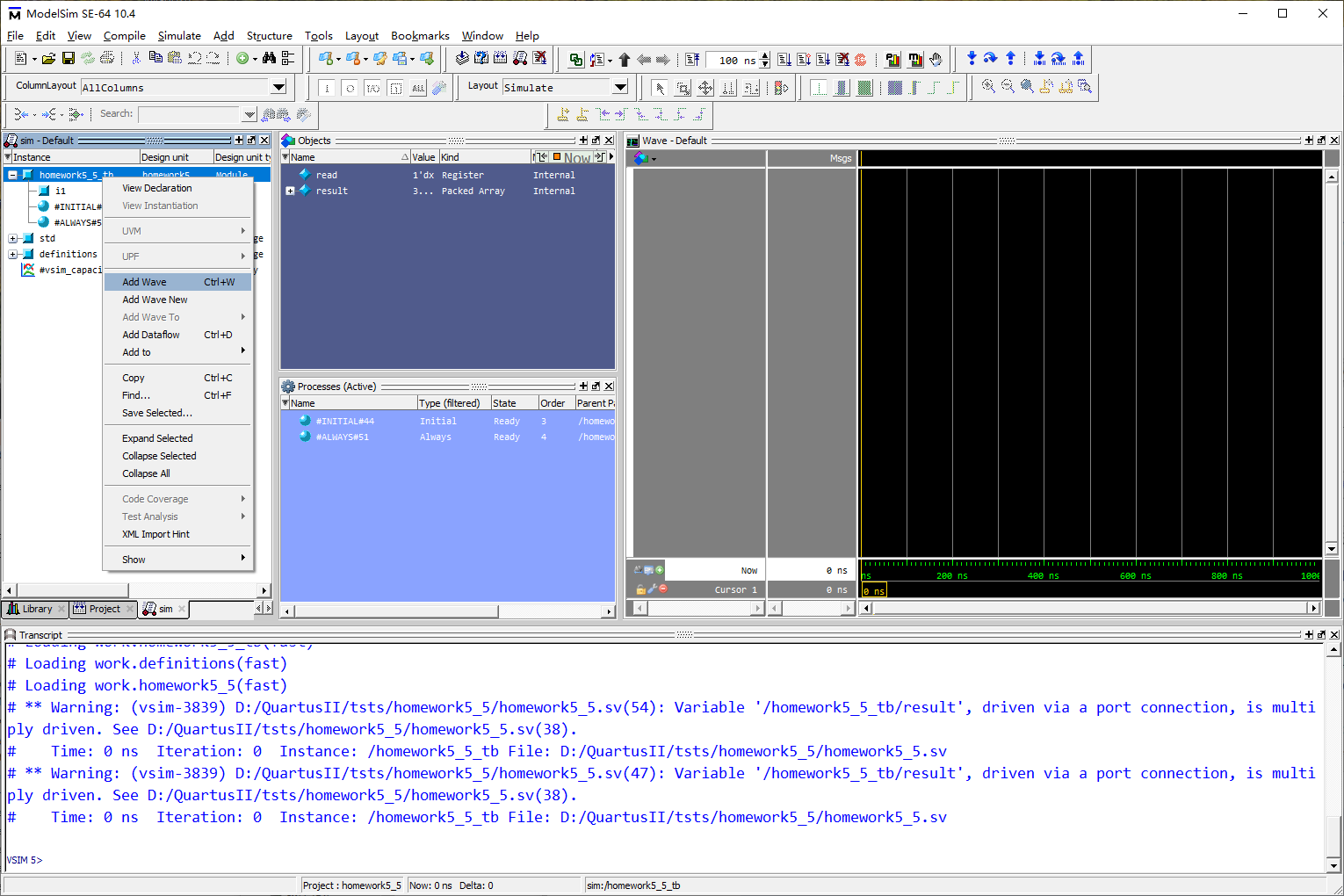

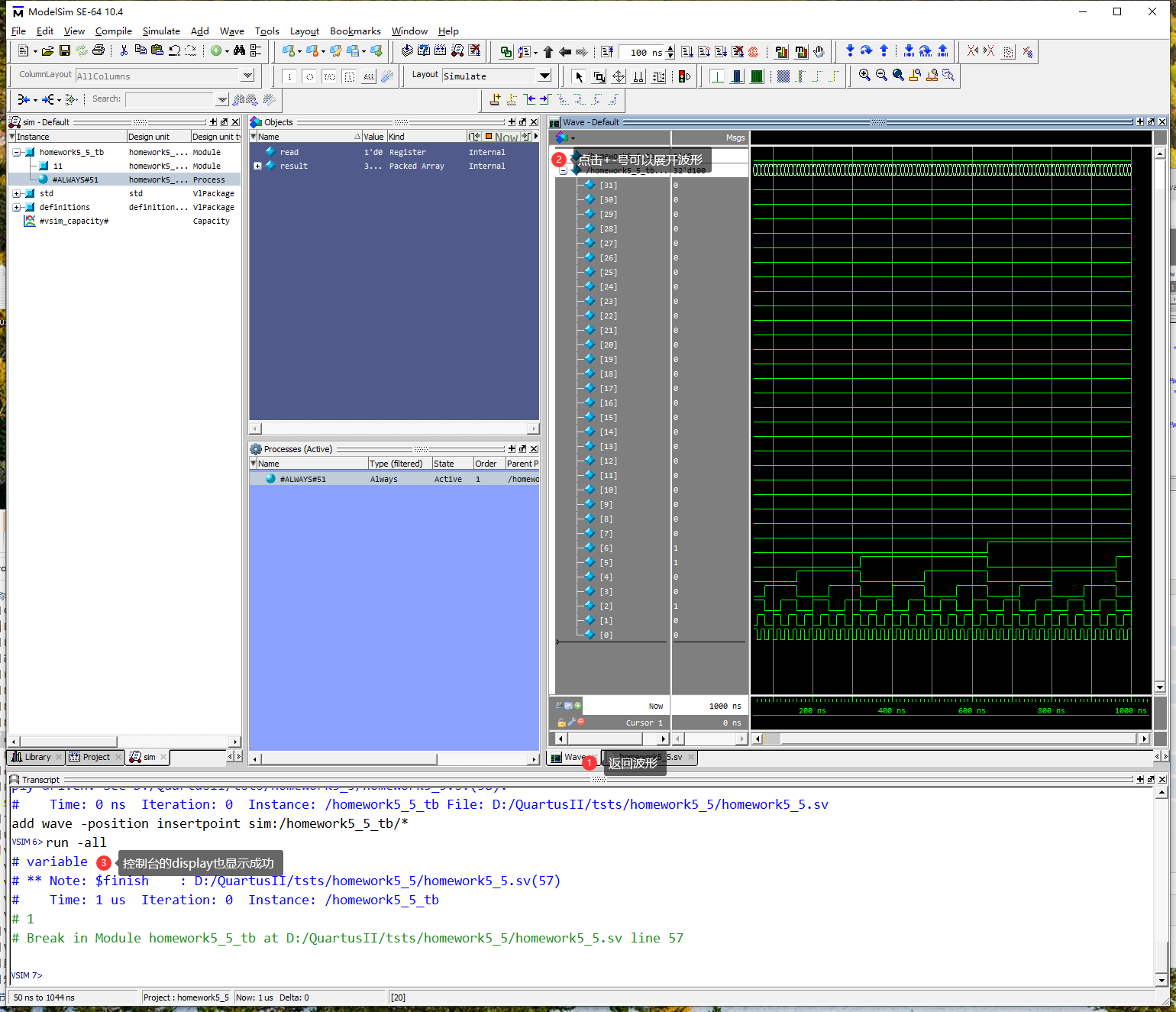

右击tb模块,添加波形

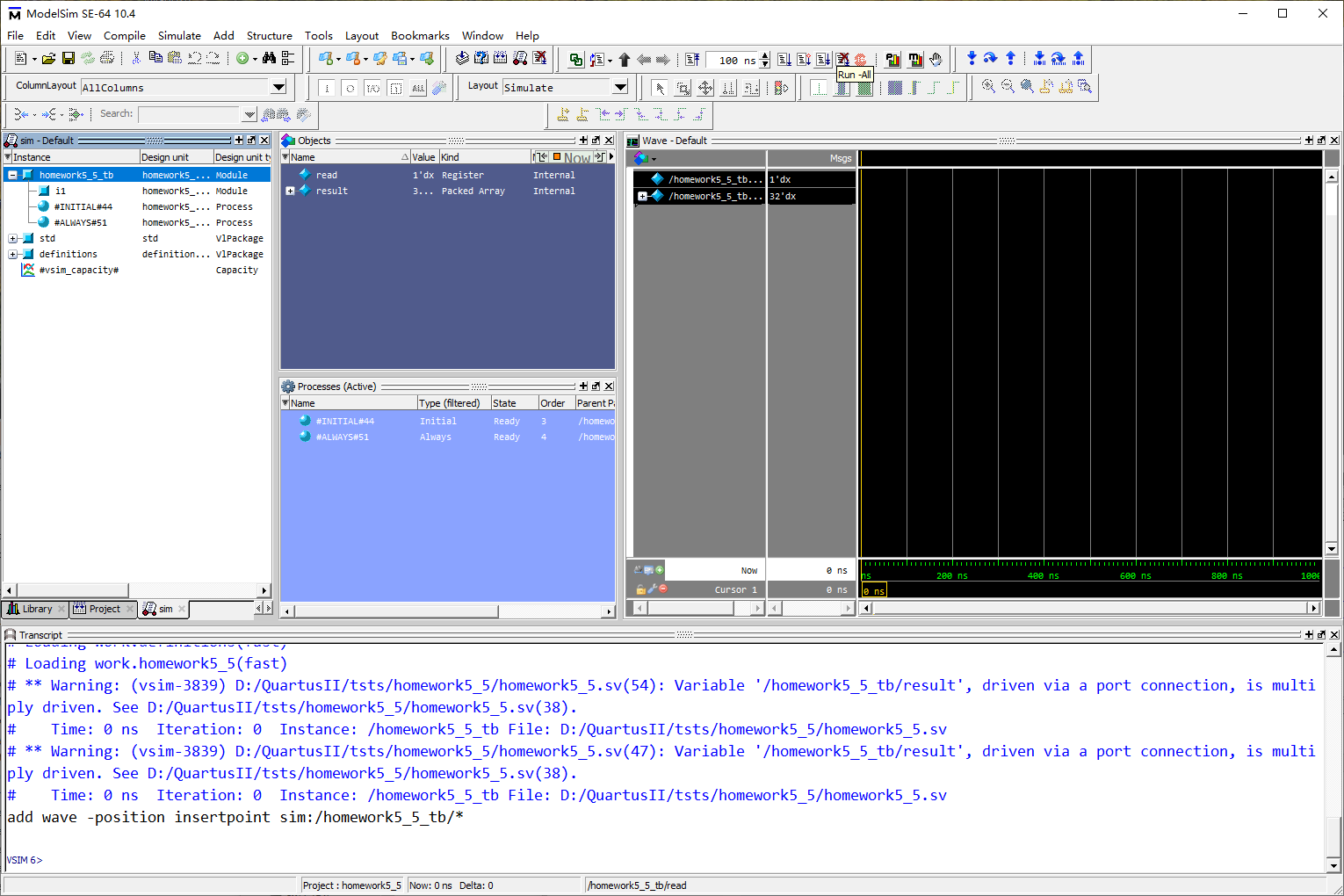

run-all

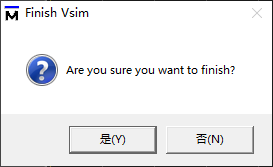

选择否

返回波形视图,查看仿真结果

版权声明: 本博客所有文章除特别声明外,均采用 CC BY-NC-SA 3.0 许可协议。转载请注明出处!

浙公网安备 33010602011771号

浙公网安备 33010602011771号