FGPA异步信号问题

FPGA在处理异步信号时,尽量打1~2拍寄存器,否则在线调试会发现各种奇怪问题。

下面是verilog代码

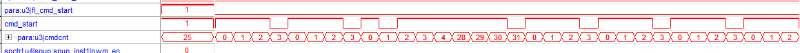

在线调试发现,计数器在跳变

原因是cmd_start由ARM输出,与FPGA时钟异步,需要打1~2拍寄存器

reg [5:0] cmdcnt; reg fl_cmd_start; reg cmd_start_0,cmd_start_1; //-----------------------cmd_start滤波------------------//(ARM输出持续580ns的脉冲) //cmd_start为异步信号,这里打两拍寄存器(ARM与FPGA时钟异步) always @(posedge clk_50m) begin cmd_start_0 <= cmd_start; cmd_start_1 <= cmd_start_0; end always@(posedge clk_50m or negedge rst_n) begin if(!rst_n) begin cmdcnt <= 6'd0; fl_cmd_start <= 0; end else begin if(cmd_start_1) begin if(cmdcnt==6'd24) fl_cmd_start <= 1'b1; cmdcnt <= cmdcnt + 1'b1; end else begin cmdcnt <= 6'd0; fl_cmd_start <= 0; end end end

这样修改后不会出现计数异常跳变

浙公网安备 33010602011771号

浙公网安备 33010602011771号