Advanced FPGA Design Architecture,Implementation and Optimization学习之复位电路

在日志http://www.cnblogs.com/qiweiwang/archive/2011/03/07/1975932.html和http://www.cnblogs.com/qiweiwang/archive/2010/11/25/1887888.html中,我们已经讨论过复位电路的设计。

1.完全异步复位的问题

完全异步复位在确立和释放触发器时都是异步的,这里异步复位指的是复位连线到触发器的异步复位引脚的情况。此外,复位的确立和释放是没有任何时钟的背景下执行的。

1: module resettff

2: (

3: output reg oData,

4: input iclk,iRst_n,

5: input iData

6: );

7:

8: always @ (posedge iclk,negedge iRst_n)

9: if(!iRst_n)

10: oData <= 1'b0;

11: else

12: oData <= iData;

13: endmodule

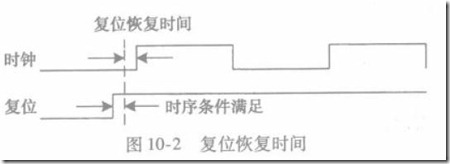

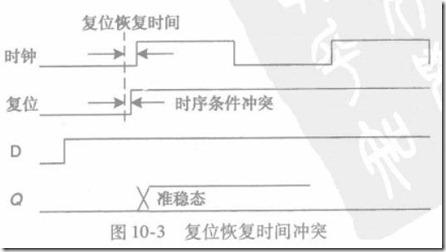

上面描述的电路最大问题是多半时间它会工作。但是,周期性复位释放的沿将十分接近下一个时钟沿,并与复位恢复时间冲突。这个复位恢复时间是一类在触发器上建立时序的条件,它定义复位释放和下一个上升时钟沿之间的时间量。

当复位在时钟上升沿之前适当的时刻被释放时,复位恢复条件被满足,如上图所示。

下图说明了复位恢复时间冲突,在输出端引起不稳定和一系列不可预测的行为。

重要的是要特别注意:复位恢复时间冲突只出现在复位释放的时刻,而不是出现在确立的时刻。

2.完全同步复位的问题

完全同步复位的代码是类似于对异步数据信号的双触发技术。

1: module resetsync 2: ( 3: output reg oData, 4: input iclk,iRst_n, 5: input iData 6: ); 7: 8: always @ (posedge iclk) 9: if(!iRst_n) 10: oData <= 1'b0; 11: else 12: oData <= iData; 13: endmodule

同步复位总是满足复位恢复时间,但是对复位的确立时间不敏感。

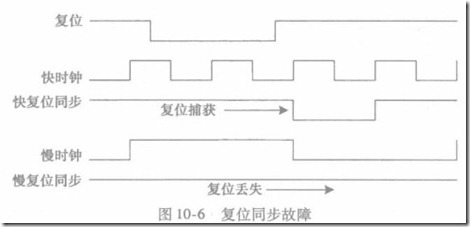

在时钟运行足够慢的情况下(或者时钟未打开),由于在复位信号确立期间不存在时钟的上升沿,复位没有被捕获,其结果是在这个状态的触发器从不复位。

完全同步复位可能捕获不到复位信号本身取决于时钟的特性。

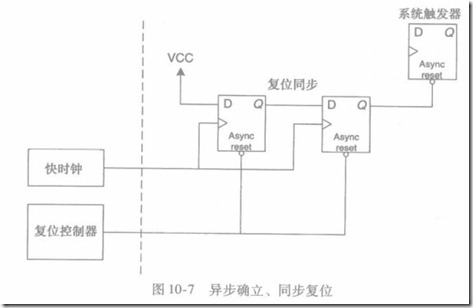

3.异步确立同步释放的复位

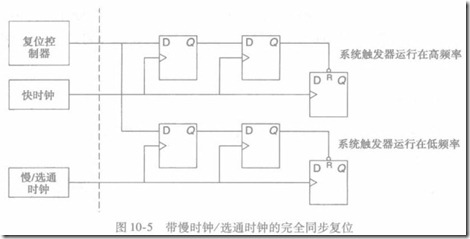

复位电路中的寄存器是通过外部信号异步复位,全部功能寄存器中同时复位,这个与时钟异步发生,时钟不需要在复位的时间运行。当外部复位释放,位于这个时钟区域的时钟在功能寄存器脱离复位之前必须触发两次。注意到,功能寄存器只在时钟开始触发和同步已经完成时才脱离复位。

module rstsync ( output reg sync_rst, input clk,rst_n, ); reg r1; always @ (posedge clk,negedge rst_n) if(!rst_n) begin r1 <= 1'b0; sync_rst <= 1'b0; end else begin r1 <=1'b1; sync_rst <=r1; end endmodule

路漫漫其修远兮,吾将上下而求索

浙公网安备 33010602011771号

浙公网安备 33010602011771号