Advanced FPGA Design Architecture,Implementation and Optimization学习之时钟区域

解决方案一:相位控制

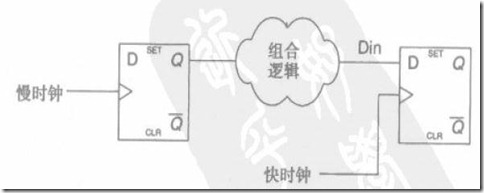

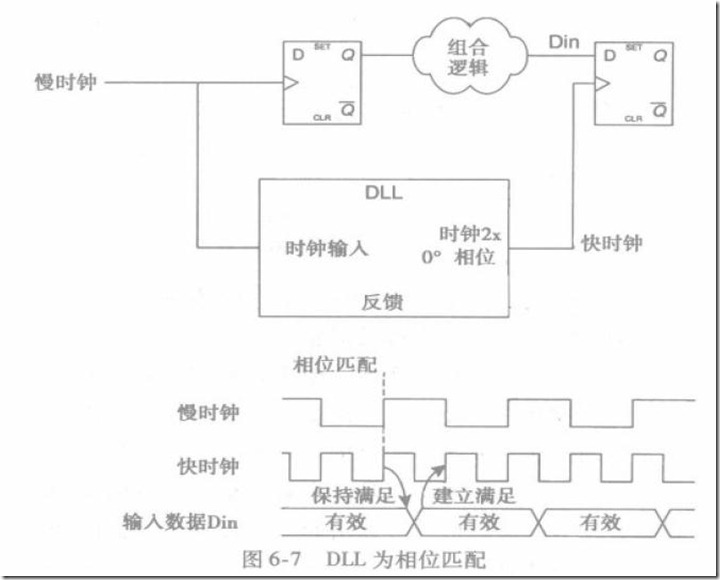

考虑到不同周期的有任意相位关系的两个时钟区域,如果其中至少一个时钟是在FPGA内部通过PLL(锁相环)或者DLL(延迟锁相环)可控制的,另一个时钟与在PLL或者DLL解决方案中那个时钟周期有倍数关系,那么相位匹配可以用来消除时序冲突。

信号由一个慢时钟区域向另一个周期是其一半的时钟区域传送,如果在时钟相位关系没有任何保障的前提下,时序就会发生冲突。然而,使用DLL或者PLL由第一个来驱动更快的时钟,那么就可以达到相位匹配。

当一个时钟的周期是另一个的整数倍的时候,并且其中一个时钟可以由内部PLL或者DLL控制时,就可以使用相位控制技术。

解决方案二:双跳技术

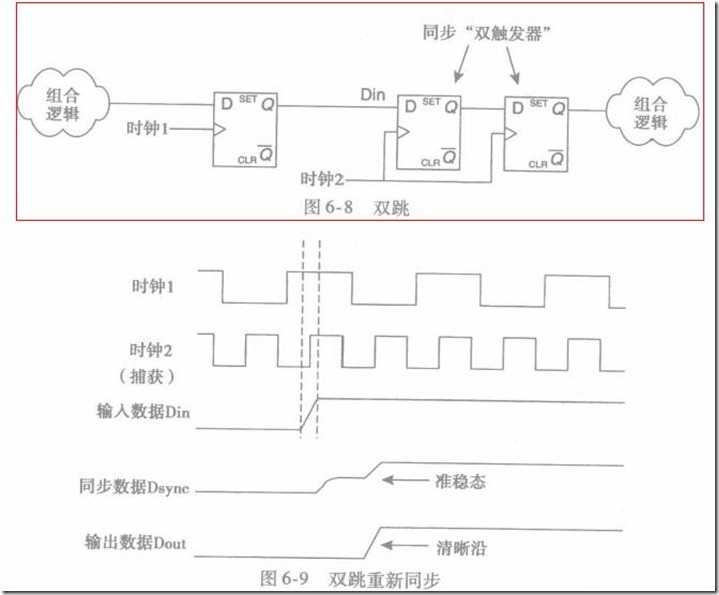

双跳技术是一项可以用于两个异步时钟区域之间单比特信号传输的技术。建立或者保持冲突可以引起触发器中的一个节点变到亚稳态,在信号稳定于有效电平之前,会有一个不确定数量的逗留时间存在。这个逗留时间会附加于时钟到输出时间之上,并且可能对下一级中引起时序冲突。

假设两个时钟区域是完全异步的,一个减小亚稳态发生概率的简单办法是使用双跳技术。

这里Dsync是第一个触发器而Dout是第二个触发器的输出。

双跳技术可以用于在两个异步时钟区域间对单比特信号进行再同步。

当利用双跳的方法时,最重要的是规定时序约束,使得第一和第二种时钟区域之间的信号通过在时序分析时不考虑,因为双触发结构重新同步化信号,在两个区域之间没有有效的同步通道。此外,在触发器之间的时序应该最小化,以减少准稳定状态通过第二个触发器传播的概率。

时序分析应该不管第一个重新同步的触发器,并保证在同步触发器本身之间的时序是最小的。

解决方案三:FIFO结构

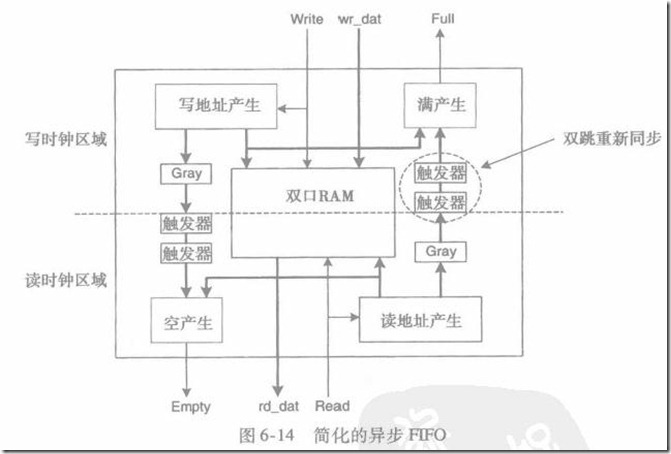

在时钟区域之间传递信号更灵活的方式是使用FIFO结构。当在异步时钟区域之间传递多位信号时可以利用FIFO。FIFO最通常的应用包括在标准总线接口之间传递数据和读写突发存储器。

在FPGA中的FIFO一般用围绕双口RAM的包装来实现的。

格雷码可以利用在异步时钟区域之间传递多位计数器的数据,常常利用在FIFO内部。

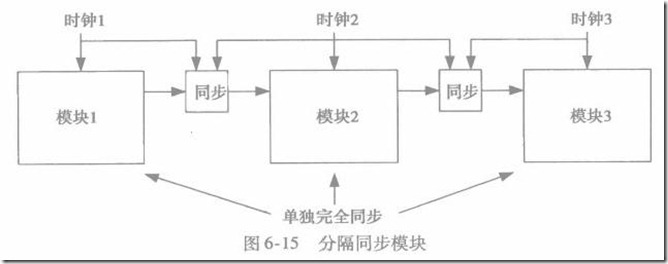

解决方案四:分割同步模块

同步寄存器应该分割为功能模块外部的独立模块。

浙公网安备 33010602011771号

浙公网安备 33010602011771号