如何用ModelsimSE仿真IP核-以PLL为例

我们之前介绍了如何使用Modelsim SE进行仿真和利用do文件的仿真方法,但是其中待仿真的模块是我们自己编写的Verilog模块,但是在实际工作中,我们的设计中会经常用到FPGA厂商给我们提供的现成模块—IP核,这些模块我们看到不到源代码,只知道IP核的端口信息,当我们要仿真的时候,同样要向Modelsim提供这些IP核的信息,而FPGA厂商也会给我们提供相应的IP核的编译库文件,我们如果设计中包含这些IP核,就必须在仿真之前,将这些库文件编译到Moldelsim 的库中去。其实IP核只是我们要添加的其中一种库(MegaFunction),除此之外,我们还需要添加lpm库(设计中如果调用了lpm原件,需要添加此库),还有原语库(primitive),器件库(我们用的是cyclone),当然同一种库,还会分Verilog版和VHDL版。这里只介绍Verilog版相关库文件的添加,VHDL版的,方法类似,大家只需更换相应的VHDL编译文件即可。

1.1.1.建立仿真库

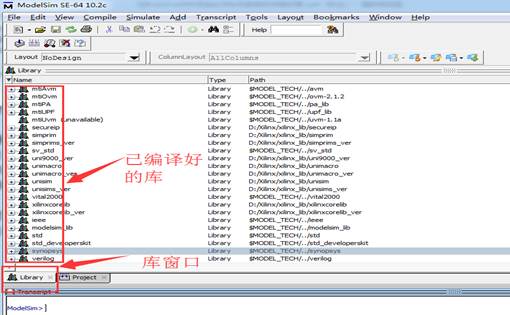

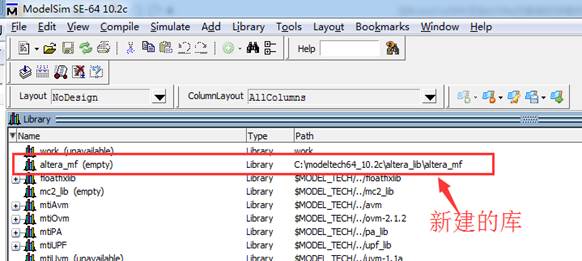

我们将IP核等相关库文件编译到Modelsim中后,以后凡是设计中调用到IP核时,我们就不用再重复添加了。我们看一下如何在Modelsim中查看我们已经编译好的库,打开modelsim,如下图,会默认弹出名为library的窗口,窗口中的内容就有我们已经添加的库,一部分是Modelsim自带的库。

下面我们开始准备添加相关库文件。

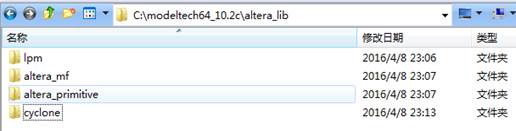

第一步,首先在新建一个文件夹,用来存放我们编译后的库文件,这里命名为altera_lib,我们这里存放到了“C:\modeltech64_10.2c\”路径下,然后在altera_lib下新建四个文件夹lpm、altera_mf、altera_primitive、cyclone,如下图,后面我们会建立四个对应且相同名称的库。

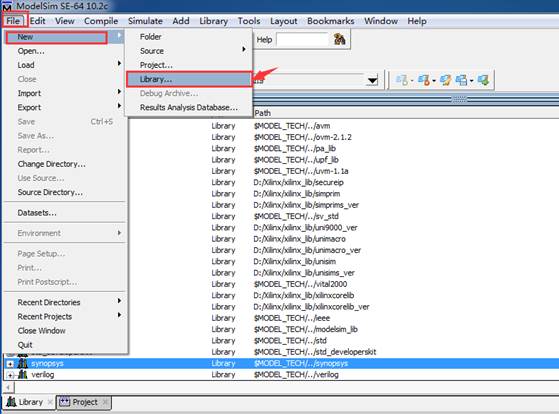

第二步,建立库,我们以添加IP核库文件(altera_mf)为例进行介绍。首先打开Modelsim,选择菜单 File—>New—>Library。这里我们介绍一下“库”的概念,库实际就用来存放编译结果的一个文件夹,他最终都和我们实际硬盘上的物理空间的文件夹是一一对应的,在第五章我们提到过工作库(work库),存放的是我们自己设计文件的编译结果。

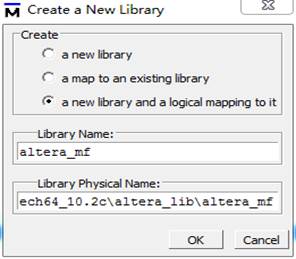

第三步,弹出新建库的窗口,我们选择第三项“a new library and a logical mapping to it”,即创建一个新库,并映射到我们硬盘的相应路径下。Library

Name填写相应的库名称“altera_mf”,Library Physical Name中填写我们第一步中新建库对应文件夹的存放路径。这里altera_mf对应文件夹路径为“C:\modeltech64_10.2c\altera_lib\altera_mf”。然后点击确定。

第四步,在modelsim的library窗口下,大家可以看到新建的altera_mf库,不过此时库文件为空的。如下图。

第五步,编译相应文件到库中,我们这里需要将相关IP核文件编译到altera_mf库中去。菜单栏选择compile—>compile…,弹出如下窗口,首先选择待编译的库library,这里选择我们刚新建的库“altera_mf”,然后找到在quartus安装目录下,找到Altera提供的关于altera IP核的编译文件altera_mf.v,路径为“altera\13.1\quartus\eda\sim_lib”。最后点击compile,完成编译后,关闭。此时可以看到library窗口下,altera_mf库不再是一个空的库。

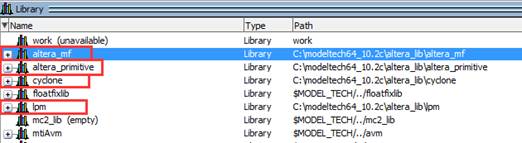

第六步,重复2-5步,依次建立lpm、altera_primitive、cyclone三个库。对应的编译文件依次是220model.v(lpm)、altera_primitives.v(altera_primitive)、cycloneiv_atoms.v(cyclone库,这里我们只添加了cyclone4的库文件)。添加完成后可以在library中看到四个库,如下图。

第七步,找到Modelsim安装路径下的modelsim.ini文件,去除文件的只读属性,然后打开, 将上一步中的四个库的名称及路径以下图的方式,添加到57行后。关闭文件,再设置为只读属性。注意路径是反斜杠。

至此,我们已经将altera相关的库文件添加到了Modelsim SE中了。后面,我们将介绍如何通过do文件启动仿真。

1.1.2. 原理介绍

介绍PLL IP核建立之前,我们先讲一下PLL的基本原理。PLL是Phase-Locked Loop的缩写,中文含意为锁相环。PLL基本上是一个闭环的反馈控制系统,它可以使PLL输出与一个参考信号保持固定的相位关系。PLL一般由鉴相器、电荷放大器(Charge Pump)、低通滤波器、(电)压控振荡器、以及某种形式的输出转换器组成。为了使得PLL的输出频率是参考时钟的倍数关系,在PLL的反馈路径或(和)参考信号路径上还可以放置分频器。PLL的功能示意图如下图所示:

首先大家要理解什么是压控振荡器(VCO),压控振荡器实际就是一个:频率—电压转换器。当VCO输入的电压变化时,对应输出的频率也会发生变化。PLL的工作原理就是将VCO输出的频率经过分频器返回到输入端,将分频信号与原始输入的信号鉴相,鉴相器输出又通过电压放大器和低通滤波器并转换成电压,这样就调整了VCO的输入电压,从而调整了VCO的输出频率,然后这样循环调整,最终将输出频率锁定。

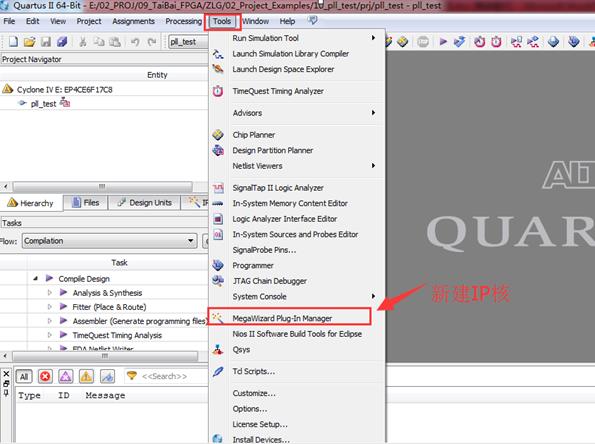

1.1.3. 建立IP核

第一步:按照2.4.2节的方法新建pll_test工程,这里我们就不重复了,新建好工程以后。选择菜单栏Tools—>MegaWizard Plug-In Manager。其中MegaWizard就是Quartus的IP核建立向导工具,我们通过这个工具建立我们需要的IP核。

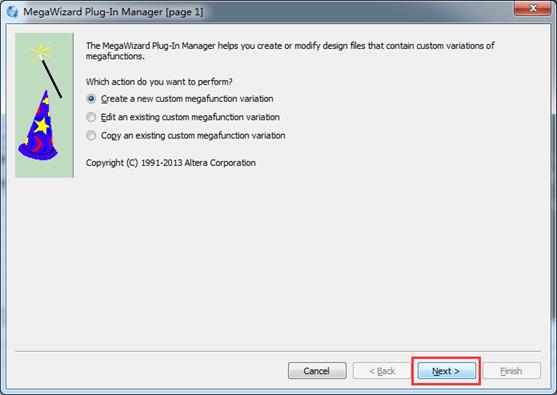

第二步:弹出如下对话框,选择“Create a new custom megafunction variation”创建一个新的IP核。点击Next。

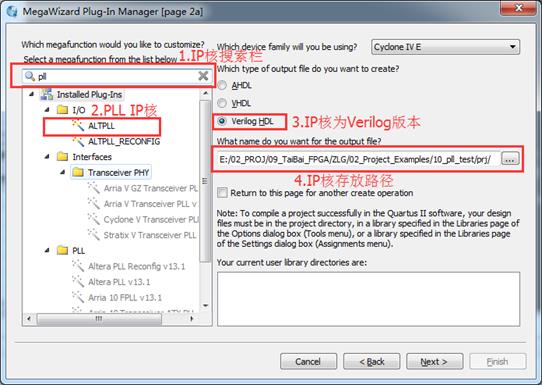

第三步:弹出如下对话框,首先介绍一下IP核搜索栏,我们可以通过这个地方快速查找到需要的IP核的位置,我们输入pll,便可以迅速找到PLL的IP核,ALTPLL,如下图。这里生成IP核文件,我们选择为Verilog。

第四步:点击IP核存放路径后面的![]() ,选择存放路径,如下图,我们存放至src/ip文件夹下,这里必须要在文件名处填写IP核对应输出文件的名称,这里我们定义为pll.v。然后点击“打开”,回到第三步窗口,继续Next。

,选择存放路径,如下图,我们存放至src/ip文件夹下,这里必须要在文件名处填写IP核对应输出文件的名称,这里我们定义为pll.v。然后点击“打开”,回到第三步窗口,继续Next。

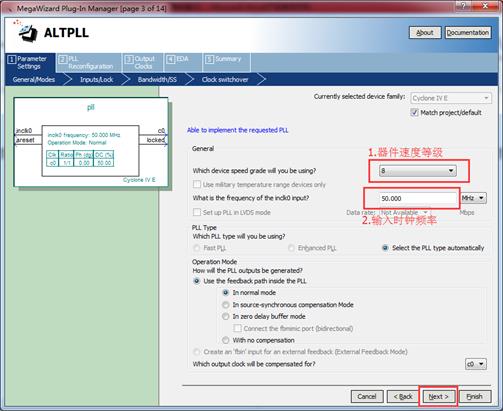

第五步:此时会弹出PLL

IP核的配置窗口。首先设置器件的速度等级,我们所用器件速度等级为8。速度等级数值越小,对应的FPGA速度越快。然后设置PLL的输入频率,这里我们设置为50MHz,其他默认。点击Next。

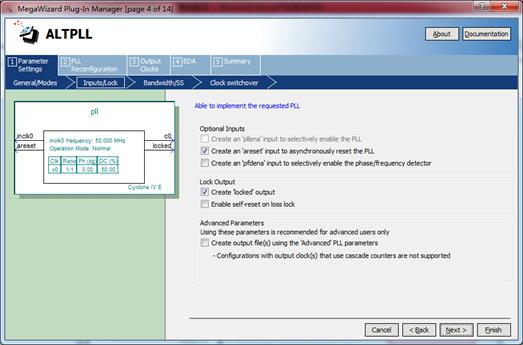

第六步:弹出如下对话框,保持默认选项,即创建一个异步输入信号,注意这个复位信号是高电平有效的,创建一个PLL锁定locked信号。继续Next。

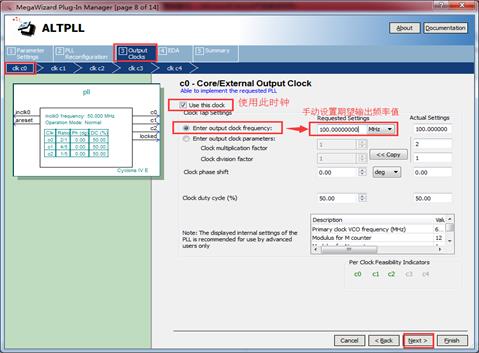

第七步:一直点击Next,中间过程配置保持默认,直到选项卡为Output Clocks—>clk c0时,表示对pll输出时钟进行配置,clk c0的“use this

clock”选项是默认选上的。选择“Enter output clock frequency”,在“Requested Settings”下设置好期望输出的时钟频率,这里clk c0设置为100MHz。然后点击Next。

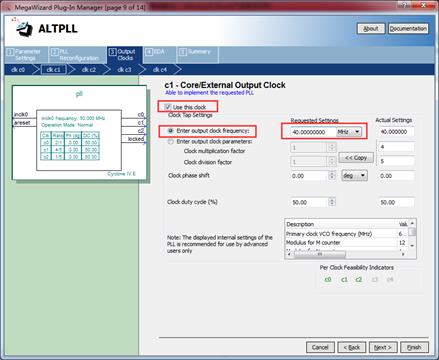

第八步:弹出同样窗口,这里我们需要,手动选择“use this clock”,同样方法创建clk

c1 为40MHz时钟,clk c2为10MHz时钟。c3、c4不启用。

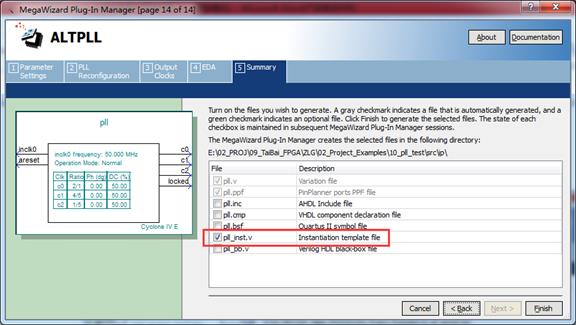

第九步:继续Next,中间过程保持默认,一直到Summary选项下时,可以选择实际输出的文件,这里pll.v是必须的,这个文件是将来我们仿真时,IP的编译文件。其次,我们选择pll_inst文件,这个文件为pll的例化文件,我们可以直接从该文件中将pll的例化结果拷贝到相应的应用逻辑中。最后点击Finish。

第十步:调用IP核,首先新建顶层文件,pll_test.v文件,参考src文件夹下源文件。找到src/ip路径下pll_inst.v文件,打开。将其中的例化例子拷贝至顶层文件中。根据顶层IO信息调整pll的例化端口。代码如下。

1. module pll_test

2. (

3. input i_clk ,//模块输入时钟 ,50mhz

4. input i_rst_n ,//复位信号,低电平有效

5. output o_clk_100MHz , //100MHz 时钟输出

6. output o_clk_10MHz , //40MHz

时钟输出

7. output o_clk_40MHz , //10MHz

时钟输出

8. output o_led_done //LED亮,时钟LOCK

9. );

10. wire w_pll_lock ;

11. pll pll_inst (

12. .areset ( !i_rst_n ),

13. .inclk0 ( i_clk ),

14. .c0 ( o_clk_100MHz ),

15. .c1 ( o_clk_10MHz ),

16. .c2 ( o_clk_40MHz ),

17. .locked ( w_pll_lock )

18. );

19. assign o_led_done =!w_pll_lock;

20. endmodule

至此,我们完成了整个IP核建立及调用过程,下一节我们介绍IP核的仿真。

1.1.4. 启动仿真

2.10.1节中已建立好仿真库,以后再仿真任何IP核时,都不用再重复2.10.1节的操作。现在,我们只需要简单修改一下do文件的内容,就可以直接通过do文件启动仿真了。下面是本节的sim.do文件内容。

21. vlib work

22. vmap work work

23. vlog ../sim/*.v

24. vlog ../src/*.v

25. vlog ../src/ip/pll.v

26. vsim -t ps -novopt-L lpm -L altera_mf -L cyclone -L altera_primitive work.tb_pll_test

可以看出,本节的sim.do文件的vsim指令后比我们之前实验的vsim指令多了几个选项-L lpm -L altera_mf -L cyclone-L altera_primitive,这几个选项实际就把我们2.10.1节中建立的4个库,添加到我们的仿真中去,-L 表示库,紧跟着的是相应的库的名称。其次-t表示仿真时间单位,这里我们需要将仿真的时间单位调整为ps,否则PLL仿真没有波形。需要注意的是在编译IP核的生成文件时,只编译pll.v即可,我们之前生成的pll_inst.v文件不要编译。否则会报错。

修改完上述几项后,我们再双击modelsim_run.bat文件,我们就可以启动仿真,并看到我们的放真波形。

posted on 2016-04-21 22:01 SevenFormer 阅读(3928) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号