【自学嵌入式:stm32单片机】SPI通信外设

SPI通信外设

SPI通信外设简介

-

STM32内部集成了硬件SPI收发电路,可以由硬件自动执行时钟生成、数据收发等功能,减轻CPU的负担

-

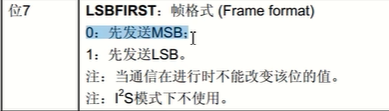

可配置8位/16位数据帧、高位先行/低位先行(最常用的是8位数据帧,高位先行)

-

时钟频率: \(f_{\text{PCLK}} / (2, 4, 8, 16, 32, 64, 128, 256)\) (这些数字是分频系数)

-

支持多主机模型、主或从操作

-

可精简为半双工/单工通信(单工就是单独拿掉发送数据线或者单独拿掉接收数据线)

-

支持DMA

-

兼容I2S协议(数字音频传输协议)

-

STM32F103C8T6 硬件SPI资源:SPI1、SPI2,SPI1挂载在APB2,PCLK是72M,SPI2挂载在APB1,PCLK是36M

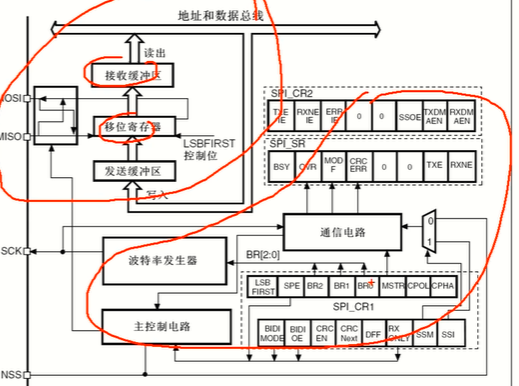

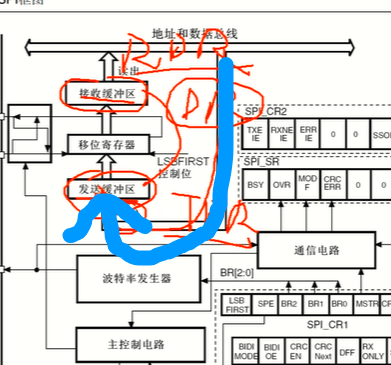

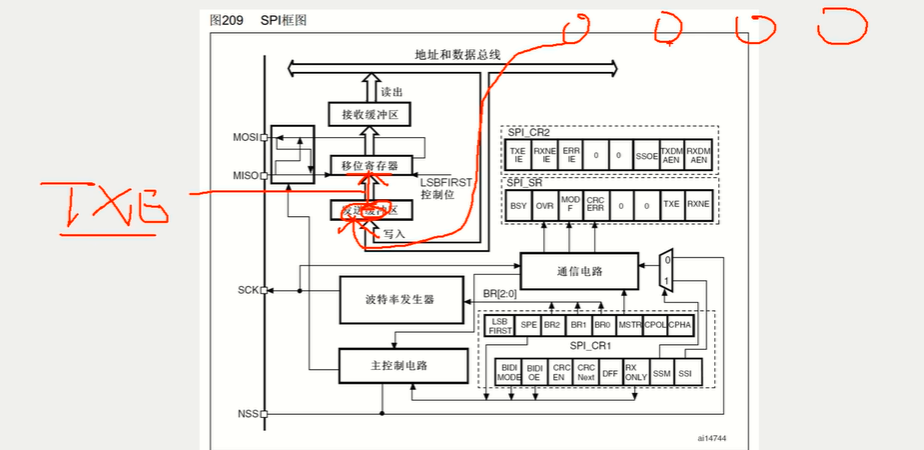

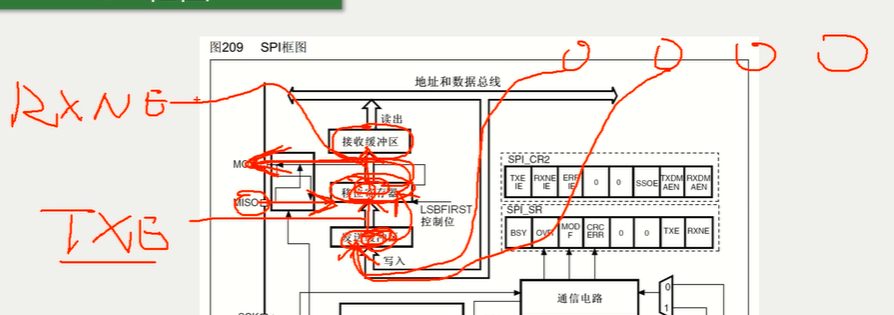

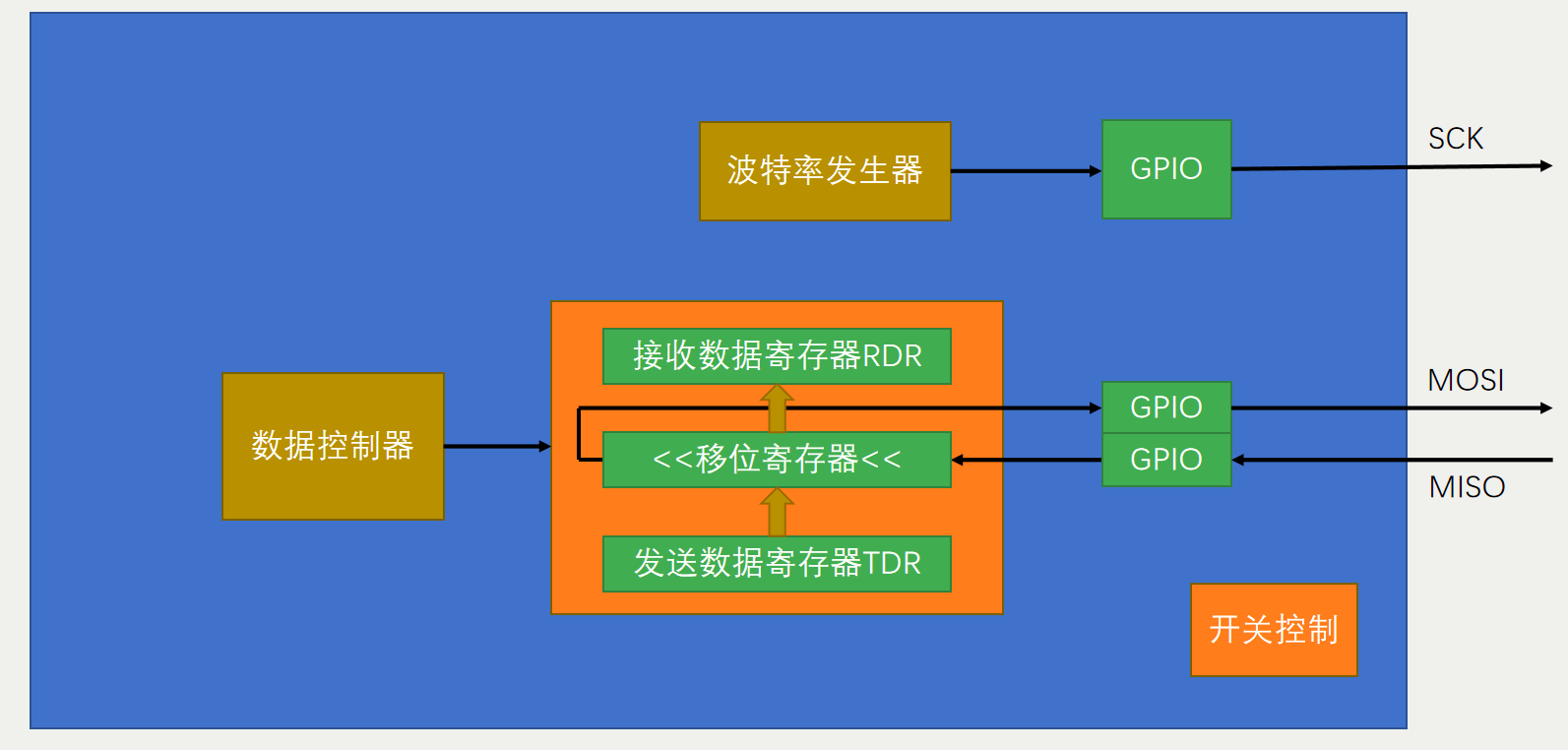

SPI框图

如上图,左上角这部分是数据寄存器和移位寄存器配合的过程,和之前的硬件I2C的框图类似。

右下角这部分是控制逻辑,寄存器的哪些位,控制哪些部分,会产生哪些效果,可以参照手册。

数据寄存器和移位寄存器配合的过程

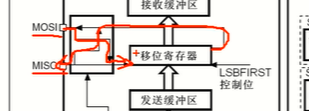

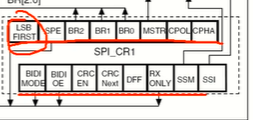

先看移位寄存器,数据一位一位地从MOSI移出去,然后MISO的数据一位一位地移入左边的数据高位,达到一种交换数据的效果,图上展示的是一种低位先行的状态,LSBFIRST控制位可以控制是低位先行还是高位先行,高位先行就是输出从左边移出去,输入用右边移进来

MSB是高位的意思,LSB是低位的意思

这里MOSI和MISO做了个交叉,这一块主要是用来进行主从模式引脚变换的,这个SPI外设可以做主机也可以做从机,做主机时,这个交叉就不用,做从机时候,启用交叉连接,MOSI就变成从机输入,走输入那一路。MISO编程从机输出,走输出那一路,如下图:

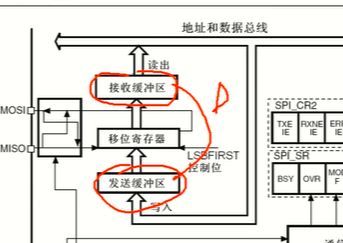

这两个缓冲区,实际上就是接收数据寄存器RDR和发送数据寄存器TDR,和之前硬件I2C的数据缓冲区类似,和串口那里意义,TDR和RDR占用同一个地址,统称为DR

写入DR时,数据从上图蓝色指示的方向,写入到TDR,读取DR时,数据从RDR读出,数据寄存器和移位寄存器打配合,可以实现连续的数据流

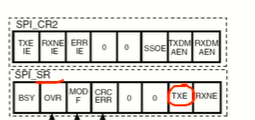

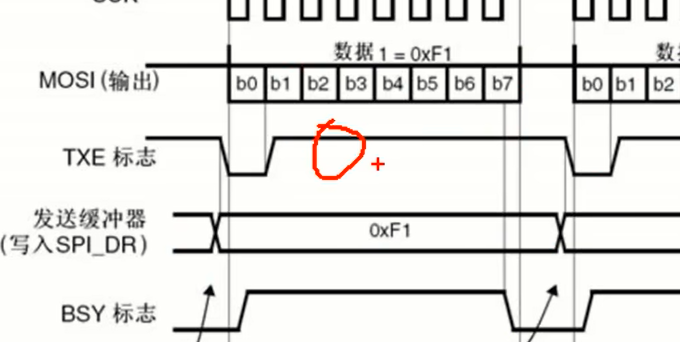

具体流程就是,比如我们需要连续发送一批数据,第一个数据写入到TDR,当移位寄存器没有数据移位时,TDR的数据会立刻转入移位寄存器,开始移位,这个转入时刻,会置状态寄存器的TXE为1,表示发送寄存器为空,当检查TXE置1后,紧跟着,下一个数据,就可以提前写入到TDR里候着了,一旦上一个数据发完,下一个数据就可以立刻跟进,实现不间断的连续传输,然后移位寄存器这里,当数据过来了,它就会自动产生时钟,将数据移出去

在移出的过程中,MISO的数据也会移入,一旦数据移出完成,数据移入也完成,这时,移入的数据就会整体地从移位寄存器转入到接收缓冲区RDR,这个时刻,会置状态寄存器的RXNE为1,表示接收寄存器非空,当我们检查RXNE置1后,就要尽快把数据从RDR读出来,在下一个数据到来之前,读出RDR,就可以实现连续接收,否则下一个数据已经收到的清空下,上一个数据还没从RDR中读出来,那RDR的数据就会被覆盖

控制逻辑

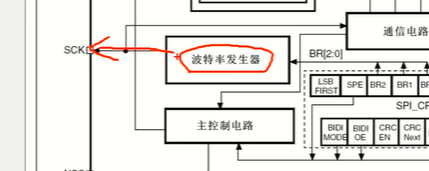

波特率发生器用来产生SCK时钟,其内部就是一个分频器,输入时钟是PCLK,72M或36M,经过分频器之后,输出到SCK引脚,当然这里生成的时钟肯定是和移位寄存器同步的了,每产生一个周期的时钟,移入移出一个bit

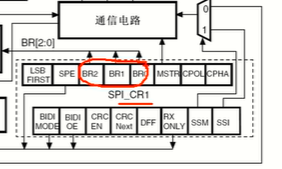

然后右边,CR1寄存器的三个位BR0、BR1、BR2,用来控制分频系数,

LSBFIRST,决定高位先行还是低位先行;SPE(SPI ENABLE)是SPI使能,就是SPI_Cmd函数配置的位;BR(Baud Rate)配置波特率,就是SCK时钟频率,MSTR(Master)配置主从模式(1是主模式,0是从模式,一般用主模式),CPOL和CPHA,这个之前讲过,用来选择SPI的4种模式

然后这里SR状态寄存器,最后两位,TXE位发送寄存器空,RXNE接收寄存器非空,CR2寄存器都是一些使能位,中断使能DMA使能等等...

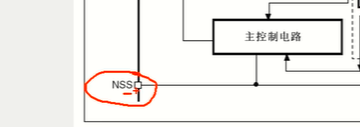

最后这里有个NSS引脚,SS就是从机选择,低电平有效,所以这里前面加了个N,这里的NSS更偏向于实现多主机模型,这个NSS不会用到,SS引脚我们直接使用一个GPIO模拟就行

SPI基本结构

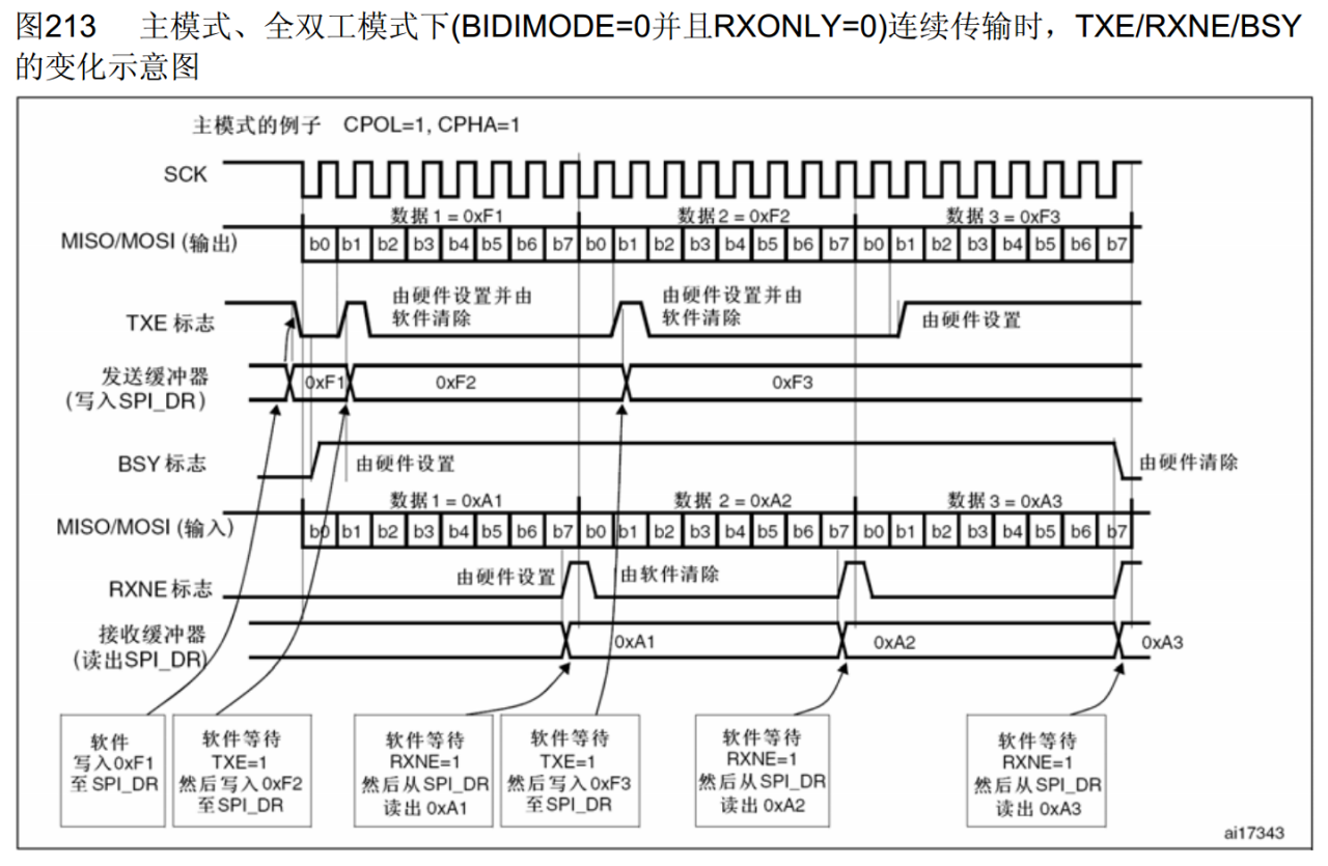

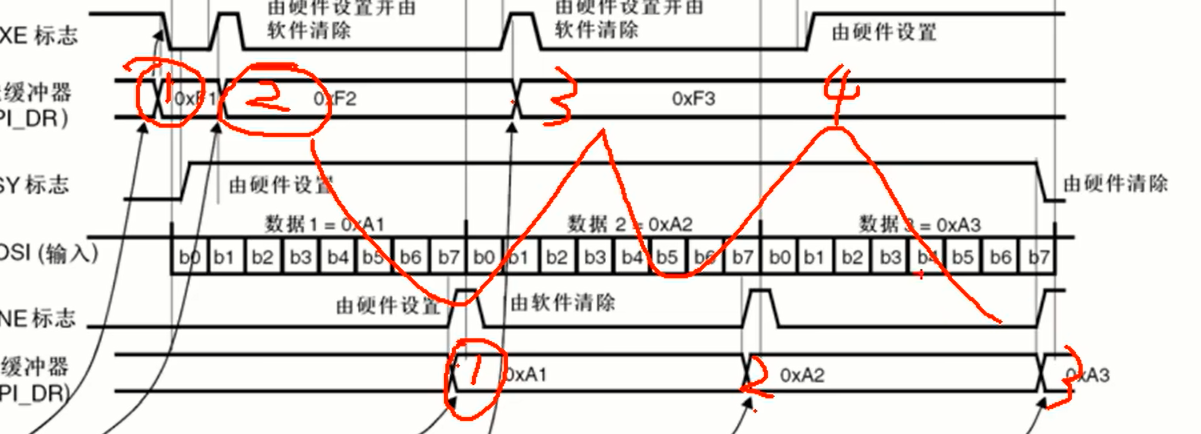

主模式全双工连续传输

CPOL = 1,CPHA = 1,使用SPI模式3,这里演示的是低位先行的模式

这个传输效率高,但是比较复杂,不利于封装,实际上用非连续输出

这个发送的是交错的,发送数据2后才接收数据1。

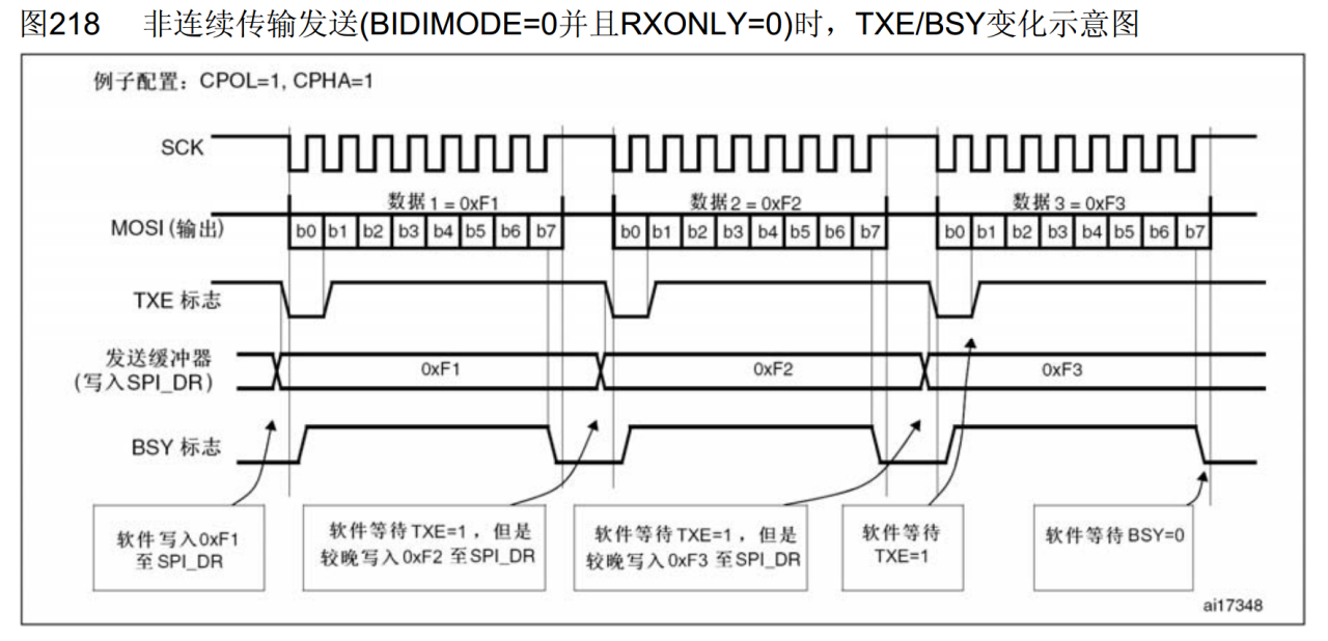

非连续传输

它的缺点是在这个位置没有及时把下一个数据写入TDR等着,所以等到第一个字节时序完成后,第二个字节还没有送过来,那数据传输就会在这里等着,所以这里时钟和数据的时序在字节和字节之间会产生间隙,拖慢了整体数据传输的速度,这个间隙,在SCK频率低的时候,影响不大,但是在SCK频率非常高时,间隙拖后腿的现象,就比较严重了

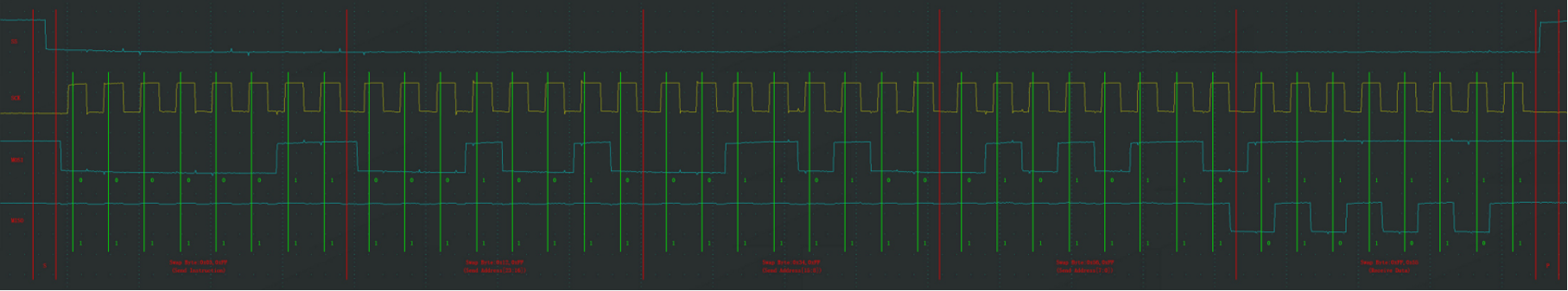

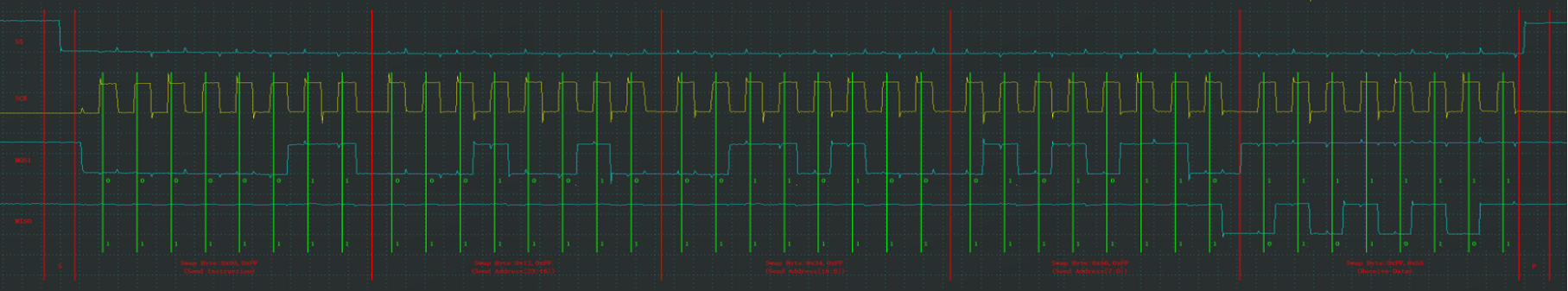

软件/硬件波形对比

软件波形

硬件波形

SCK下降沿数据移出,上升沿数据移入,无论是下降沿变化还是低电平期间变化,它们都是一个意思,下降沿和低电平期间都可以作为数据变化的时刻,只是硬件波形一般会紧贴边沿,软件波形,一般只能在电平期间,当然无论是哪种方式,最终都不会影响数据传输

浙公网安备 33010602011771号

浙公网安备 33010602011771号