1、kc705_user_guider里面可以找到各个bank的xdc的约束命令,如何去接端口。

2、kc705的7series_hdl可以找到各种原语的介绍,以及verilog的例化模板。当然,vivado中tools下面的Language Templates也可以找到。

3、kc705的schematic是k7芯片的I/O端口。

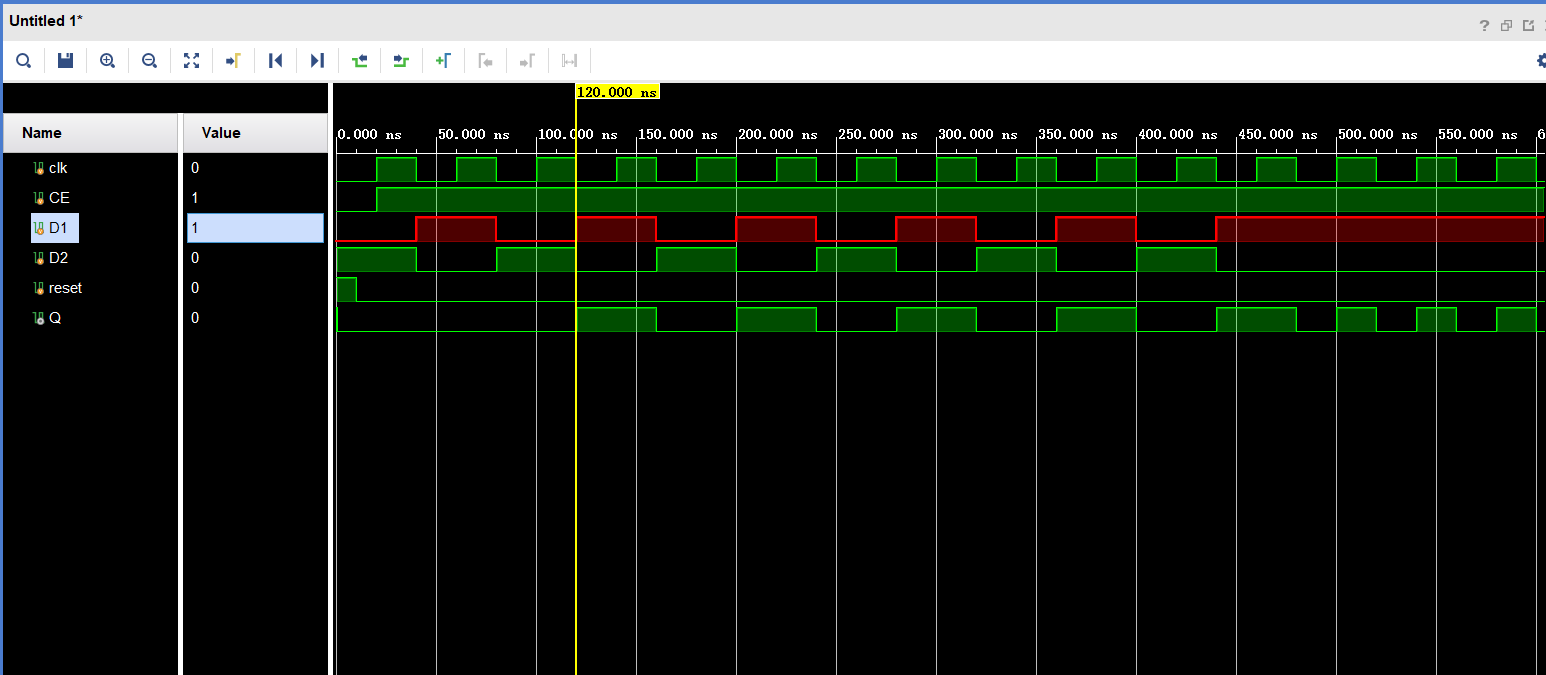

4、OBUFDS原语必须要配合ODDR原语的使用,OODR分为上下降沿进行采样,上升沿对D1采样,下降沿对D2采样,拼成一个时钟周期(上板可能会有时延)。输出的信号给OBUFDS,在实现一个单端转为双端差分信号。

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q(Q), // 1-bit DDR output

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D1(D1), // 1-bit data input (positive edge)

.D2(D2), // 1-bit data input (negative edge)

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

// End of ODDR_inst instantiation

测试代码:

module test_oddr( input clk, input CE, input D1, input D2, input reset, output Q ); ODDR #( .DDR_CLK_EDGE("SAME_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE" .INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1 .SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC" ) ODDR_inst ( .Q(Q), // 1-bit DDR output .C(clk), // 1-bit clock input .CE(CE), // 1-bit clock enable input .D1(D1), // 1-bit data input (positive edge) .D2(D2), // 1-bit data input (negative edge) .R(reset), // 1-bit reset .S(1'b0) // 1-bit set ); // End of ODDR_inst instantiation endmodule

tb:

module test(); reg clk; reg CE; reg D1; reg D2; reg reset; wire Q; initial begin reset=1; #10; reset=0; end initial begin clk=0; forever#20 clk=~clk; end initial begin CE=0; #20; CE=1; end initial begin D1=0; D2=1; #40; D1=1; D2=0; #40; D1=0; D2=1; #40; D1=1; D2=0; #40; D1=0; D2=1; #40; D1=1; D2=0; #40; D1=0; D2=1; #40; D1=1; D2=0; #40; D1=0; D2=1; #40; D1=1; D2=0; #40; D1=0; D2=1; #40; D1=1; D2=0; end test_oddr u_test_oddr( .clk(clk), .CE(CE), .D1(D1), .D2(D2), .reset(reset), .Q(Q) ); endmodule

vivado仿真波形:

浙公网安备 33010602011771号

浙公网安备 33010602011771号