FPGA中亚稳态的分析与解决

在学习 FPGA 的新手入门项目中,FIFO 是一个不可错过的经典练手项目。与简单的地址加法器(Addr 加法器)不同,FIFO 更强调对 FPGA 时序特性 的深入理解,是学习跨时钟域设计的绝佳实例。

FIFO 的设计不仅能帮助新手掌握基本的硬件描述语言,还能引导我们深入探索 FPGA 中时序约束、同步机制等重要概念。尤其是在工程实践中,最大的挑战是如何正确解决 亚稳态问题,否则 FIFO 的数据传输就可能变得不稳定,导致整体设计失效。

通过实现 FIFO,初学者可以真正理解和应对 FPGA 开发中的时序问题,这对后续设计更复杂的项目有极大的帮助。

概念解析

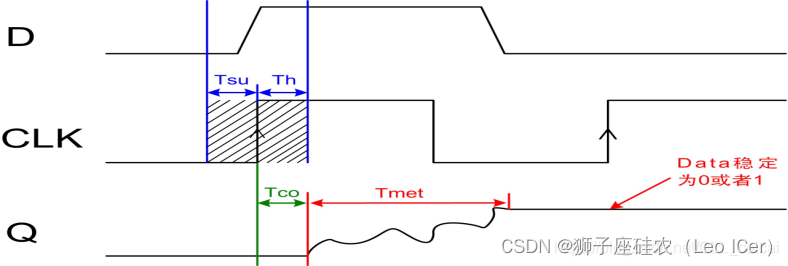

对于很多软件出身的人来讲,认为数字电路中的状态不是3.3v,就是0v。在状态改变的过程中,电压立马从3.3v,跳变到0v。而实际并不是这样的,门电路由mos管组成。mos管的充放电都需要时间。在异步FIFO中,两个不同的时钟频率间互相传递数据,很容易出现采样不及时等情况。表现在电压信号中就是电压信号在0~3.3v中随机震荡很长一段时间,最终会明确信号。在震荡这部分时间,我们称之为亚稳态。顾名思义,就是不稳定状态。

解决分析

在很多教科书中讲解,通过两极触发器即可解决亚稳态采样。在这里简单讲一下原因。

mos管的原理是通过形成电容,构建沟道,从而导通电路。在这里有两个重要参数,分别是Vg>Vs和阈值时间,也就是电容形成的时间。

电路进入亚稳态,此时电压信号很难驱动并打开mos管,也就是门电路。对于D触发器来讲值不会变动,依旧输出上一次明确的逻辑信号。解决了亚稳态采样问题。

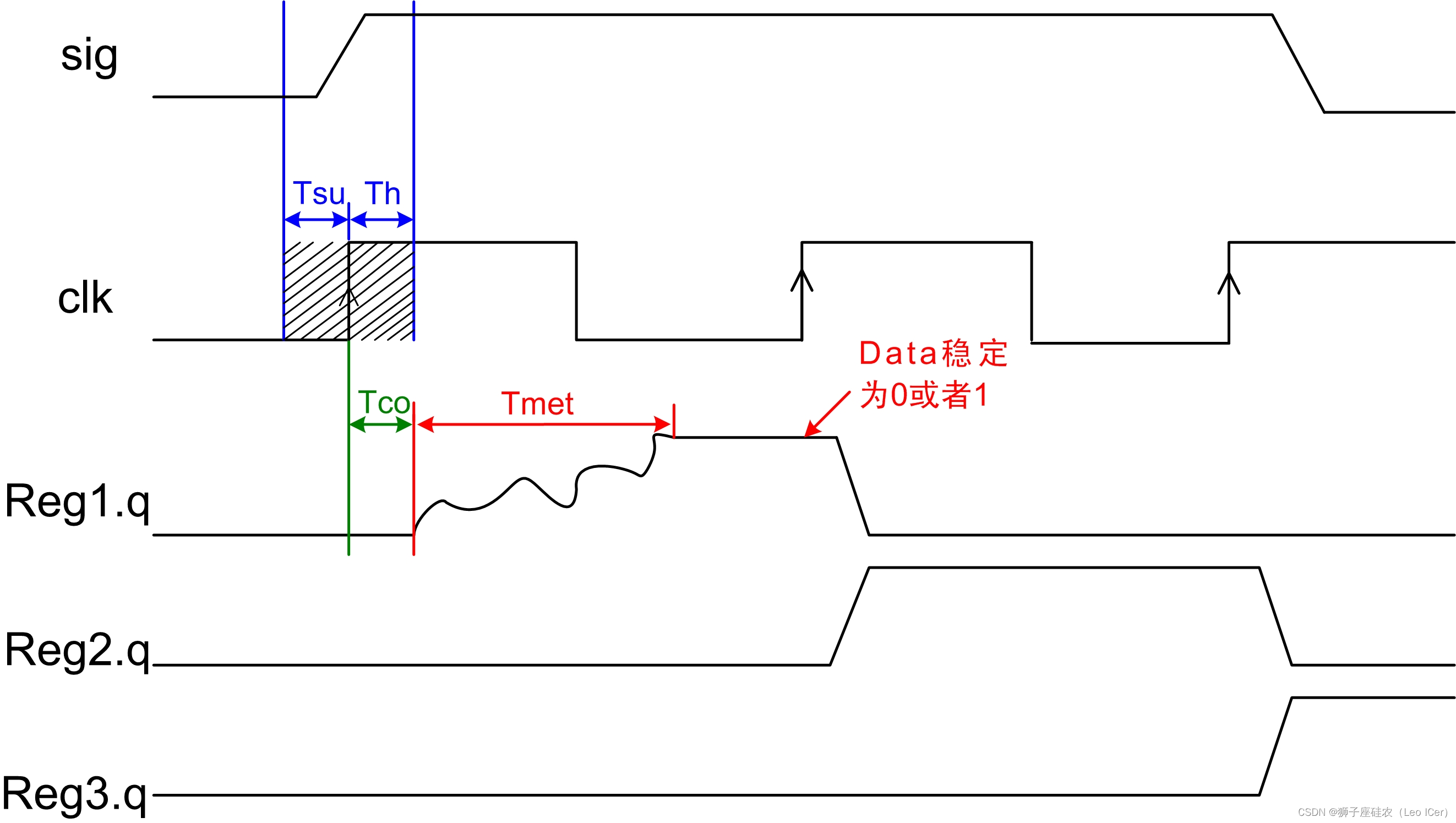

可能这时候有同学提问,那只需要一个D触发器就可以,为什么还需要两个触发器呢?原因很简单,mos管的Vg>Vs,栅极电压并不会是明确的3.3v,很有可能1.5或2.0V。这时候亚稳态电路恰好达到mos管的阈值电压,并且阴差阳错地达到了mos管充电阈值。此时D触发器会因为亚稳态而采集到不正确的逻辑信号。如果只有一个D触发器,此时就会输出这个错误的逻辑信号,约等于继续传播这个错误的亚稳态,造成FPGA错误。

而如果存在两个D触发器,虽然第一个D触发器因为采集到亚稳态信号而变成错误的逻辑信号,这个时间周期可能已经超过了时钟上边沿的周期,因此第二个D触发器在非时钟上边沿是无法被写入的。这个错误的逻辑信号就会被存储在第一个D触发器中。

根据统计,一般亚稳态顶多在一个周期内就会结束。在下一个时钟上边沿到来之际,第一个D触发器会采样正确的逻辑信号,并修改存储的值,由因亚稳态而采集到的错误逻辑信号修改为正确的逻辑信号。第二个D触发器此时会先接收到这个错误的逻辑信号,紧接着第一个D触发器会把正确的值再传递给第二个D触发器。完成亚稳态的消除工作。如果你为了更保险,基于上面的原理,可以多增加几个触发器,串联即可。

浙公网安备 33010602011771号

浙公网安备 33010602011771号