ti8168平台的tiler memory

DM8168 DMM/TILER简介

1.概述

如图4-1,DMM定位在SDRAM控制器的前端,是所有initiator产生的内存存取的接口。

动态内存管理器DMM,是一个专门的管理模块,广义上说,包括内存存取的方方面面。比如:

- initiator索引化的优先级产生。

- 多区域SDRAM内存交织配置

- 块目标传输优化:tiling和子tiling

- 集中的低延迟页翻译:类似MMU

内存的动态管理表现为软件可配置,天性为运行时,由DMM操作的内存管理有4个方面:

- 添加基于Initiator的优先级到任何输入的请求中

- 执行tiled请求的tiling转换

- 提供优化的低延迟基于页的翻译以便管理内存碎片:MMU

- 在两个内存控制器间按照交织配置分配交通。

TILER是DMM内的一个子模块,目的是高效操作2D数据,比如HDVICP2通过使用tiled格式进行视频/图像存取。

- 优化管理内存碎片,通过页为粒度的翻译实现0 copy物理帧缓冲交换。

- 产生高速0浪费的变换:90/180/270度旋转,带水平或垂直镜像。

2.特征

- 延迟特别低的互联端口:ELLA,用于Cortex A8存取

- 在两个EMIF bank之间的DDR数据可以是交织的,使用可编程的多区域DRAM内存映射,这增加了2倍内存通过率,支持多达4个独立的内存区域(Section)

- 基于优先级请求扩展的可编程Initiator,多达16个initiator组。

- 支持tiled数据的地址翻译,在4KB页粒度中使用PAT,这有助于管理内存碎片。

- 2个内部地址查找表(LUT),每个有256x128个入口,4个可重填引擎用于编程LUTs,带自动同步重加载。

- 支持4个独立的PAT视窗。

3.功能模块图

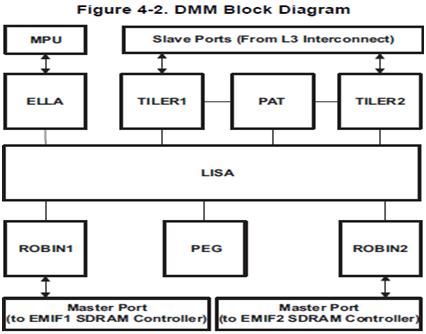

图4-2显示了DMM宏结构。DMM组成是6个模块:

- PEG:优先级扩展产生器,用来产生SDRAM控制器要求的优先级。注意这些优先级并不在DMM中使用。

- ELLA:极低延迟存取,它有自己的互联从端口,用来提供对内存的极低延迟存取。

- LISA:局部互联和同步代理,用来同步所有的DMM子系统和提供对配置寄存器的存取。

- PAT:物理地址翻译,用来管理内存碎片。

- ROBIN:重定序缓冲和Intiator节点,共有2个,它们有自己的互联Master端口,用来向SDRAM控制器发出请求,允许tiled数据、tiled响应和分裂的响应重构,ROBIN模块仅能管理重定序缓冲和执行数据由于定向而需要的数据重定序。

- TILER:2个,它有自己的互联从端口,用于在输入虚拟地址模式和输出物理tiled地址之间进行转换请求。注意,tiling请求转换,写数据和响应完全由TILER模块执行,

4.一些关键词和缩写词汇

bpp:Bits per pixel 每个像素使用的位数

DMM:Dynamic Memory Manager 动态内存管理

ELLA:Extra Low Latency Access 极底延迟的存取

GB,GiB:Both imply Giga Byte 都是千兆字节的意思

Initiator:器件里的一个节点,可以是CPI、外设、或DMA等,它可能是内部总线管理者(MASTER)。每个Initiator由一个ConnID(connection ID连接ID)来标识,ConnID最大限制是16,某些Initiator被分组在一起,使用一个ConnID号。

Interlaced:Qualifier for access skipping one line every line 可以跳行交织存取

IVA:Image Video Accelerator, Also called HDVICP2, IVA_HD 视频图像加速器,又称HDVICP2,IVA_HD

LISA:Local Interconnect and Synchronisation Agent 本地互联和同步代理

KB,KiB:Both imply Kilo Byte 都是千字节的意思

LUT:Look Up Table 查找表

MMU:Memory Management Unit 内存管理单元

MPU:Main Processing Unit. For the Device, it is Cortex A8 主处理器,这里指Cortex A8

PAT:Physical Address Translator 物理地址翻译

PEG:Priority Extension Generator 优先级扩展发生器

Progressive:与Interlaced相反,必须一行行连续存取。

ROBIN:Re-Ordering Buffer and Initiator Node 重新定序缓冲和发起者节点

Tiled access:对tiled区域的1D或者2D存取。在这儿,图像以2D方式读出和写入。改善了2D存取的效率,例如对图像的宏块存取,TILER 简化为一个简单的1D线性读写请求,DMM负责在连续内存中完成请求中指定的地址读写。

2D access:HDVICP2和HDVPSS能对2D图像缓存产生一个特殊的存取,带有读/写请求,高度和宽度信息。DMM-TILER基于高度宽度和地址来译码存取类型,负责读/写数据到物理内存,基于粒度为子tile的坐标。

http://blog.csdn.net/shanghaiqianlun/article/details/762048

HDVPSS 使用TI开发的算法,灵活的复合和融合引擎,各种高质量外部视频接口,实现视频/图像显示和采集处理功能。

2.1.3 缩略语

|

名称 |

定义 |

|

|

COMP |

Compositor |

复合器 |

|

DEI |

De-Interlacer |

去隔行 |

|

DEIH |

High quality De-Interlacer |

高质量去隔行 |

|

DVO |

Digital Video Output |

数字视频输出 |

|

GRPX |

Graphics Pipeline |

图形流水 |

|

HD |

High Definition |

高清 |

|

HDCOMP |

High Definition Component |

高清分量 |

|

HDMI |

High Definition Multimedia Interface |

HDMI接口 |

|

HDVPSS |

High Definition Video Processing Subsystem |

高清视频处理子系统 |

|

NF |

Noise Filter |

噪声滤波 |

|

NTSC |

National Television System Committee |

NTSC |

|

PAL |

Phase Alternating Line |

PAL |

|

SC |

Scaler |

缩放 |

|

SD |

Standard Definition |

标清 |

|

SDK |

Software Development Kit |

软件开发包 |

|

TILER |

Tiling and Isometric Light weight Engine for Rotation |

平铺和等容积轻量级旋转引擎 |

|

VENC |

Video Encoder |

视频信号调制编码器 |

|

VIP |

Video Input Port |

视频输入口 |

|

VPDMA |

Video Port Direct Memory Access |

视频口DMA |

2.1.4 数据格式

表2列出了HDVPSS的数据格式。注意对于T422 YUV422I_YUYV数据格式最大输入数据宽度是960个像素。

|

名称 |

数据格式 |

对齐方式 |

TILER功能 |

|

422I |

YUV422I_YUYV |

单一缓存:Y U Y V Y U Y V |

不支持 |

|

420T |

YUV420SP_UV |

Y缓存:Y Y Y Y UV缓存:U V U V |

Y:8-bit UV:16-bit |

|

422T |

YUV422SP_UV |

Y缓存:Y Y Y Y UV缓存:U V U V |

Y:8-bit UV:16-bit |

|

422T |

YUV422I_YUYV |

单一缓存:Y U Y V Y U Y V |

不支持 |

0

浙公网安备 33010602011771号

浙公网安备 33010602011771号