3.存储器

Memory overview

一.Categories

1.存储介质(storage media)进行分类

- Semiconductor(半导体) Memory :TTL,MOS \(\leftarrow volatile\)

- 磁表面存储器:磁头、载磁体

- 磁芯存储器:硬磁材料、环状原件

- 光盘存储器:激光,磁光材料

2.存取方式分类

- 存取时间和物理地址没有关系(随机访问)

- 随机存储器 程序执行过程可读可写

- 只读存储器 程序执行过程中只可读

- 存取时间和物理地址有关(串行访问)

- 顺序存取存储器 磁带

- 直接存取存储器 磁盘

3.按计算机作用分类

-

主存储器

-

RAM

静态Sram

动态Dram

-

ROM

MROM

PROM

EPROM

EEPROM

-

-

flash memory(半导体存储器)

-

高速缓冲存储器(cache)通常用静态ram来做

-

辅存储器:磁盘磁带光盘

二.存储器的层次结构

存储体系:寄存器 缓存 主存 辅存。磁盘光盘磁带

- 寄存器分为体系结构寄存器(不透明)和非体系结构寄存器(透明)对程序员

程序局部性原理,时间空间局部性原理 cpu和缓存提高速度

1.缓存和主存层次 (速度,硬件连接)

- 主存储器

- 实地址

- 物理地址

2.主存和辅存层次(容量,软硬件结合方式)

- 虚拟存储器

- 虚地址

- 逻辑地址

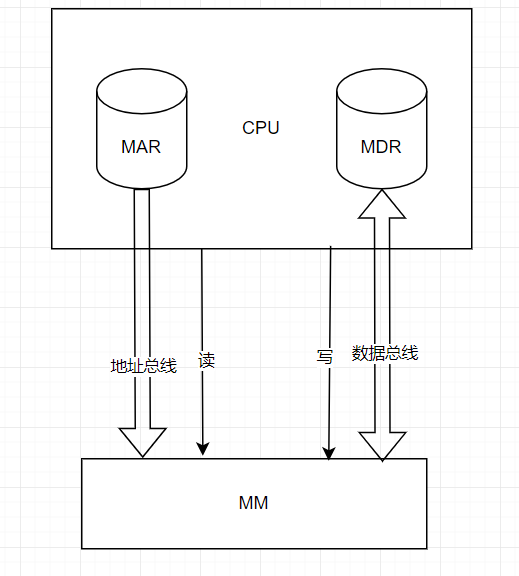

主存储器

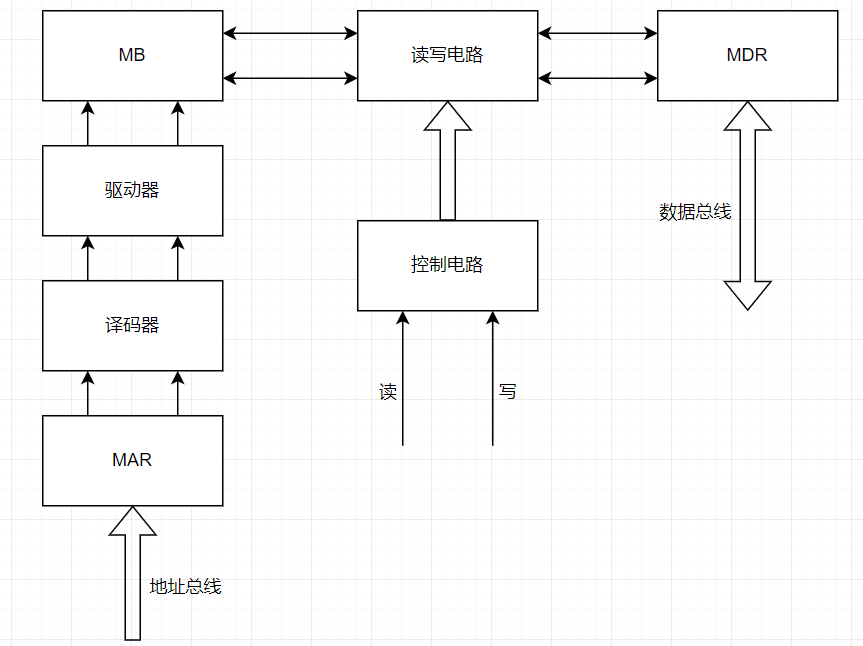

主存的基本组成

主存和cpu联系

主存中存储单元的地址分配

12345678H如何存储

大端大尾方式

小端小尾方式

设地址线24根

按字节寻址 \(2^{24}B=16MB\)

按字寻址

- 16bit字长 \(16MB/(16/8)B=8MW\) w=16bit

- 32bit字长\(16MB/(32/8)=4MW\) w=32bit

主存的技术指标:

存储容量 :存放二进制代码的总位数

存储速度:

-

存取周期:连续两次独立的存储器操作(读或写)所需要的最小时间间隔

-

存取时间:存储器的访问时间

- 读出时间

- 写入时间

-

存取时间比存取周期要短

\(存取周期=存取时间+等待时间\)

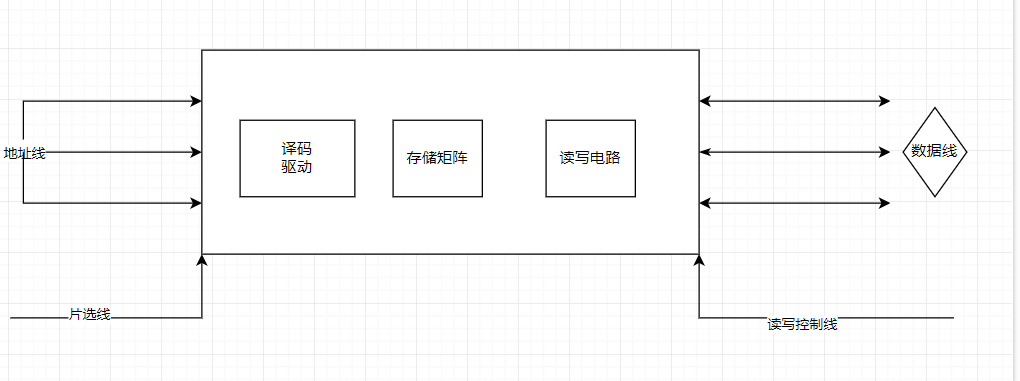

主存储器——半导体芯片

半导体存储芯片基本结构

存储容量计算:

10根地址线,8根数据线

\(2^{10}\times8bit=1K\times8bit=1KB\)

片选线:

\(\overline{CE}或者\overline{CS}\)

读写控制线:

\(\overline{WE}低电平写\)

\(\overline{OE}低电平允许读\)

存储芯片片选线作用:

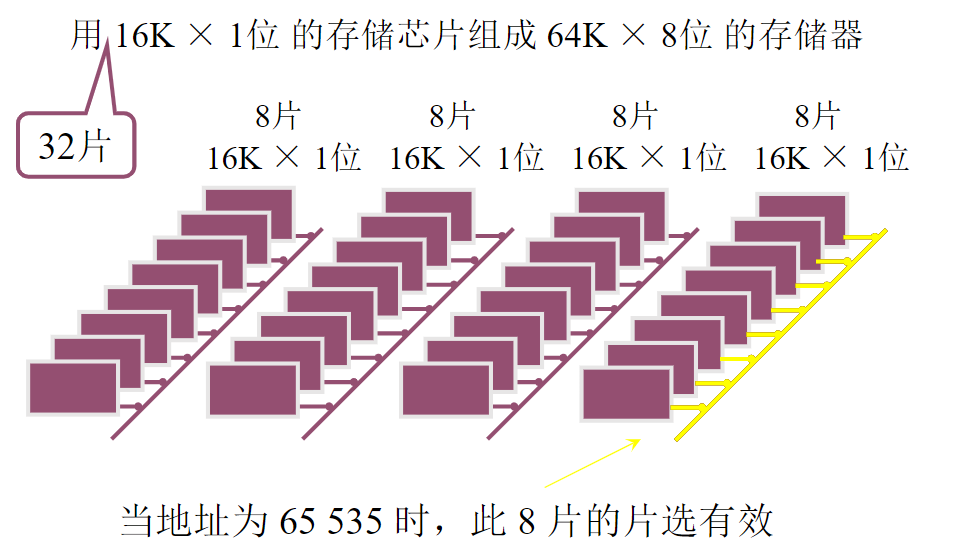

将是 \(16k\times 1bit\)的存储芯片组成 \(64k\times8bit\)的存储器

将8个芯片的片选线连接在一起成为一组,可以同时读写操作

则为\(16k\times8bit\)

使用6组芯片组

则为 \(64k\times8bit\)

地址65536时,第8组的片选线有效

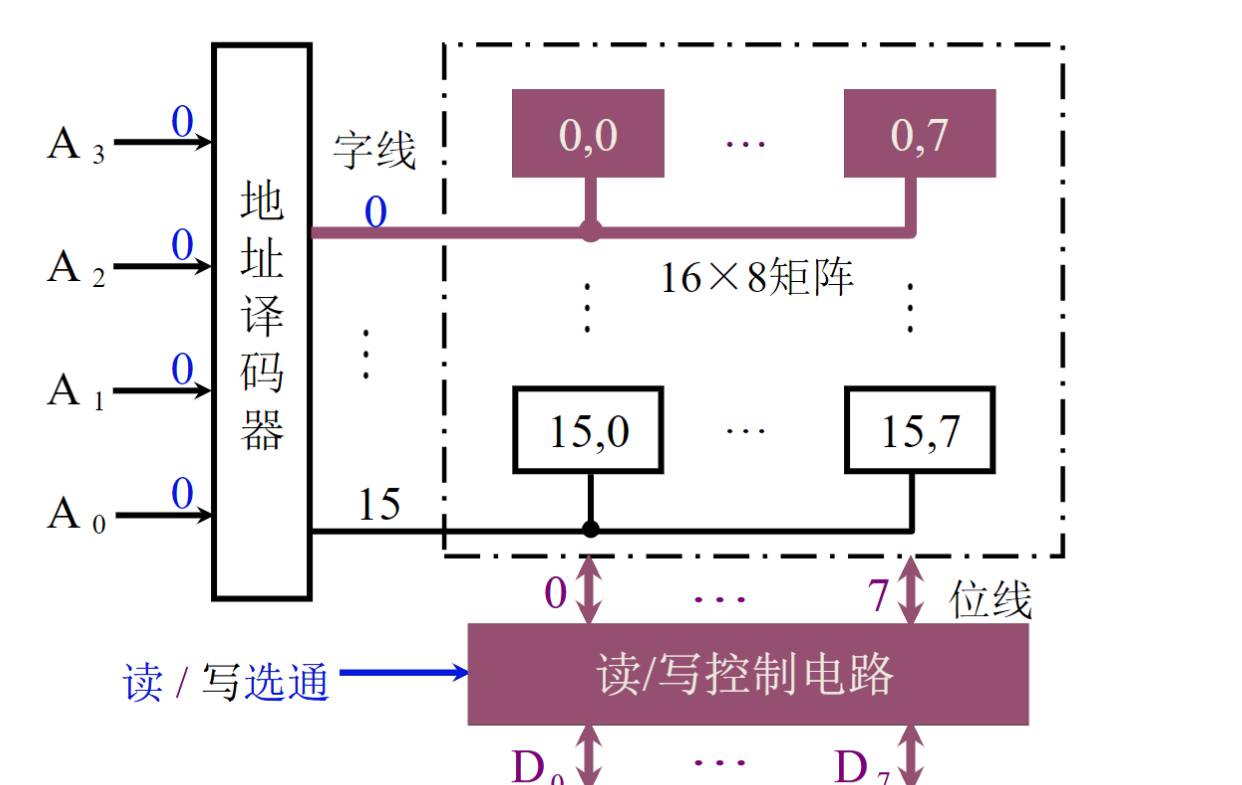

半导体存储芯片译码驱动方式

1.线选法

2.重合法

随机存取存储器(RAM)

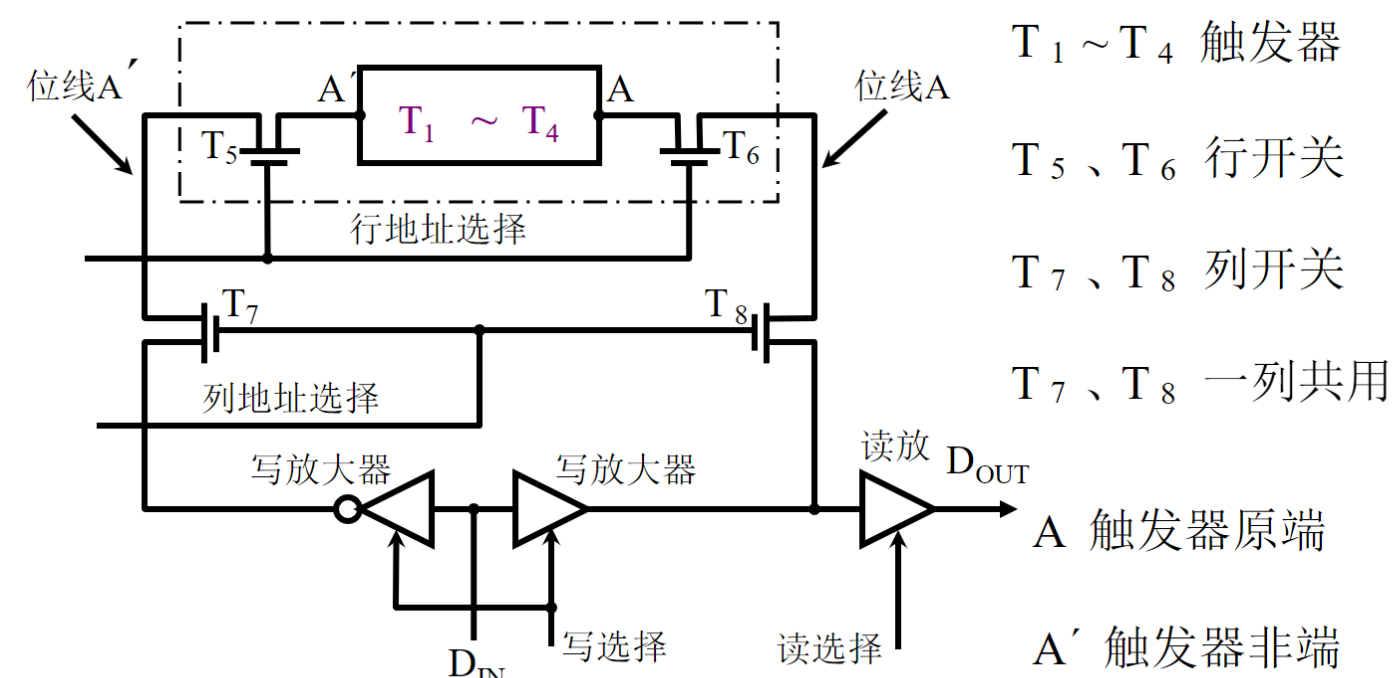

SRAM(静态ram)

通过双稳态触发器来保存0,1

6管SRAM的单元电路

单元电路读操作

\(行选\rightarrow T5,T6开\)

\(列选\rightarrow T7,T8开\)

读选择有效

\(V_A\rightarrow T6\rightarrow T8\rightarrow 读放\rightarrow D_{OUT}\)

单元电路写操作

\(行选\rightarrow T5,T6开\)

\(列选\rightarrow T7,T8开\)

写选择有效

\(D_{in}两个写放\)

\(D_{in}\rightarrow T8\rightarrow T6\rightarrow A\)

\(D_{in}\rightarrow 反相\rightarrow T7\rightarrow T5\rightarrow A'\)

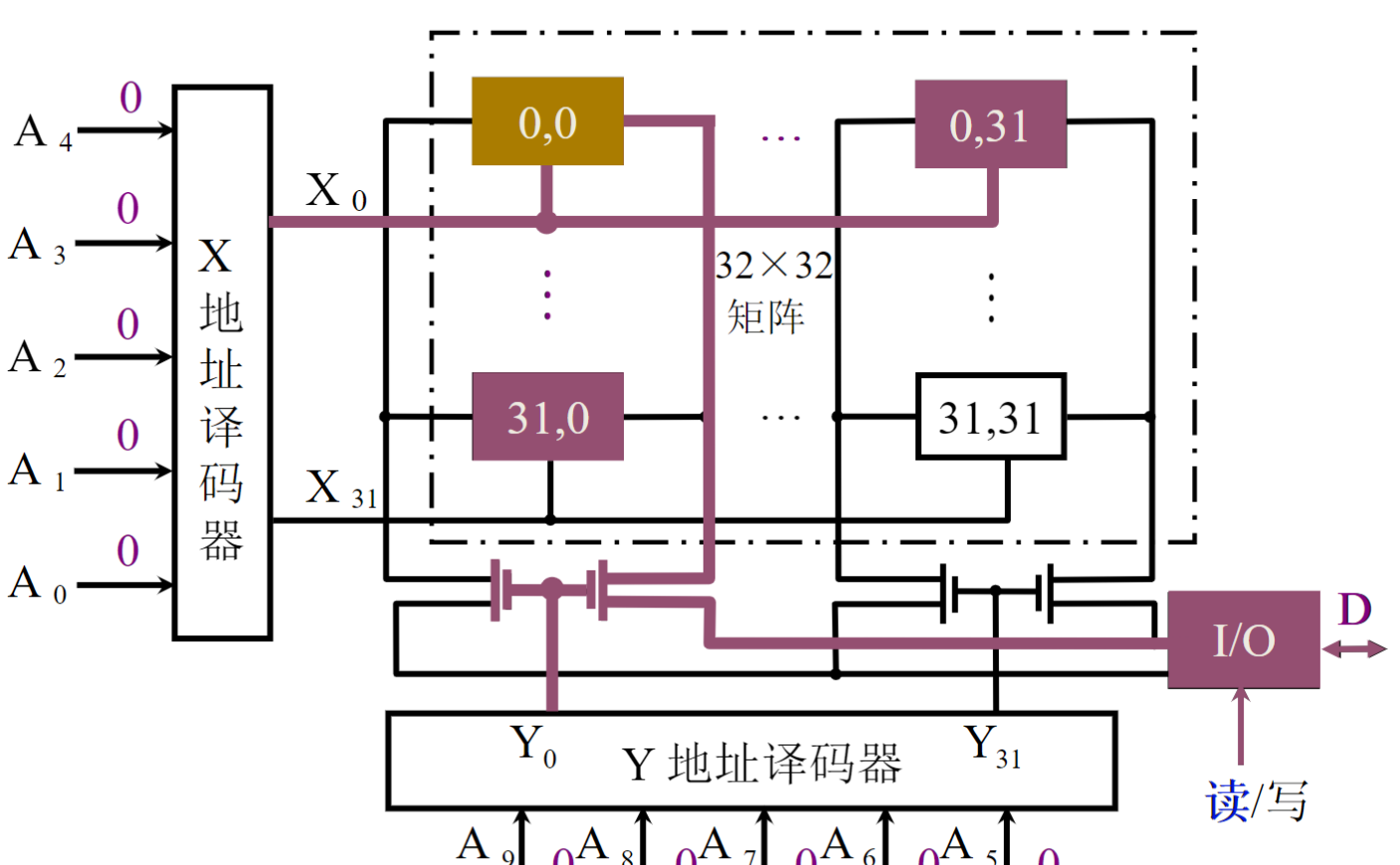

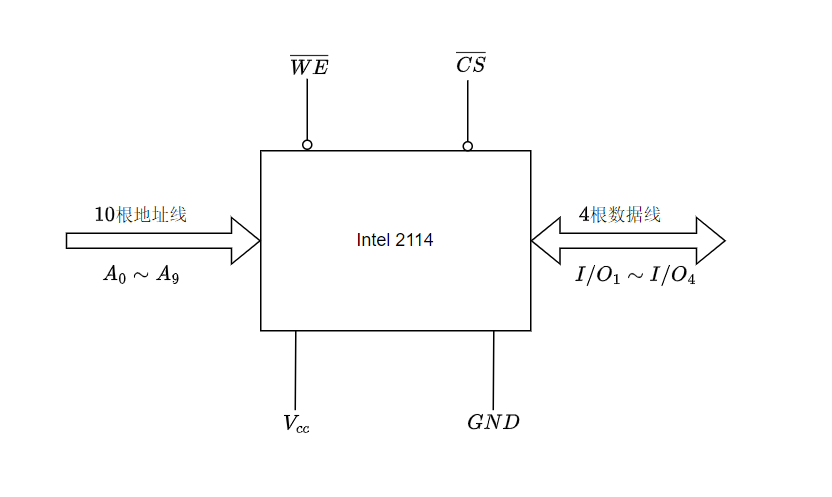

Sram典型芯片Intel 2114

外特性

存储容量为\(1k\times 4\)

存储容量为\(1k\times 4\)

通过重合法实现

4k容量= \(2^{12}=64^2\)所以存储矩阵为 \(64\times 64\)

需要6根行地址线

需要4根列地址线 \(因为需要实现一次四列,64列分成4组,16列一组,则需要4根地址线\)

也就是\(12-log_24\)

DRAM(动态ram)

dram单元电路

-

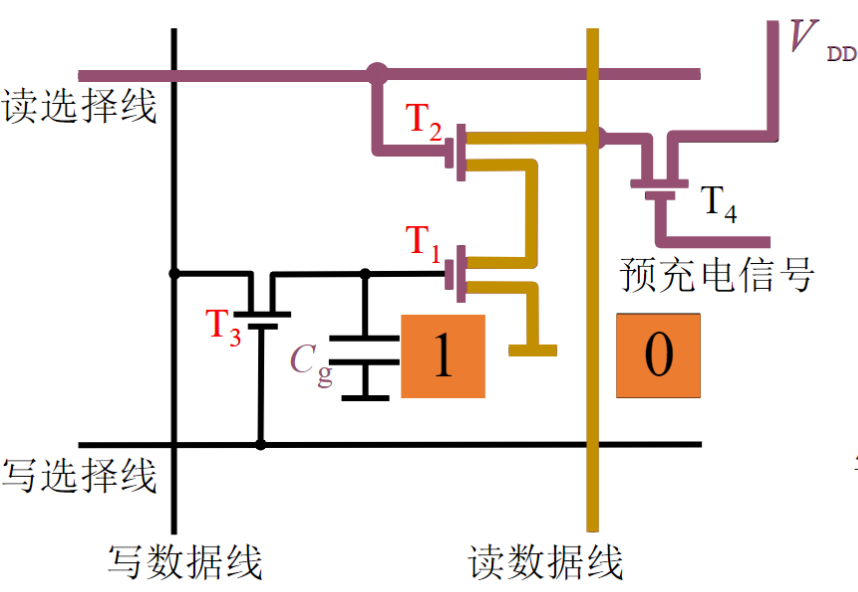

三管dram

![image-20240725215655044]()

-

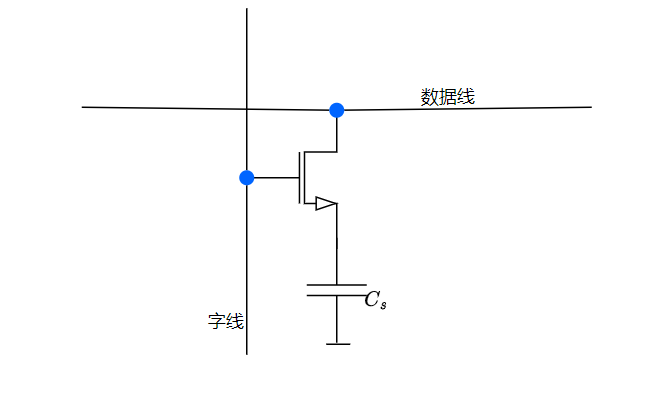

单管dram

![image-20240725220659764]()

DRAM典型芯片

-

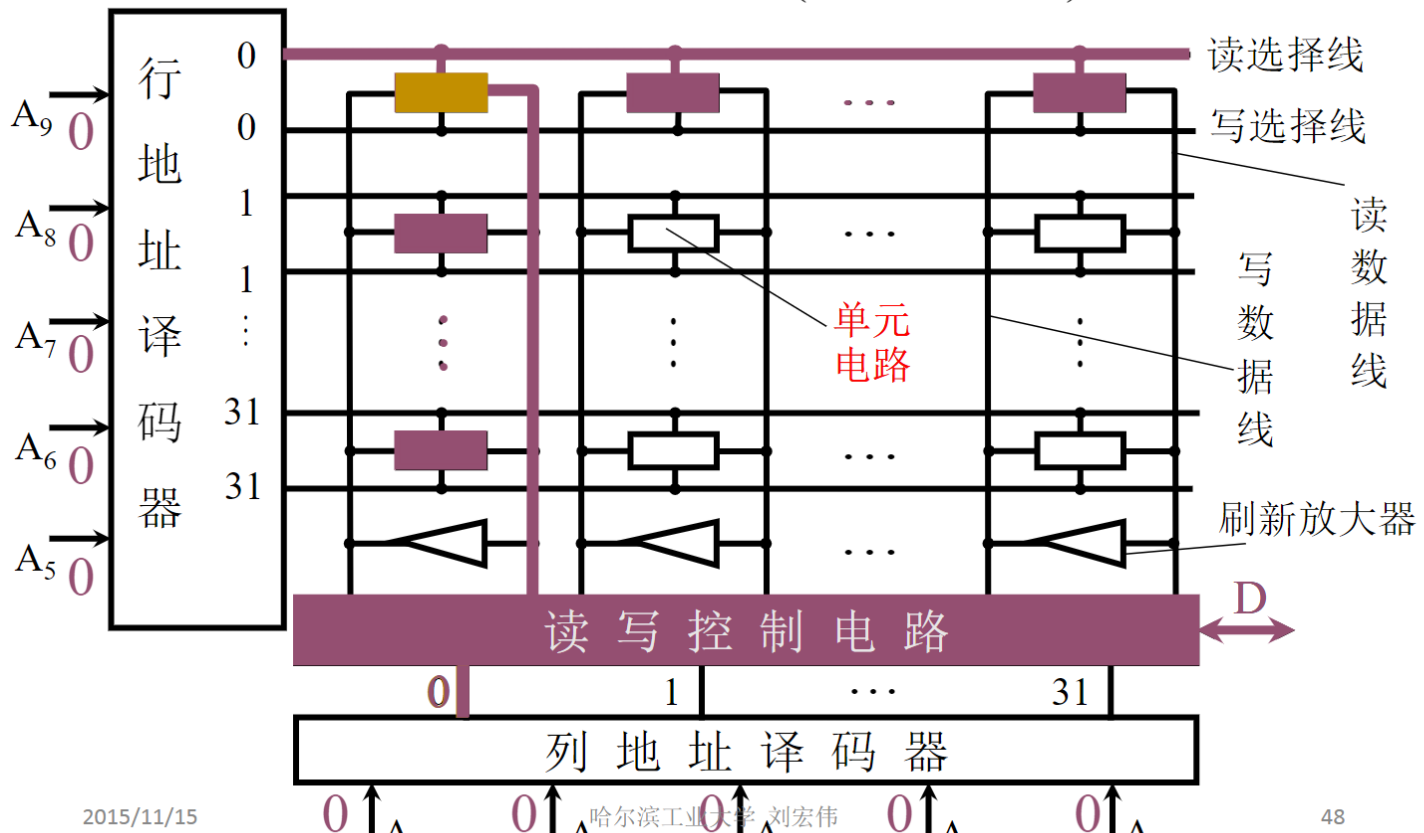

三管 (intel 1103)

![image-20240725221103591]()

-

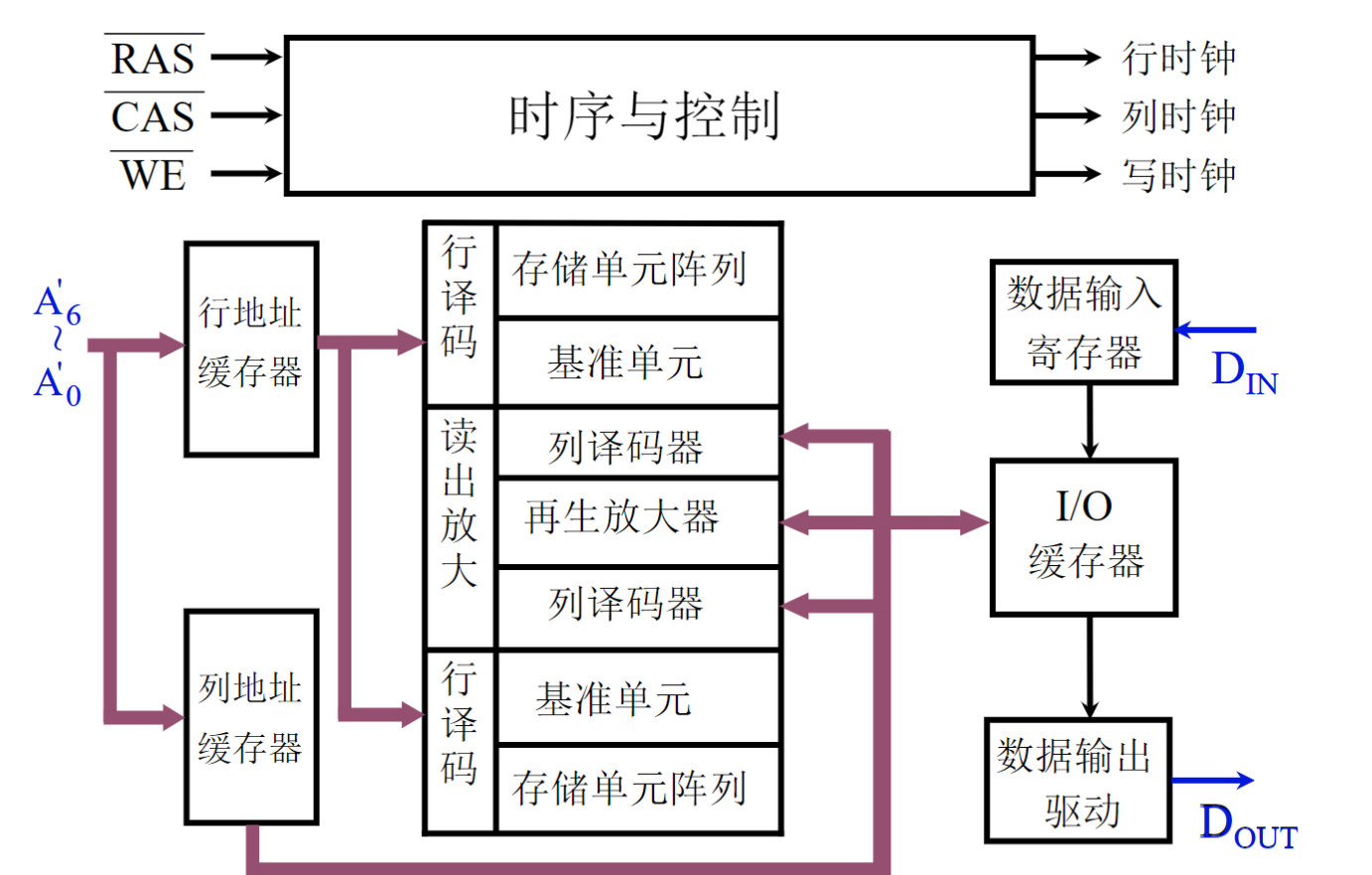

单管 4116 \(16k\times1bit\)

\(16k\times 1bit=2^{14}按理说需要14根地址线由于bus\; multiplexing 所以只需要7根地址线\)

外特性 \(\overline{CAS},\overline{RAS},\overline{WE}\)

![image-20240725221601785]()

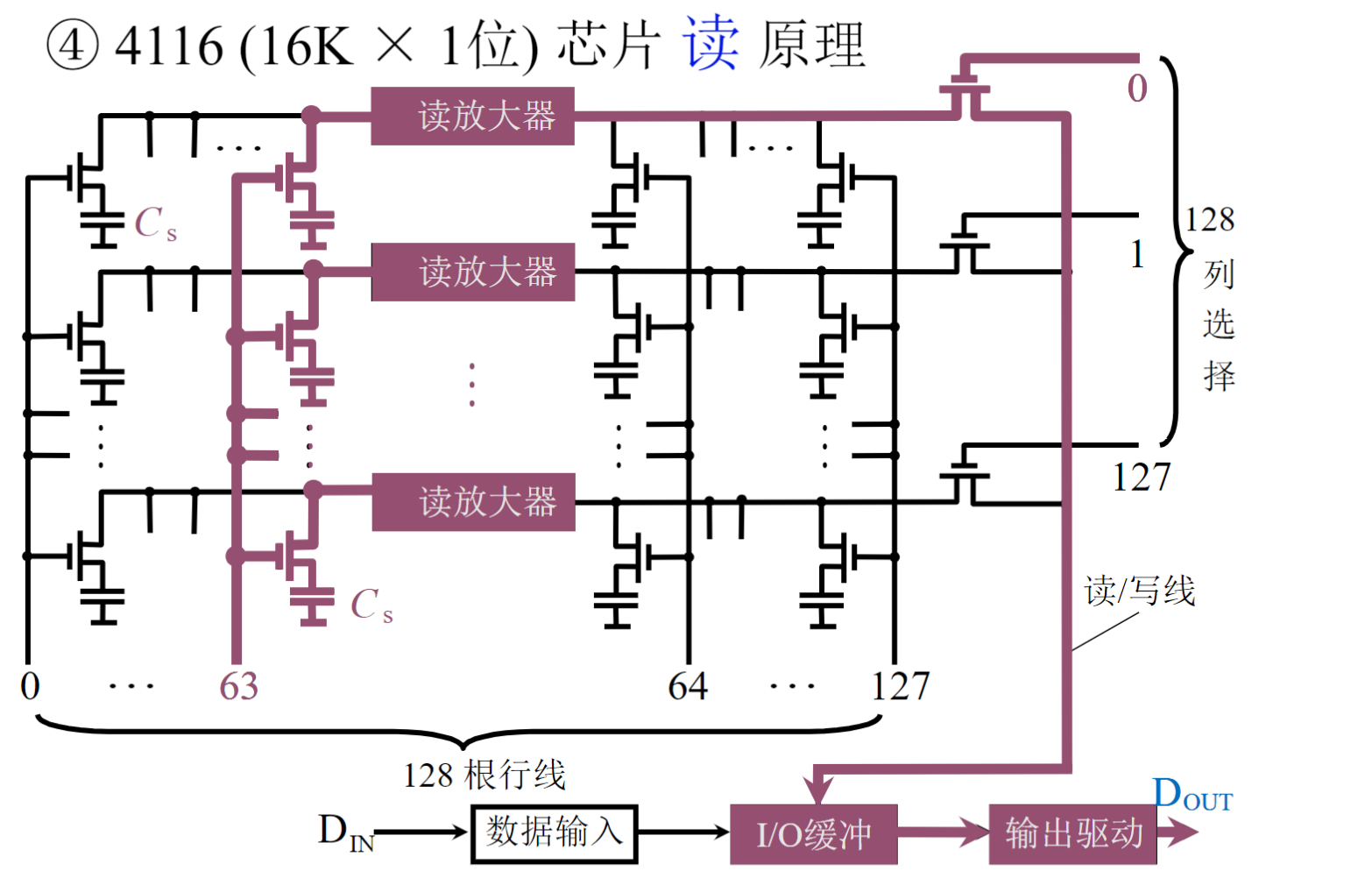

4116读原理

![image-20240725221815633]()

这里的读放大器相当于跷跷板电路两头0,1相反

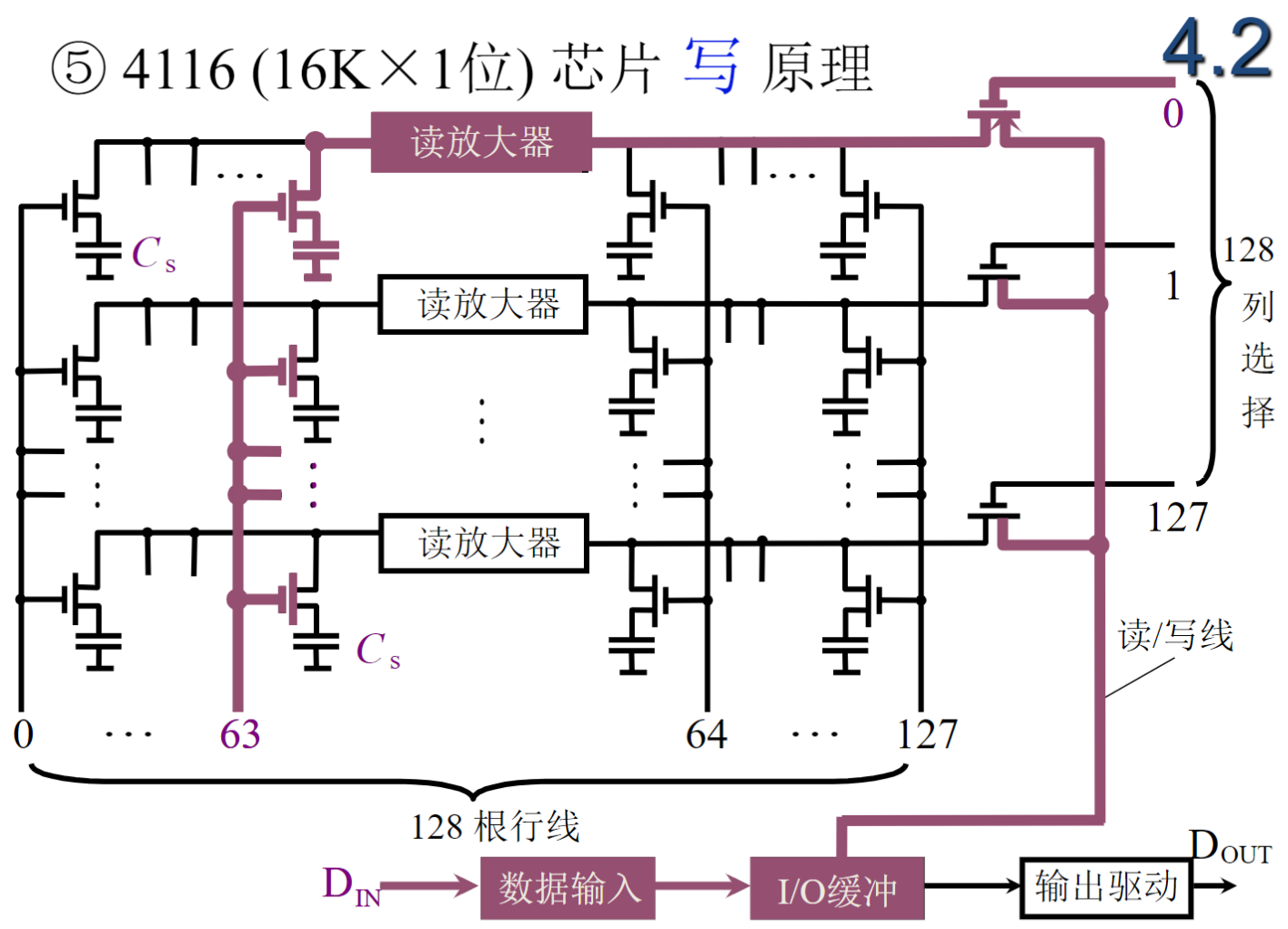

4116 写原理

![image-20240725223324267]()

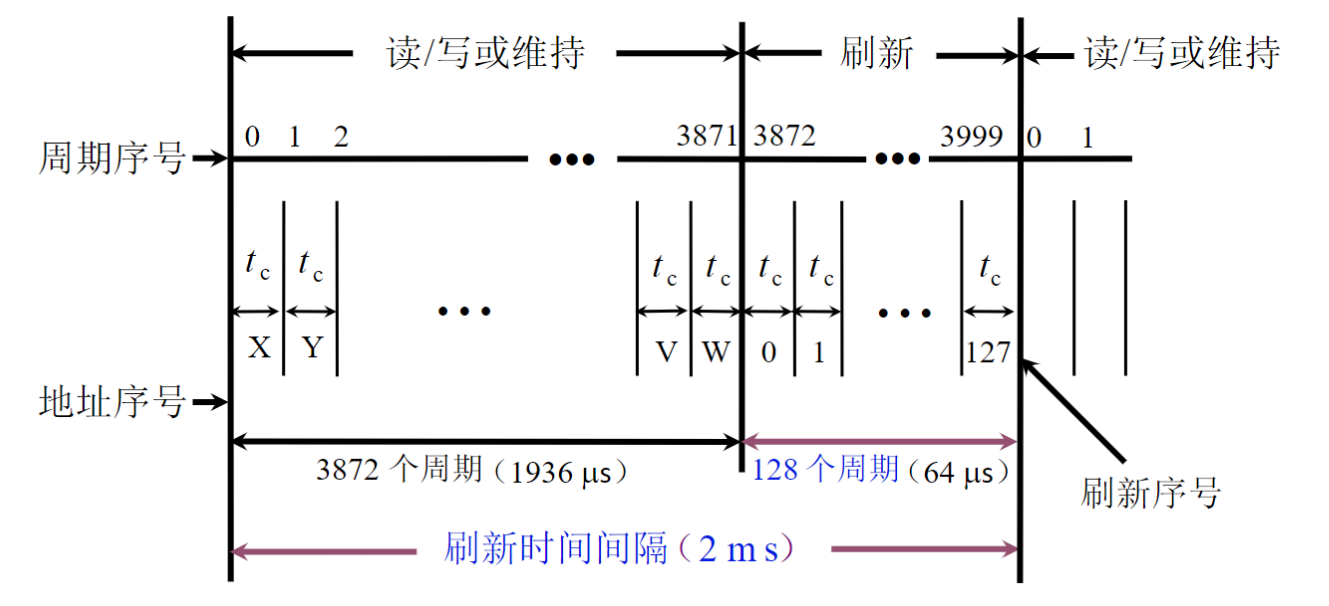

Dram刷新原理

刷新和行有关Row-Based Refresh

-

集中刷新 Concentrated Refresh

设存取周期为 \(0.5\mu s\)

\(128\times128\)矩阵为例

![image-20240725230327077]()

“死区 dead zone” 为 \(0.5\mu s\times128=64\mu s\)

“死时间率”为128/4000=3.2%

-

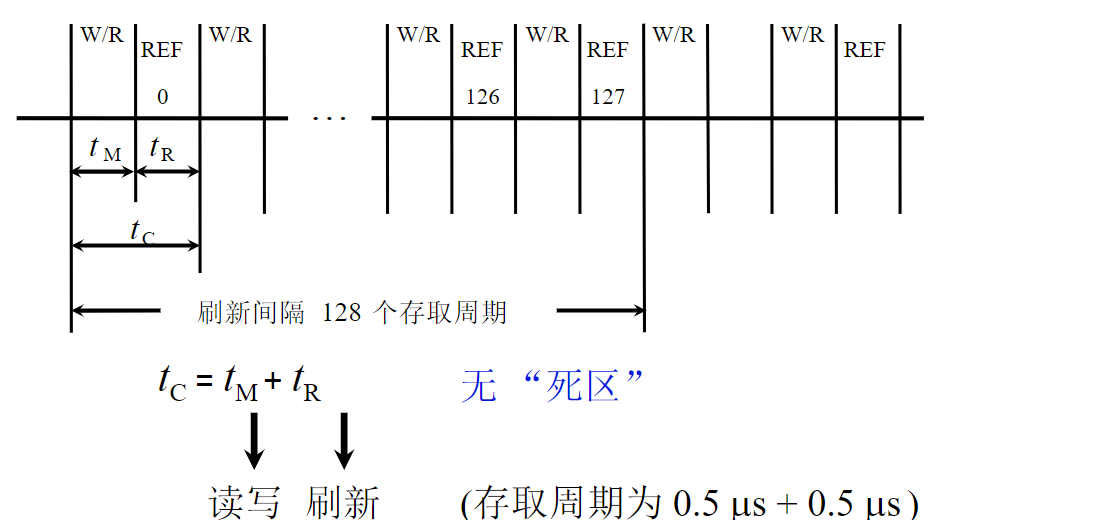

分散刷新Distributed refresh

设存取周期为 \(0.5\mu s\)

\(128\times128\)矩阵为例

![image-20240725232424803]()

-

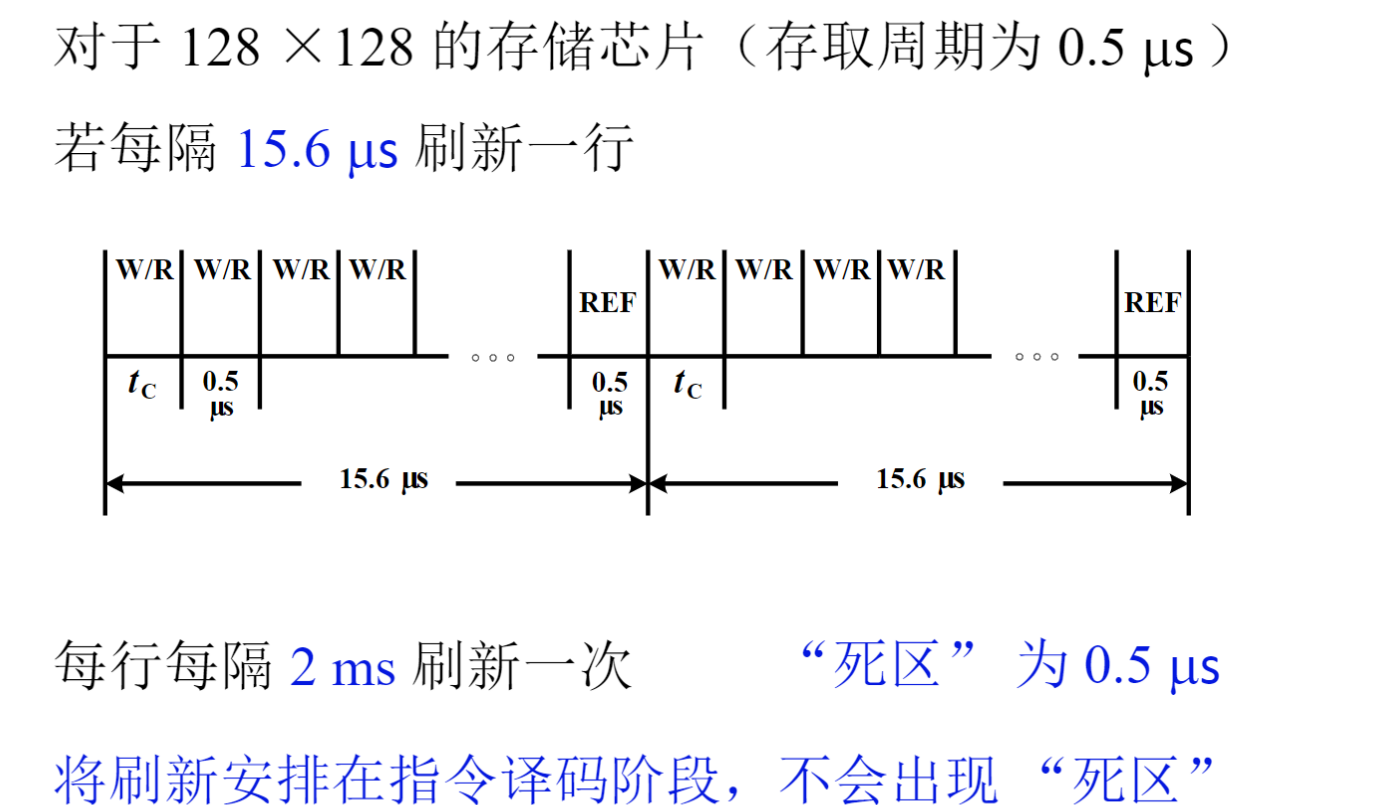

异步刷新Asynchronous refresh

设存取周期为 \(0.5\mu s\)

\(128\times128\)矩阵为例

![image-20240725232742599]()

-

SRAM和DRAM比较

| Dram(MM) | Sram(Cache) | |

|---|---|---|

| 存储原理 | 电容capacitor | 触发器flip flop |

| 集成度 | 高 | 低 |

| 芯片引脚 | 少 | 多 |

| 功耗 | 低 | 高 |

| 价格 | 低 | 高 |

| 速度 | 慢 | 快 |

| 刷新 | 需要刷新 | 不需要 |

浙公网安备 33010602011771号

浙公网安备 33010602011771号