3.4存储器拓展

提高访存速度的措施

采用高速器件

sdram(synchronous Dram 同步dram)

在系统时钟的控制下进行读写,cpu无需等待

支持猝发

rdram

解决带宽问题

带cache的dram

里面集成了一个sram组成的cache有利于猝发

采用层次结构 cache+主存

调整主存结构

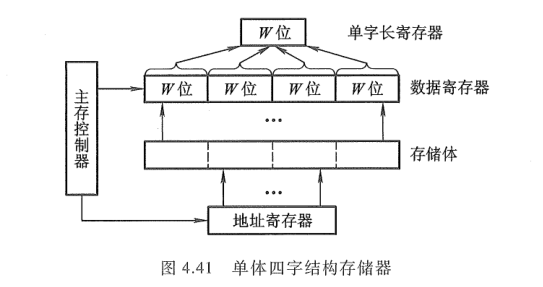

1.单体多字

缺点:

按地址在一个存取周期内可读出 4\(\times W\)位的指令或数据,使主存带宽提高到 4 倍。显然,采用这种办法的前提是:指令和数据在主存内

必须是连续存放的,一旦遇到转移指令,或者操作数不能连续存放,这种方法的效果就不明显。

2.多体并行系统

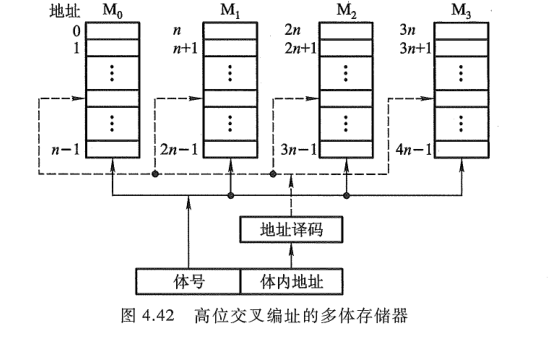

1.高位交叉编址(顺序存储)

这种编址方式由于一个体内的地址是连续的,有利于存储器的扩充。

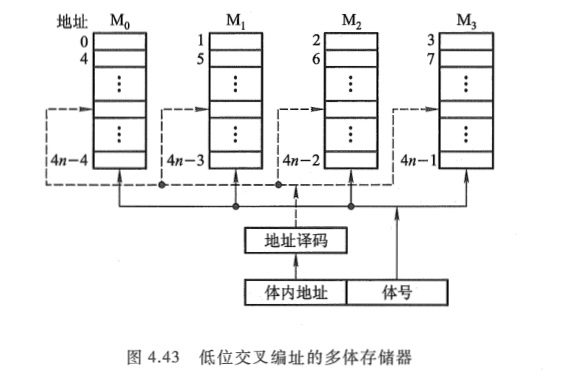

2.低位交叉编址

cpu交叉访问4个存储体

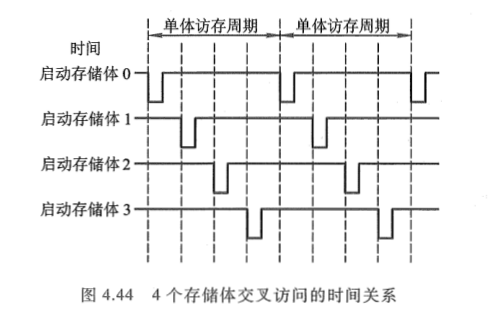

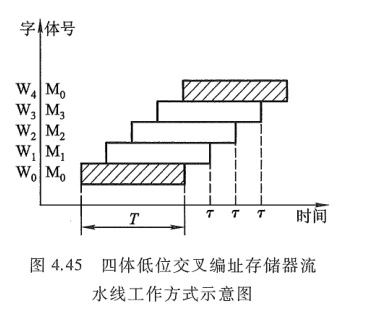

流水线工作方式

存储器模块数为 n ,存取周期为 T ,总线传输周期为 \(\tau\) ,那么当采用流水线方式(如图 4.44 所示)存取时,应满足 \(T=n*\tau\)

对千低位交叉的存储器,连续读取 n 个字所需的时间\(t_1=T+(n-l)\tau\)

高位交叉为\(t_2=nT\)

EX1

设有 4 个模块组成的四体存储器结构,每个体的存储字长为 32 位,存取周期为 200 ns 。假设数据总线宽度为 32 位,总线传输周期为 50 ns ,试求顺序存储和交叉存储的存储器带宽。

解:顺序存储(高位交叉编址)和交叉存储(低位交

叉编址)连续读出 4 个字的信息量是 \(32\times4=\) 128 位。

顺序存储存储器连续读出 4 个字的时间是

200 \(ns\times4\) = 800 ns = \(8\times10^{-7} s\)

交叉存储存储器连续读出 4 个字的时间是

200 ns+50 \(ns\times\)(4-1)= 350 ns=\(3.5\times10^{-7} s\)

顺序存储器的带宽是

128/(\(8\times10^{-7} s\))= \(16\times 10^7\) bps

交叉存储器的带宽是

128/(\(3.5\times10^{-7} s\))\(\approx\) \(37\times10^7\) bps

浙公网安备 33010602011771号

浙公网安备 33010602011771号