2.总线

BUS(总线)

Fundamental Concepts:

各个部件共享的传输介质,连接部件的信息传输线

Physical Implementation of the Bus:Mainboard

模式:

互连缺点,占用空间大,不利于拓展;

Bus Architecture:总线结构

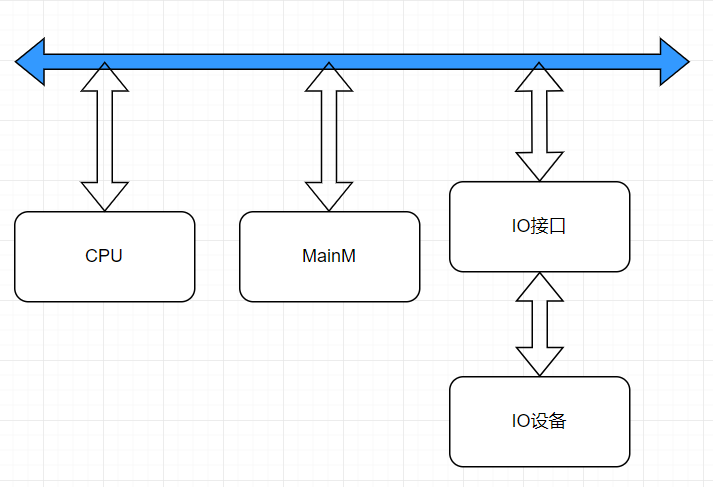

Single Bus单总线结构:

Drawbacks:

-

延迟问题,总线长导致

-

io占用,影响cpu效率

-

Bus Arbitration (总线争用问题)

-

总线瓶颈

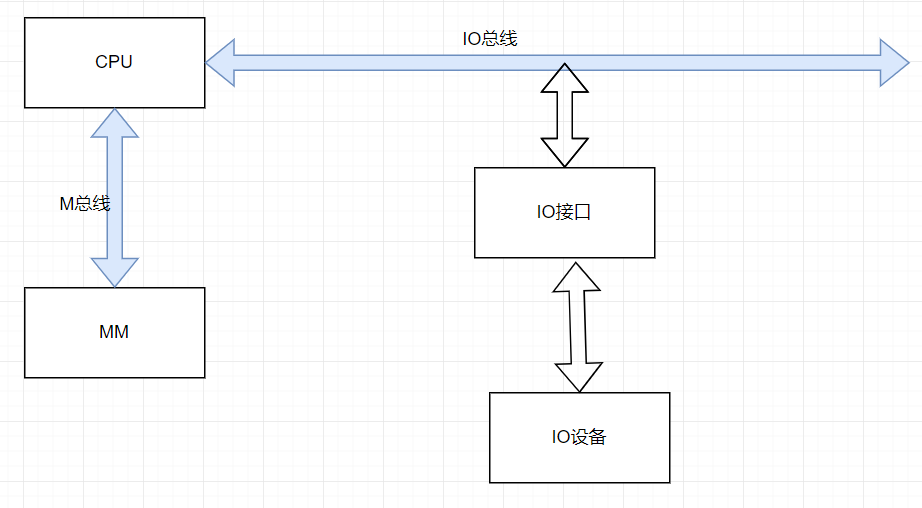

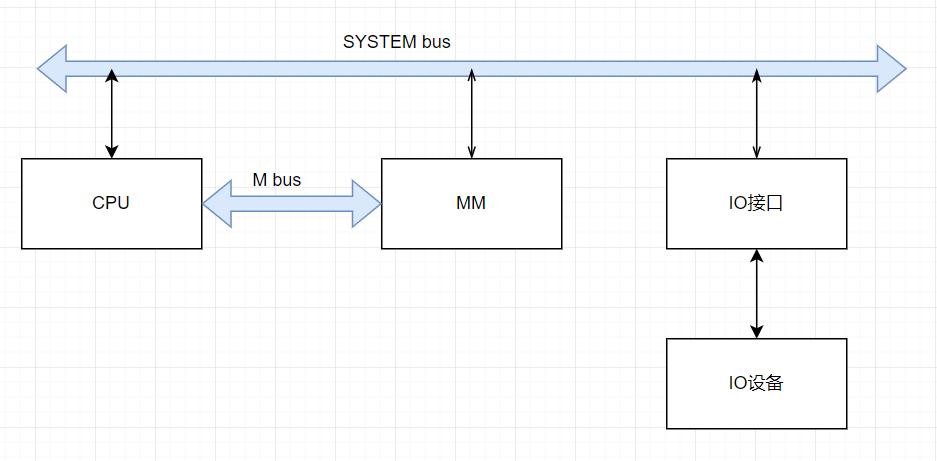

Dual Bus双总线结构

CPU-Centric Bus Architecture(以cpu为核心)

Drawbacks:

- cpu效率,cpu工作被外部设备和内存传输打断

Memory-Centric Bus Architecture(以存储器为核心)

Drawbacks:

- 目前双口ram还是不能进行并行

总线分类

1.on-chip bus&internal bus片内总线:芯片内部总线

2.system bus系统总线: 计算机各个部件的信息传输

-

数据总线 data bus 双向传输 机器字长、存储字长相关

-

地址总线 address bus 单向,cpu,主设备发出 Memory cell 相关,原型机里内和MAR位数一致

-

控制总线control bus 传入传出

3.communication bus通信总线

Bus characteristic:总线特性

1.机械特性 (mechanical characteristic):

形状,尺寸,管脚数,排列顺序

保证了总线接口的标准化

2.电气特性 (electrical characteristic):

传输方向,有效的电平范围

保证总线上信号的传输质量和完整性

3.功能特性(functional characteristic):

总线上每条信号线的功能

data,addr,control

4.时间特性(timing characteristic):

信号时序关系

Bus Performance Metric总线性能指标

Bus width:总线宽度,代表数据线的根数(默认描述datalines)

Bus Standard transfer rate:总线标准传输率 ,每秒传输的最大字节数 (MBps)

Clock Synchronization :时钟同步 ,同步不同步

Bus Multiplexing:总线复用,地址线数据线复用,目的为了减少管脚数量

Number of signal lines:信号线数 地址线数据线,控制线总和

总线控制方式: 突发、自动、逻辑、仲裁、计数

其他指标:负载能力 Throughput &load capacity

总线标准

ISA

EISA

VESA

AGP 连接控制芯片和显卡

PCIe(Peripheral Component Interconnect Express)

RS-232 串行通信总线标准

USB 串行接口总线标准

浙公网安备 33010602011771号

浙公网安备 33010602011771号