全国产V7+FT6678高性能实时信号处理平台

1、概述

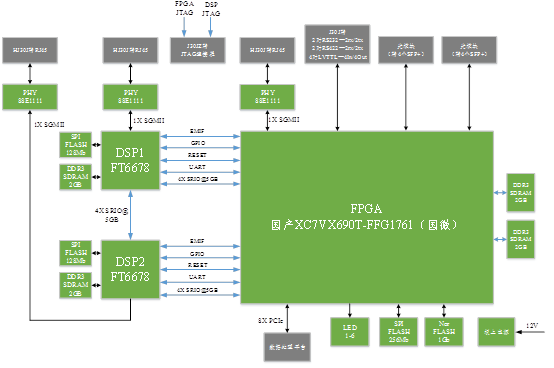

纯国产高性能实时信号处理平台组成如图1所示,包含1片性能不低于深圳国微的SMQ7VX690TFFG1761和两片性能不低于FT-6678(国防科大)的DSP,总共3个主芯片;每个主芯片外部各搭配1组64bit的DDR3内存模组以及各芯片启动配置所需要的存储芯片;采用提供8路以上SFP+(10Gbps),在面板上通过集成多束光接口实现,3路 10/100/1000M Ethernet(1FPGA和2个DSP 各1路),FPGA JTAG接口1个,DSP JTAG 1个,面板保留2路串口(1路RS422电平,1路RS232电平),通用GPIO≥6路LVTTL,提供PCIE3.0 X8接口;

互联接口:DCU板上3个主要计算芯片互联接口主要采用高速串行接口SRIO x 4,高速串行接口单lane速率拟定为5Gbps。

实时信号处理平台硬件实物图

实时信号处理平台硬件原理框图

2、硬件设计

整板尺寸(不含护角、接插件):宽x深x高=180×240×30(mm);

整板重量(不含AC/DC电源):小于1Kg;

整板供电:12VDC,插件采用4pin KPJX-4S-S电源插座;

3、外部接口:

1)以太网通信设计:FPGA路提供一路Base1000T的以太网口,通过HJ30J接口(可转成RJ45网口)前面板引出,用于与PC机通信;

2)光纤通信设计:FPGA路提供8路光纤接口,单路速率≥10Gbs,通过光纤接口前面板引出,一路可用于万兆网,另外可用于波前传感器通讯,接收图像数据或其他光纤数据通讯;

3)串口通信设计:FPGA路 J30J转2对RS232(2rx/2tx);转2对RS422(2rx/2tx);用于低速数据通讯;

4) I/O接口:FPGA路 J30J转4对I/O信号接口LVTTL(4发4收),用于低速数据通讯;

5)以太网通信设计:2片DSP分别引出两路Base1000T的以太网口,通过HJ30J接口(可转成RJ45网口),用于与PC机通信;

6)总线接口:提供一组PCIE3.0 X8接口用于高速数据通讯。

7)电源接口:输入电压12V;

计算性能:硬件用于计算的主芯片主要包含1片FPGA,型号采用深圳国微的SMQ7VX690TFFG1761,2片DSP芯片型号采用FT-6678(国防科大),总共3个主芯片,每个主芯片外部各搭配1组64bit的DDR3内存模组以及各芯片启动配置所需要的存储芯片;

4、平台内部模块连接关系:

(1)DSP选择国防科大FT-6678,FPGA选择深圳国微的SMQ7VX690TFFG1761;

(2)DSP与FPGA之间通信设计:两片DSP的 4x RapidI/O连接到FPGA,实现DSP与FPGA的RapidI/O通信;两片DSP的EMIF、GPIO和复位信号分别连接到FPGA;

(3)DSP之间通信设计:两片DSP片间采用4x RapidI/O互连,用于板间RapidI/O通信;

(4)存储功能:两个DSP分别外挂4片DDR3 SDRAM,每个DSP存储容量2GB;两个DSP总存储容量4GB;

(5)存储功能:FPGA外挂2组DDR3 SDRAM,每组4片DDR3 SDRAM组成,每组存储容量2GB,总存储容量4GB;

(6)存储功能:FPGA外挂2组FLASH,一组SPI FLASH,存储容量为256Mb;另一组为NorFlash,存储容量为1GB;可通过DSP向FLASH固化参数;

(7)两个DSP分别外挂1个FLASH,容量128Mb,可向FLASH固化参数;

(8)程序加载功能:FPGA通过SPI 4X 模式实现程序加载;DSP通过SPI 1X 模式实现程序加载;

5、性能指标:

FPGA主要功能:

a) 千兆网络传输,传输速率≥600Mbps

b) DDR读写,读写速率≥3200MB/s

c) SPI接口控制≥20Mbps

d) SRIO数据读写(x4模式),读写速率≥12Gbps

e) GPIO数据读写,读写速率≥160Mbps

f) Flash数据读写,读写速率≥18Mbps

g) 光纤数据读写,单个lane读写速率≥10Gbps

h) 串口发送接收,读写速率≥115200bps

i) 固件加载时间:FPGA固件程序从SPI FLASH加载时间不大于900ms。

n DSP功能:

j) SPI的bootloader程序

k) SRIO通讯(X4模式),读写速率≥12Gbps

l) 网络通讯,传输速率≥600Mbps

m) NorFlaah 程序 BOOT

n) EMIF数据读写,传输速率≥800Mbps

o) DSP通过SPI 1X 模式实现程序加载

6、 环境适应性:

1) 工作温度:-35℃~55℃

2) 存储温度:-40℃~60℃

3) 相对湿度:≤75%(25℃)

具有良好的防潮、防雨、防震、防沙尘、防霉(符合国军标 150.10A-2009《军用设备实验室环境实验方法 第 10 部分:霉菌试验》有关规定要求,霉菌试验后长霉等级应不大于 1 级)防冻、防盐雾(盐雾浓度: 6mg/m3)、耐日晒、防火、防锈蚀等设计。

实时信号处理平台设备,包含1片性能不低于深圳国微的SMQ7VX690TFFG1761和两片性能不低于FT-6678(国防科大)的DSP,总共3个主芯片;每个主芯片外部各搭配1组64bit的DDR3内存模组以及各芯片启动配置所需要的存储芯片;提供2个40Gbps高性能LCC48封装4路并行光收发一体模块 (分别可转出4路SFP+),在面板上通过集成多束光接口实现,3路 10/100/1000M Ethernet(1个FPGA和2个DSP各1路),FPGA JTAG接口1个,DSP JTAG 1个,面板保留4个串口(2对RS422电平,2对RS232电平),提供8路GPIO接口LVTTL(4发4收) ,串口和GPIO的接插件形式使用J30J接口(可转出ODU 7芯的接插件 ),提供PCIE3.0 X8接口;

实时信号处理平台设备,包含1片性能不低于深圳国微的SMQ7VX690TFFG1761和两片性能不低于FT-6678(国防科大)的DSP,总共3个主芯片;每个主芯片外部各搭配1组64bit的DDR3内存模组以及各芯片启动配置所需要的存储芯片;提供2个40Gbps高性能LCC48封装4路并行光收发一体模块 (分别可转出4路SFP+),在面板上通过集成多束光接口实现,3路 10/100/1000M Ethernet(1个FPGA和2个DSP各1路),FPGA JTAG接口1个,DSP JTAG 1个,面板保留4个串口(2对RS422电平,2对RS232电平),提供8路GPIO接口LVTTL(4发4收) ,串口和GPIO的接插件形式使用J30J接口(可转出ODU 7芯的接插件 ),提供PCIE3.0 X8接口;

浙公网安备 33010602011771号

浙公网安备 33010602011771号