【STM32】AFIO

单片机为充分利用引脚资源、优化引脚数目,常常为各个引脚添加复用功能,即一些引脚同时具有1个以上功能或者搭载了一个以上外设。对于STM32,其大多数引脚都具有复用功能。STM32F1系列设有一个专门的外设管理这些功能,即AFIO(Alternate Function I/O,复用功能I/O)。AFIO有三大核心功能:复用功能映射、调试端口配置、外部中断配置。本文将以STM32F1系列为例,分别介绍AFIO的组成及各功能。

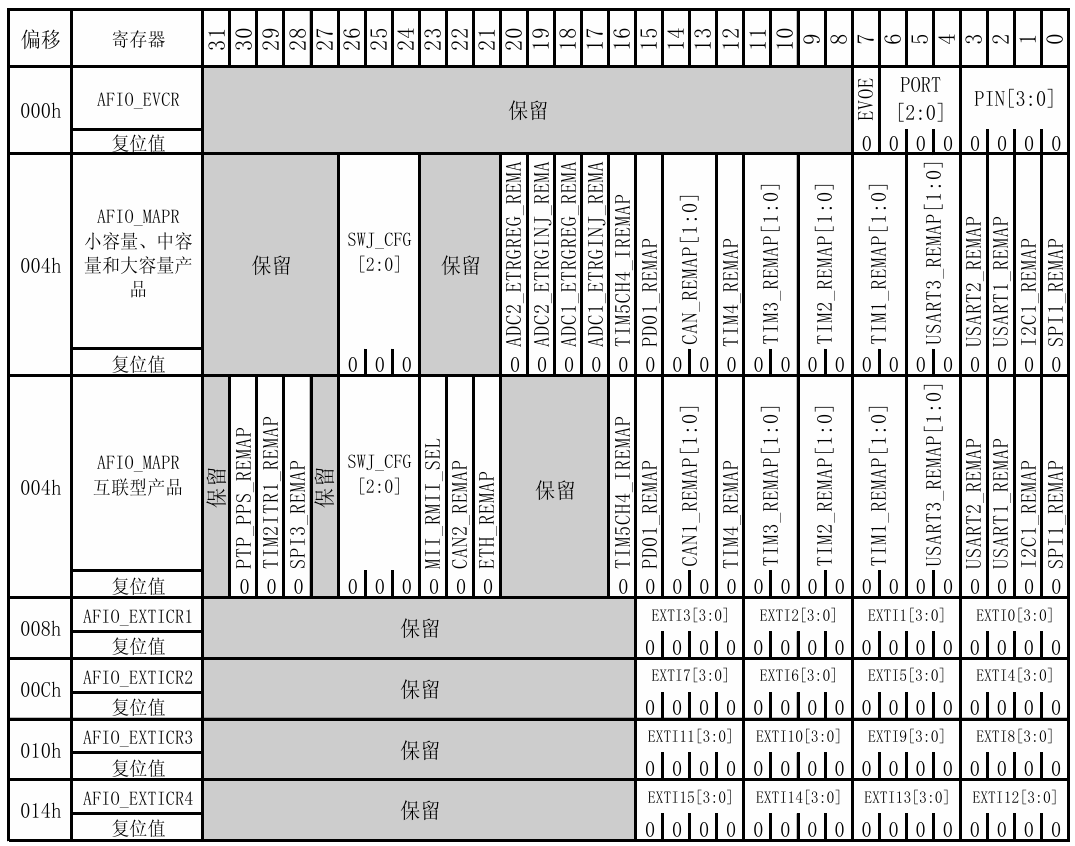

AFIO外设在内存中的寻址范围为0x40010000~0x400103FF,在STM32F1中,AFIO的核心寄存器寻址范围为0x40010000~0x4001001F,包括事件控制寄存器、复用重映射调试I/O配置寄存器以及外部中断配置寄存器,偏移地址及位功能如下表所示,了解这些寄存器功能便能掌握AFIO外设的功能和使用,下面将分别对各寄存器加以详细介绍。

事件控制寄存器EVCR

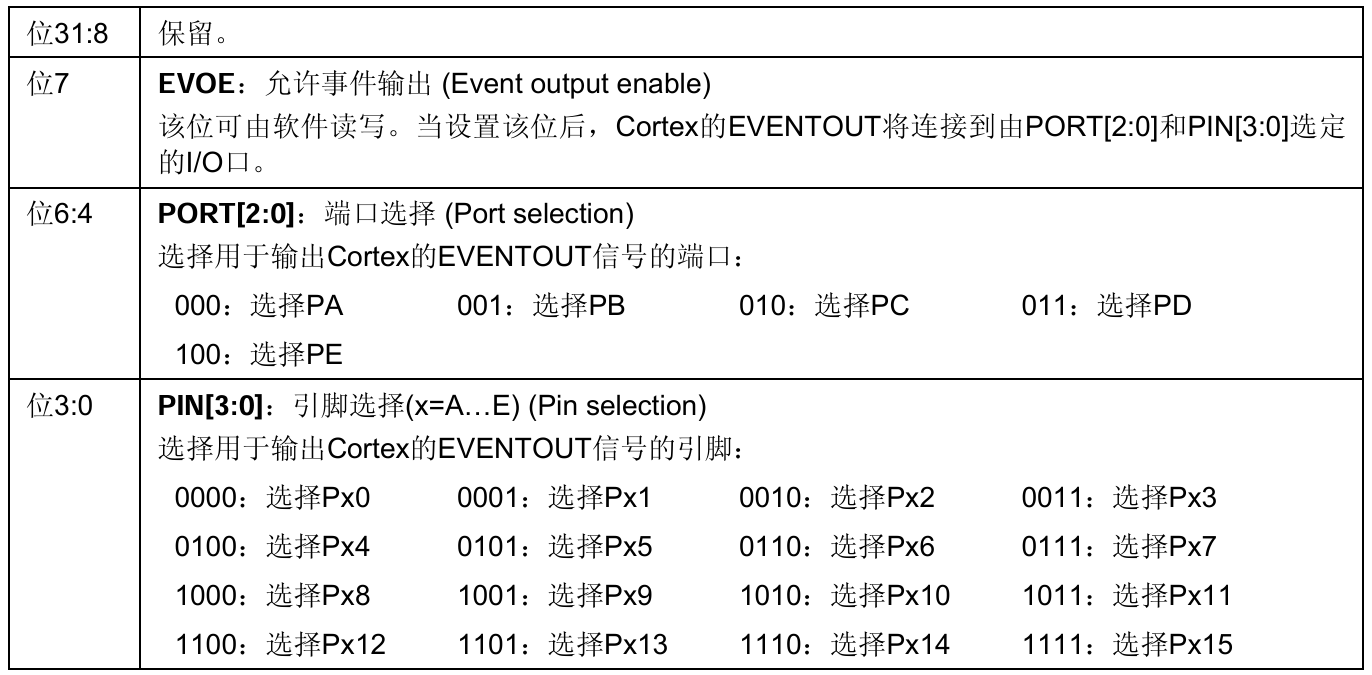

事件控制寄存器(Event Control Register,EVCR)是AFIO外设用于配置事件输出功能的寄存器,通过控制把STM32内部事件映射到指定GPIO引脚,以实现外部设备同步或触发控制。EVCR内存地址为0x40010000,复位值为0x00000000,其高24位保留,仅低8位有定义且可读可写,该8位功能定义如下表:

简单来说,就是低7位分别配置使用的端口及引脚,第8位(bit7)用于控制使能EVENTOUT(事件输出)。

复用重映射和调试I/O配置寄存器MAPR

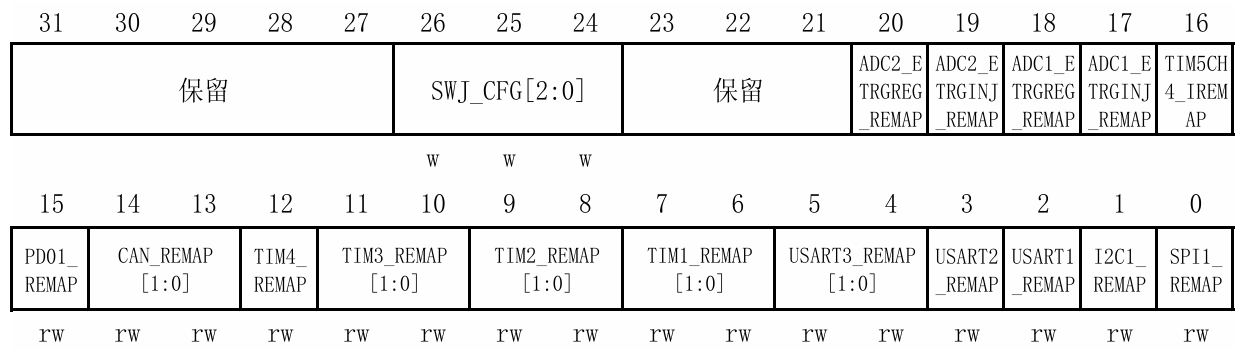

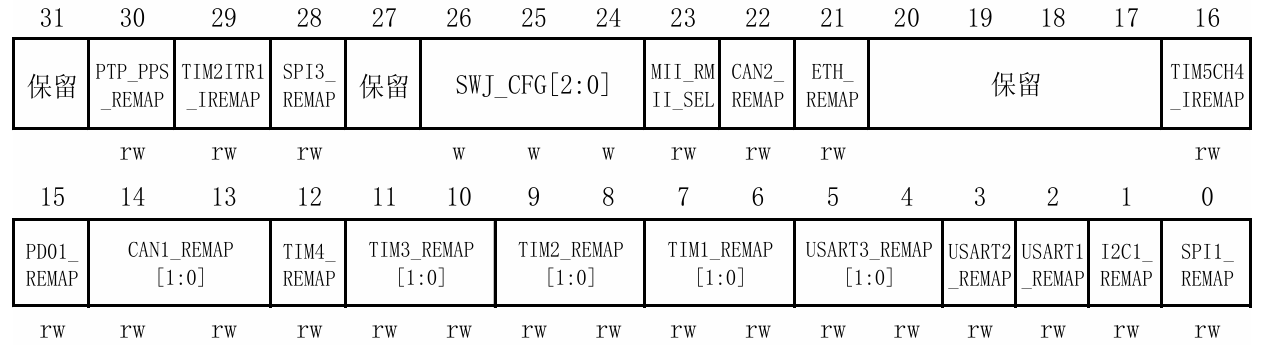

复用重映射和调试I/O配置寄存器(Remap and Debug I/O Configuration Register,MAPR)主要用于配置外设功能重映射以及控制调试端口的使能状态,其内存地址为0x40010004,复位值为0x00000000,寄存器除了bit[26:24]三位配置JTAG调试接口为只写模式外,其他为均为可读可写,且互联型系列和非互联型系列稍有不同。

上图为非互联型产品MAPR位定义,其中bit[26:24]三位是调试控制位,用于配置调试相关功能,为只写位。其他位均可读可写,用于重映射相关配置。

上图为互联型产品MAPR位定义,STM32F1系列中F105和F107子系列为互联型产品,相比非互联型产品添加了以太网支持等相关功能。在MAPR寄存器上,其bit[26:24]与非互联型产品对应位功能相同,均为调试功能的相关配置位,且两个系列的bit[0:16]低17位也完全相同。下面将先介绍两者相同部分,然后分别介绍不同部分。

串行线JTAG配置(SWJ_CFG)

MAPR的bit[26:24]三位被用于控制JTAG(Joint Test Action Group) 和SWD(Serial Wire Debug) 两种调试接口的使能状态,JTAG和SWD是STM32支持的两种调试方式,其在STM32F1系列中默认引脚分配如下表:

其中,Trace引脚一般支持较少。SWD只需两个引脚,JTAG需要5个引脚,且JTAG默认引脚分配中共用了SWD的引脚。通过配置SWJ_CFG可以实现调控两种调试方式的开启和关闭,使得调试期间获得更多空闲可利用GPIO。SWJ_CFG所在的三个bit是只写位,强行读取将会返回未定义的数值,即返回值无意义,SWJ_CFG不同取值对应功能如下表(其他未提及的取值均未定义):

其中,由于PB3有一个Trace的TRACESWO复用功能,若单片机支持异步跟踪(Trace),在使用该功能时,PB3不能被释放作为一般GPIO端口使用。

复用重映射

在存储器映射一文中,我们粗略了解了STM32F1的地址分配以及存储器映射,并了解到片上外设均被映射到了内存的外设区,不同外设对应不同型号有固定的地址以及I/O端口。为了更方便灵活地调动I/O引脚资源,STM32支持对默认的端口映射进行修改,该修改过程被称为重映射,而修改控制就是通过配置寄存器MAPR实现。

bit0

bit0控制

S

P

I

1

SPI1

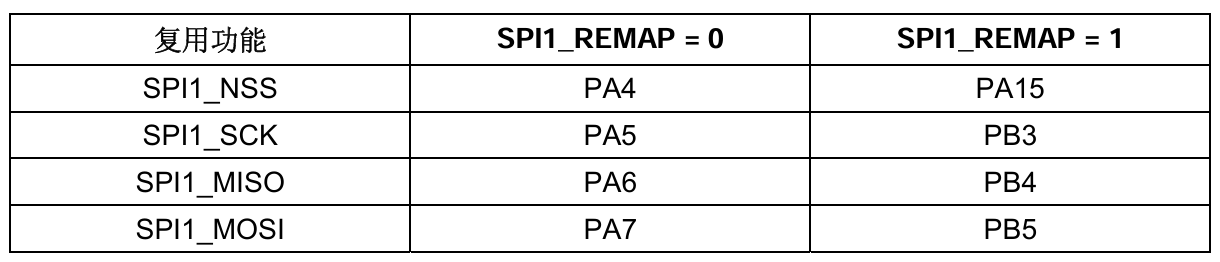

SPI1的端口重映射,默认引脚分配为对应位为0时的情况。

bit1

控制

I

2

C

1

I^2C1

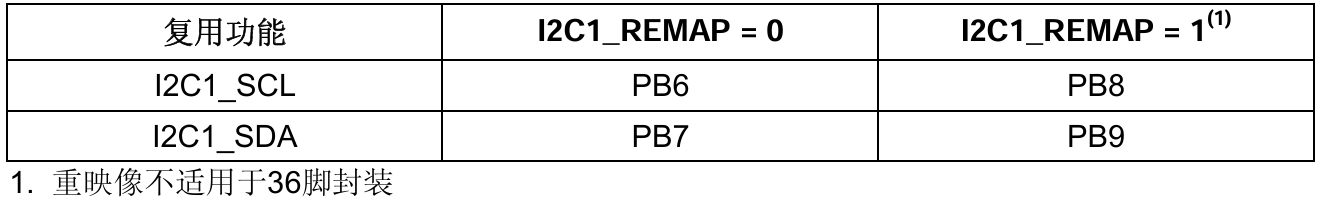

I2C1端口重映射。

bit2

控制

U

S

A

R

T

1

USART1

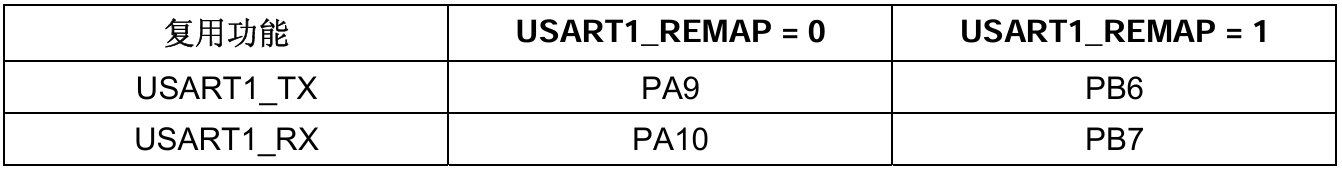

USART1端口重映射。

bit3

控制

U

S

A

R

T

2

USART2

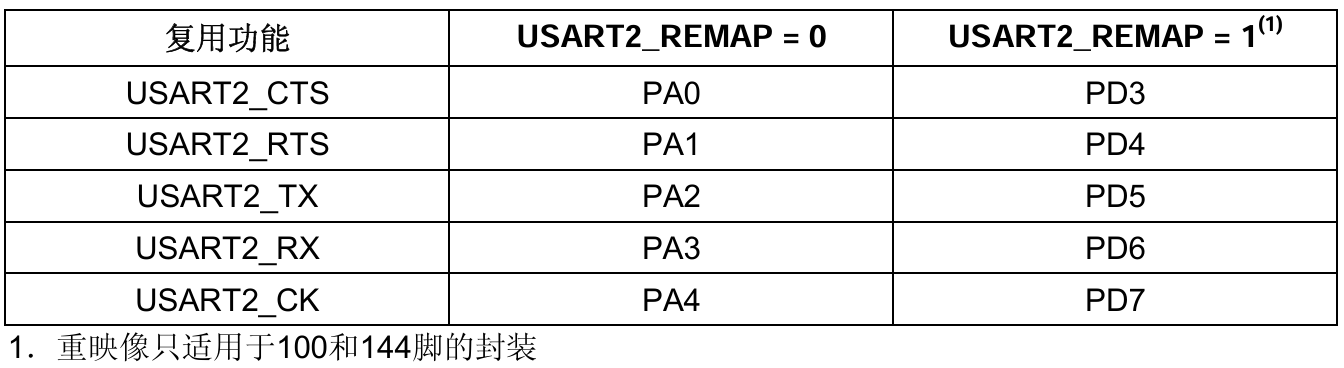

USART2端口重映射。

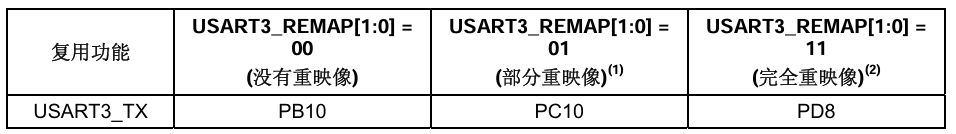

bit[5:4]

控制

U

S

A

R

T

3

USART3

USART3端口重映射。

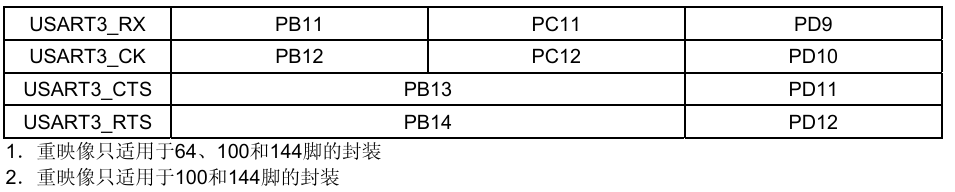

bit[7:6]

控制

T

I

M

1

TIM1

TIM1端口重映射。

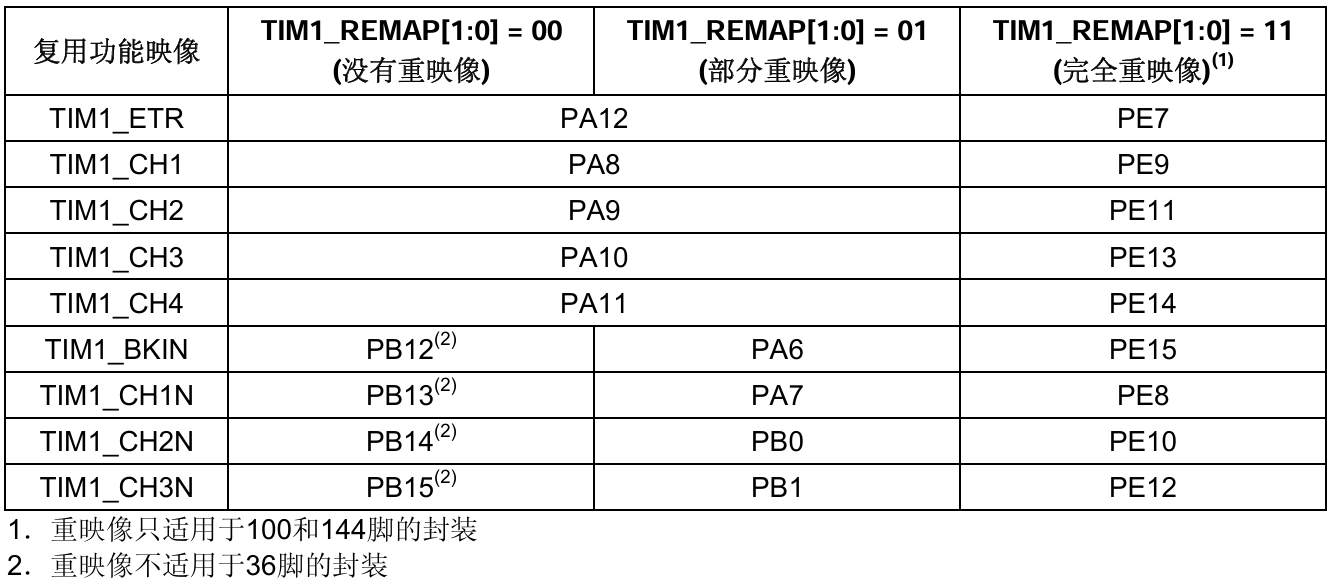

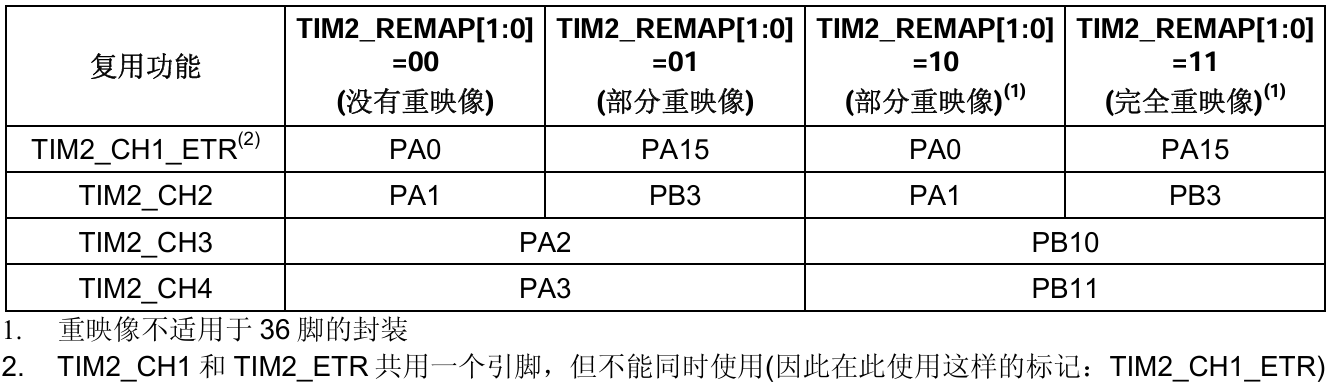

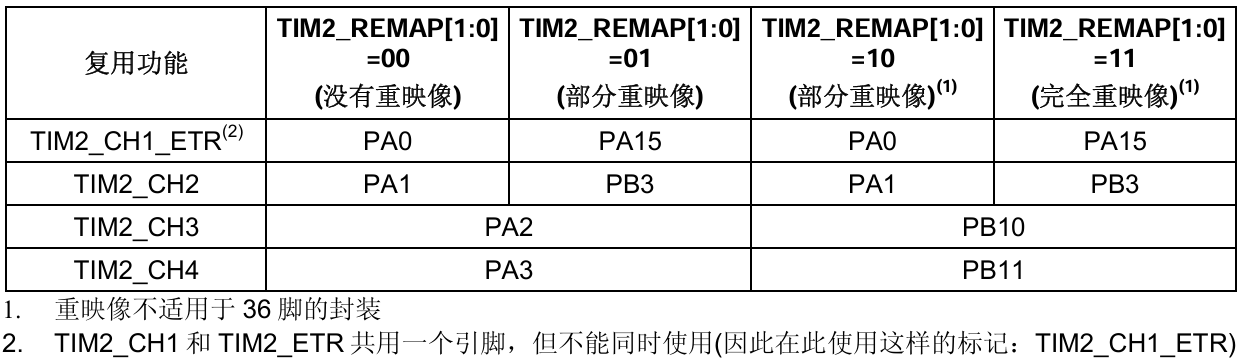

bit[9:8]

控制

T

I

M

2

TIM2

TIM2端口重映射。

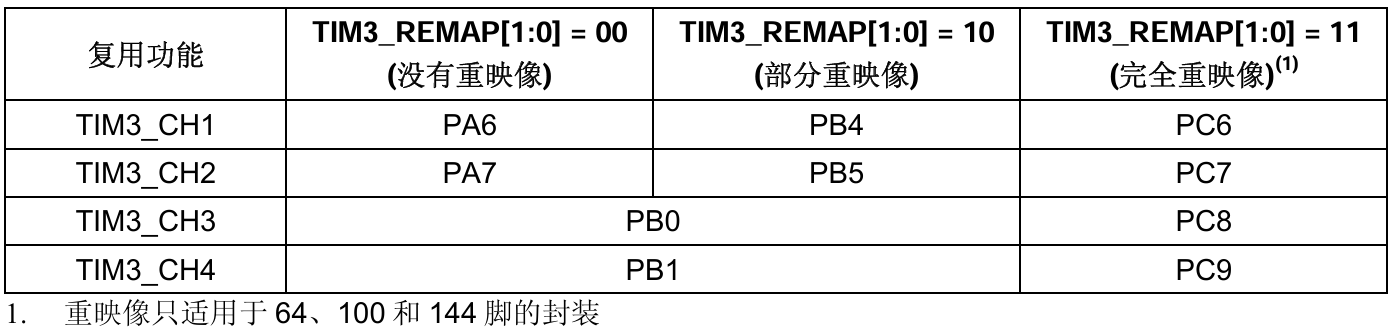

bit[11:10]

控制

T

I

M

3

TIM3

TIM3端口重映射。

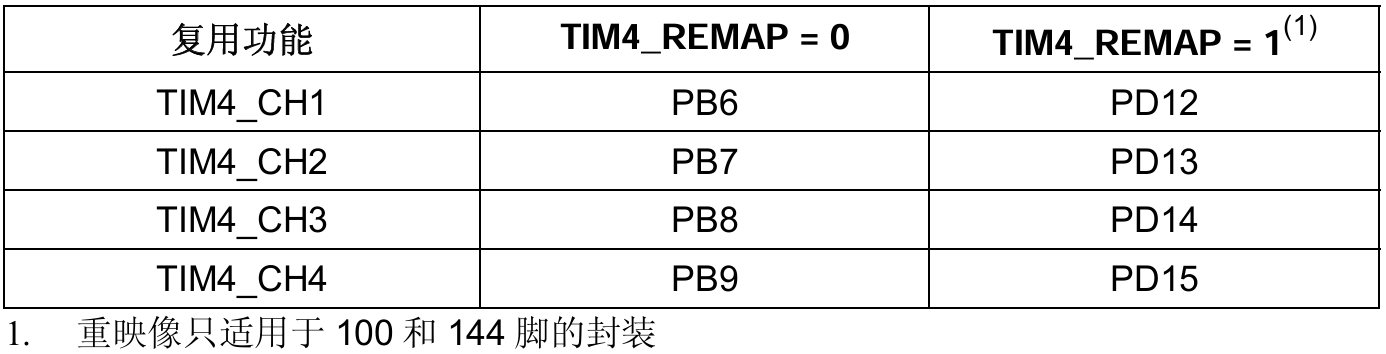

bit12

控制

T

I

M

4

TIM4

TIM4端口重映射。

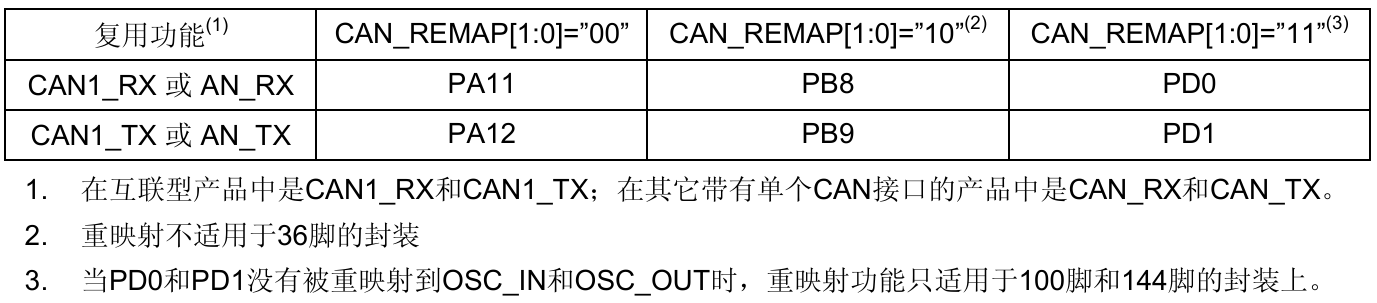

bit[14:13]

控制

C

A

N

CAN

CAN端口重映射。

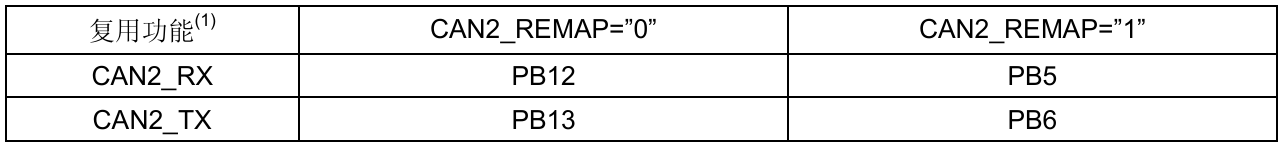

对于互联型产品,还有CAN2接口,这部分在后面说明。

bit15

控制

P

D

01

PD01

PD01端口重映射。

该位控制端口PD0/端口PD1映像到OSC_IN/OSC_OUT(Port D0/Port D1 mapping on OSC_IN/OSC_OUT)。当不使用主振荡器HSE(系统运行于内部的8MHz阻容振荡器)时,通过对该位置1,可以使PD0和PD1映像到OSC_IN和OSC_OUT引脚。此功能只能适用于36、48和64引脚的封装(PD0和PD1出现在100脚和144脚的封装上,不必重映像)。

当仅仅是LSE振荡器关闭时,LSE振荡器引脚OSC32_IN/OSC32_OUT可以分别用做GPIO的PC14/PC15,LSE功能始终优先于通用I/O口的功能。

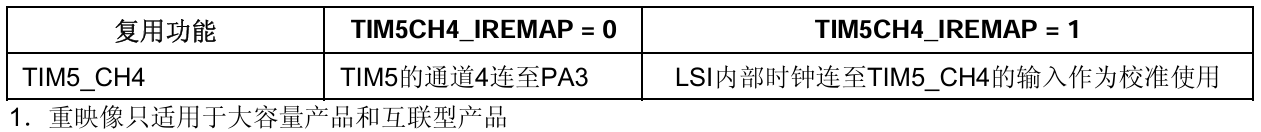

bit16

控制

T

I

M

5

C

H

4

TIM5CH4

TIM5CH4端口重映射。

bit17

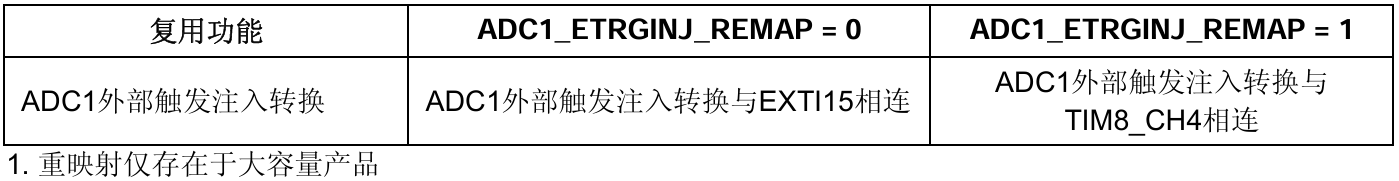

非互联型产品该位用于ADC1_ETRGINJ端口重映射配置,互联型产品该位为保留位。

bit18

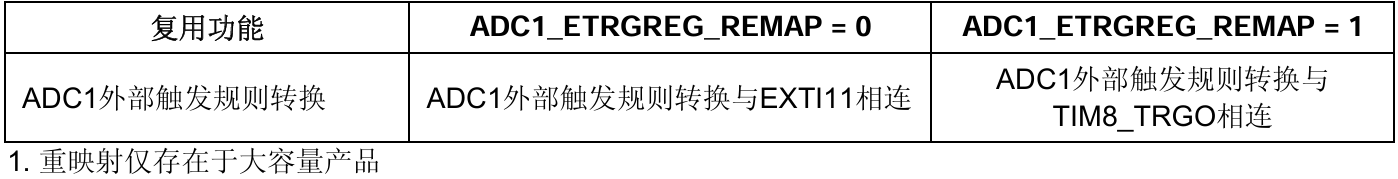

非互联型产品该位用于ADC1_ETRGREG端口重映射配置,互联型产品该位为保留位。

bit19

非互联型产品该位用于ADC2_ETRGINJ端口重映射配置,互联型产品该位为保留位。

bit20

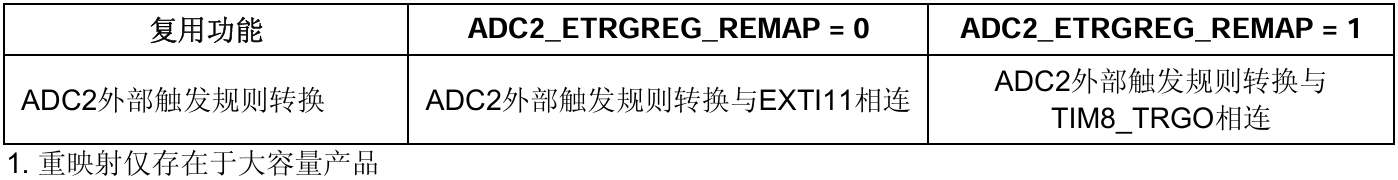

非互联型产品该位用于ADC2_ETRGREG端口重映射配置,互联型产品该位为保留位。

bit21

非互联型产品该位为保留位,互联型产品该位用于ETH端口重映射配置。

bit22

非互联型产品该位为保留位,互联型产品该位用于CAN2端口重映射配置。

bit23

非互联型产品该位为保留位,互联型产品该位用于MII_RII_SEL(MII or RMII selection,MII或RMII选择)端口重映射配置。它配置内部的以太网MAC使用外部的MII接口还是RMII接口的收发器(PHY)。

0:配置以太网的MAC使用外部MII接口的收发器(PHY);

1:配置以太网的MAC使用外部RMII接口的收发器(PHY)。

bit27

该位为保留位。

bit28

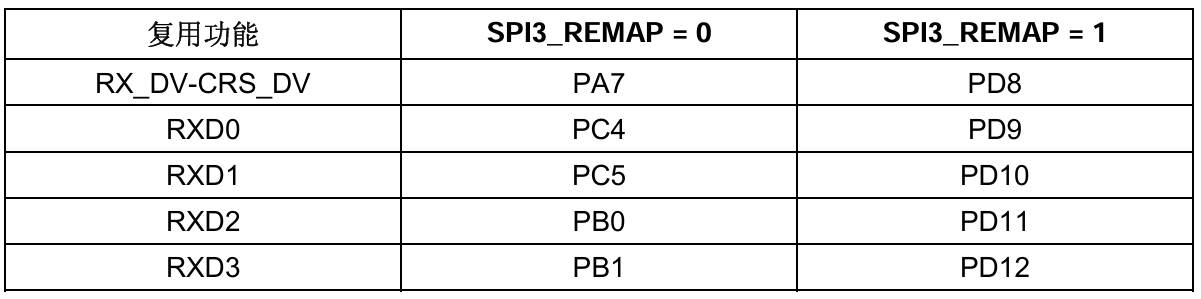

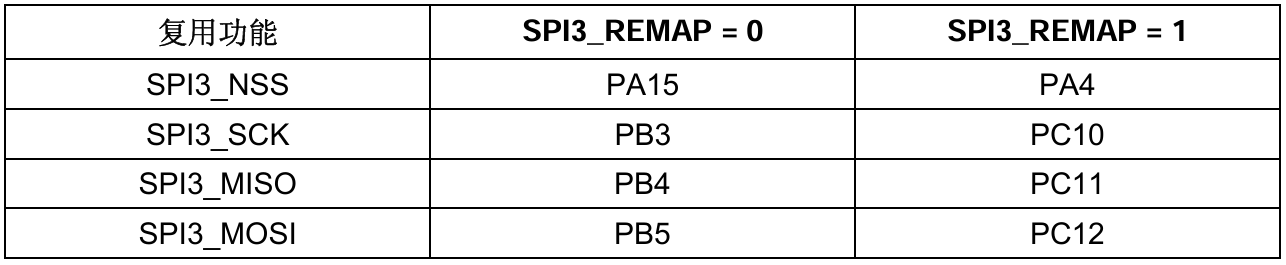

非互联型产品该位为保留位,互联型产品该位用于SPI3端口重映射配置。

bit29

非互联型产品该位为保留位,互联型产品该位用于TIM2ITR1端口重映射配置。

bit30

非互联型产品该位为保留位,互联型产品该位用于以太网PTP_PPS端口重映射(Ethernet PTP PPS remapping)配置。该位可由软件置’1’或置’0’。它允许以太网MAC的PPS_PTS输出到PB5引脚。

0:PTP_PPS不输出到PB5引脚;

1:PTP_PPS输出到PB5引脚。

bit31

该位为保留位。

外部中断配置寄存器EXTICR

外部中断配置寄存器共有4个,分别为AFIO_EXTICR1`AFIO_EXTICR1`,每个寄存器都是低16位有效,高16位保留,每个寄存器都可读可写。每个寄存器管理4条中断线,共同将16条外部中断线(`EXTI0`EXTI5)映射到具体GPIO端口。每个寄存器的地址偏移和对应功能如下表:

其中,每4个字段对应选择中断线映射的GPIO端口,以EXTI0[3:0]为例,有:

| EXTI[3:0] | GPIO端口 |

|---|---|

| 0000 | GPIOA |

| 0001 | GPIOB |

| 0010 | GPIOC |

| 0011 | GPIOD |

| 0100 | GPIOE |

| 0101 | GPIOF |

| 0110 | GPIOG |

浙公网安备 33010602011771号

浙公网安备 33010602011771号