IIC协议学习笔记

IIC总线(Inter-Integrated Circuit)即集成电路总线,是PHILIPS公司设计出来的一种简单、双向、二线制、同步串行总线。IIC总线是一个多向控制总线,多个器件(从机)可以同时挂载到一个主机控制的一条总线上。每个连接在总线上的设备都是通过唯一的地址和其他器件通信,主机和从机的角色可互换,

主机和从机的概念。主机就是负责整个系统的任务协调与分配,从机一般是通过接收主机的指令从而完成某些特定的任务,主机和从机之间通过总线连接,进行数据通讯。我们平时使用的个人电脑也就是这个概念。

IIC协议为半双工协议。

全双工指在发送数据的同时也能够接收数据,两者同步进行。目前的网卡一般都支持全双工。

半双工就是指一个时间段内只有一个动作发生,早期的对讲机、以及早期集线器等设备都是基于半双工的产品。

还有一种单工通信是指通信线路上的数据按单一方向传送.。

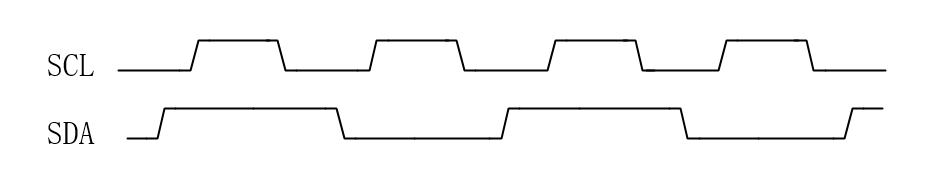

数据有效传输在scl信号的高电平期间,sda数据线保持稳定,在scl为低电平时允许sda数据线变化。

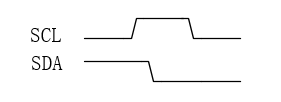

起始条件在scl为高电平期间,sda出现下降沿,则为起始信号。

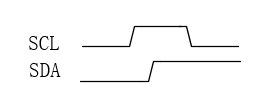

结束条件在scl为高电平期间,sda出现上升沿,则为结束信号。

总结:当scl为高电平的时候,sda为出现下降沿为start位, sda出现上升沿为stop位,所以在scl为高电平的时候sda应该保持稳定不能随意乱动。这就又回到了数据传输有效的条件,只有在scl为低电平期间,才允许数据变化,在高电平期间,不允许数据变化,否则就会出现起始位或结束位。

应答(ACK,Acknowledgement)。即确认字符,在数据通信中,接收站发给发送站的一种传输类控制字符。主机每向从机发送完一个字节的数据,主机总是需要等待从机给出一个应答信号,来确认从机是否成功接收到了数据,从机应答主机所需要的时钟也是由主机提供的,应答出现在每一次主机完成8个数据位传输后紧跟着的时钟周期,低电平0表示应答,1表示非应答。,需要应答时,数据发出方将SDA总线设置为3态输入,由于IIC总线上有上拉电阻,因此此时总线默认高电平,若数据接收方正确接收到数据,则数据接收方将SDA总线拉低,以示正确应答。

IIC传输时时从MSB开始传输到LSB结束。MSB是Most Significant Bit的缩写,最高有效位。在二进制数中,MSB是最高加权位。与十进制数字中最左边的一位类似。通常,MSB位于二进制数的最左侧,LSB位于二进制数的最右侧。LSB,英文 least significant bit,中文义最低有效位。

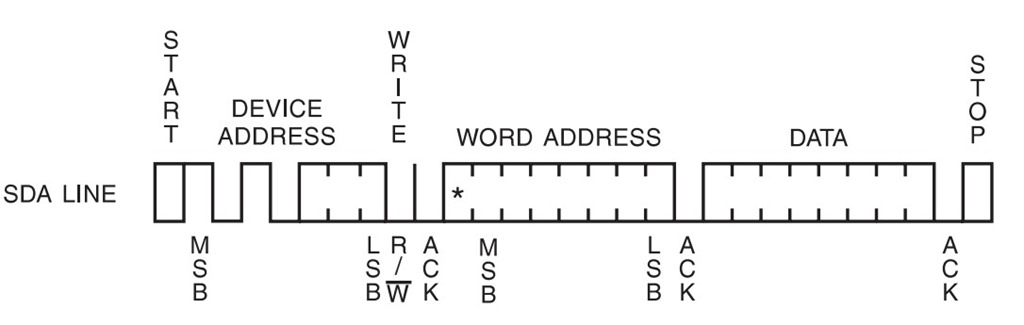

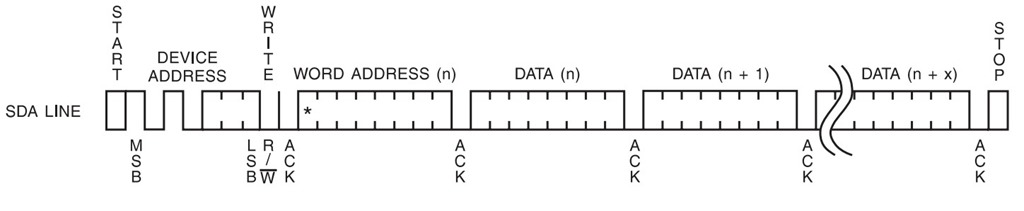

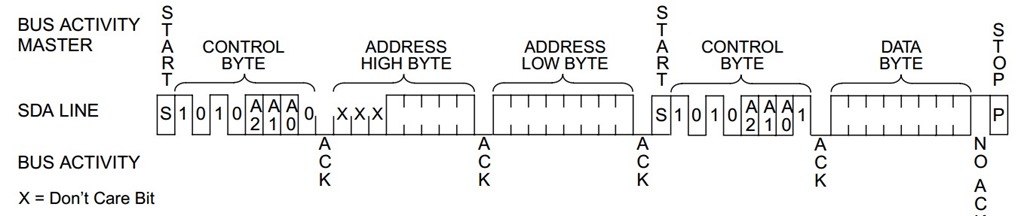

IIC写时序

ID_Address, REG_Address, W_REG_Data

(1) 产生start位

(2) 传送器件地址ID_Address,器件地址的最后一位为数据的传输方向位,R/W,低电平0表示主机往从机写数据(W),1表示主机从从机读数据(R)。ACK应答,应答是从机发送给主机的应答,这里不用管。

(3) 传送写入器件寄存器地址,即数据要写入的位置。同样ACK应答不用管。

(4) 传送要写入的数据。ACK应答不用管。

(5) 产生stop信号。

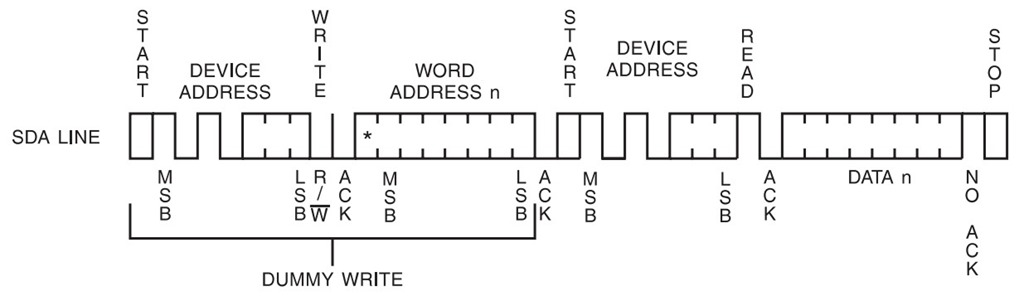

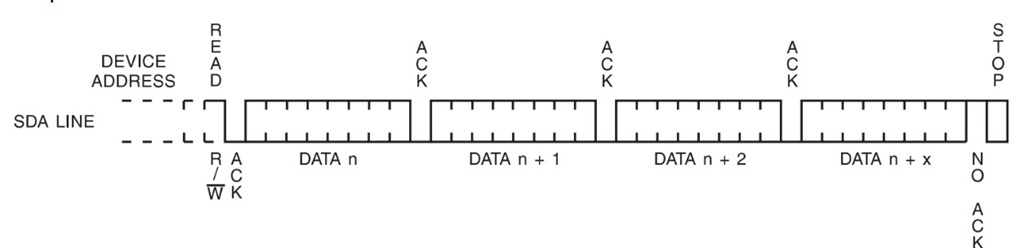

IIC读时序

{ID_Address + REG_Address} + {ID_Address + R_REG_Data}

(1) 产生start信号

(2) 传送器件地址(写ID_Address),ACK。

(3) 传送字地址(写REG_Address),ACK。

(4) 再次产生start信号

(5) 再传送一次器件地址,ACK。

(6) 读取一个字节的数据,读数据最后结束前无应答ACK信号。

(7) 产生stop信号。

从时序图上可以看出,IIC读时序要写两次器件地址,刚开始接触的时候我也很疑惑 dummy write。我个人这样理解这里,首先传送器件地址到总线上找到器件,然后写入寄存器地址,也就是word address找到需要读取数据的地址,但并不是真正的写入数据所以叫做dummy wirte(假写)。然后再传输一次器件地址后开始读数据。

IIC协议在读写数据时,总是要发送器件地址,这里需要注意的是,不是主机给从机发送地址,而是主机给地址总线上发送地址,挂IIC总线上的所有从机都能收到地址,如果发过来的地址和自己的地址匹配上了,从机就会给主机一个应答,这样就建立起来了一个通讯。所以我在想,如果从机的器件是完全一样的,那么IIC协议就可以同时给多个从机,即对多个器件进行配置。这种理论上是可行的,但其实是不行的,IIC协议就是通过地址不同来判断给哪个器件传送数据的,如果两个器件的地址完全一样,器件会产生应答,那么两个器件就通过竞争判断给谁通信了,有随机性。即IIC协议一次只能和一个设备/器件进行通讯。

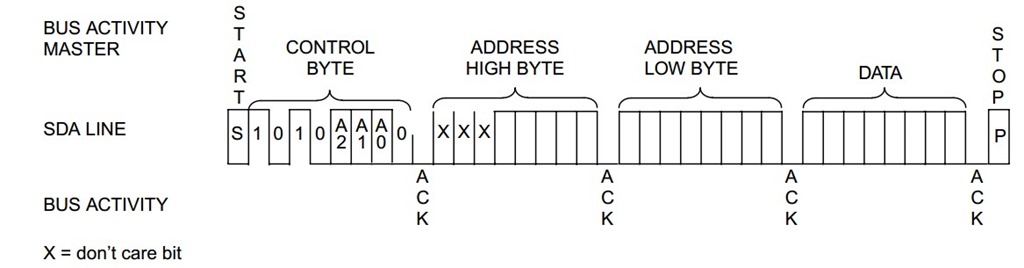

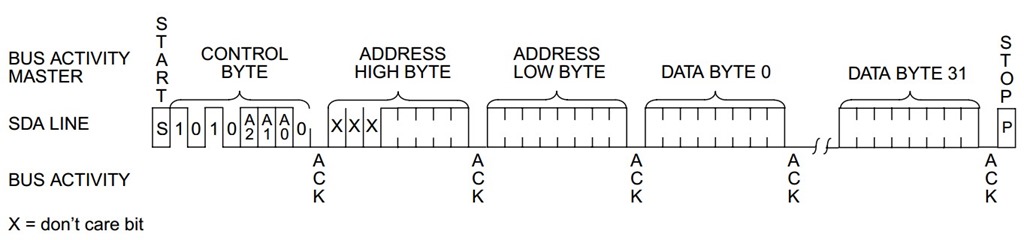

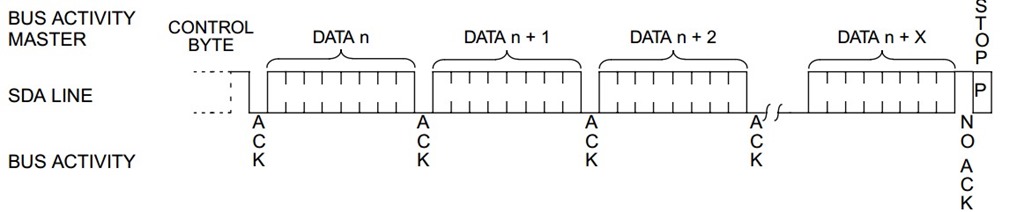

IIC读写时序补充

双字节地址写时序,写入器件地址,写入寄存器地址高位、低位,然后写数据。

多数据写时序,写入器件地址,写入寄存器地址,连续写入数据。

双字节地址多数据写时序,写入器件地址,写入寄存器地址高位、低位,然后连续写入数据。

双字节地址读时序,写入器件地址,写入寄存器地址高位、低位,然后再次写入器件地址,写入数据。读数据最后结束前无应答ACK信号。

多数据读时序,写入器件地址,写入寄存器地址,,然后再次写入器件地址,连续写入数据。读数据最后结束前无应答ACK信号。

双字节地址多数据读时序,写入器件地址,写入寄存器地址,,然后再次写入器件地址,连续写入数据。读数据最后结束前无应答ACK信号。

转载请注明出处:NingHeChuan(宁河川)

个人微信订阅号:开源FPGA

如果你想及时收到个人撰写的博文推送,可以扫描左边二维码(或者长按识别二维码)关注个人微信订阅号

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/8595423.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号