电子丨阻抗计算

在电路板(PCB)设计中,阻抗是指导体中交流电(AC)所遇到的阻碍,包括电阻(R)、电感(L)、电容(C)的综合效应,通常用复数表示(Z = R + jX)。在高频信号或高速数字电路中,阻抗匹配至关重要,以下是详细说明:

1. 阻抗的组成

- 直流电阻(R):导体本身的电阻,由材料(如铜)和几何形状决定。

- 感性电抗(jωL):高频下导体的自感效应(如走线长度增加电感)。

- 容性电抗(1/jωC):导体间绝缘介质(如FR4)和间距形成的寄生电容。

2. 为什么需要阻抗计算?

(1) 信号完整性(SI)

- 反射抑制:当信号传输线阻抗与源/负载阻抗不匹配时,会发生反射(如50Ω系统需匹配50Ω走线),导致信号振铃、过冲或失真。

- 高频损耗:高频信号(如GHz级)对阻抗敏感,不匹配会加剧衰减和相位畸变。

(2) 电磁兼容性(EMC)

- 辐射控制:阻抗失配会导致能量辐射(如天线效应),引发EMI问题。

- 串扰减少:精确计算差分对阻抗(如100Ω差分线)可降低邻近信号干扰。

(3) 功率传输效率

- 射频/RF电路:阻抗匹配(如50Ω)确保最大功率传输,减少能量反射损耗。

(4) 高速协议要求

- 如USB、PCIe、DDR:协议严格规定阻抗容差(如±10%),否则可能导致时序错误或眼图闭合。

3. 阻抗计算的关键参数

- 特性阻抗:由走线宽度(W)、厚度(T)、介质高度(H)、介电常数(Dk)决定。

- 微带线(Microstrip):表面走线,常用公式:

\[Z_0 \approx \frac{87}{\sqrt{\varepsilon_r +1.41}} \ln \left( \frac{5.98H}{0.8W + T} \right) \]- 带状线(Stripline):内层走线,受上下介质影响。

- 差分阻抗:与线间距(S)相关,需平衡奇模/偶模阻抗。

4. 实际设计中的考虑

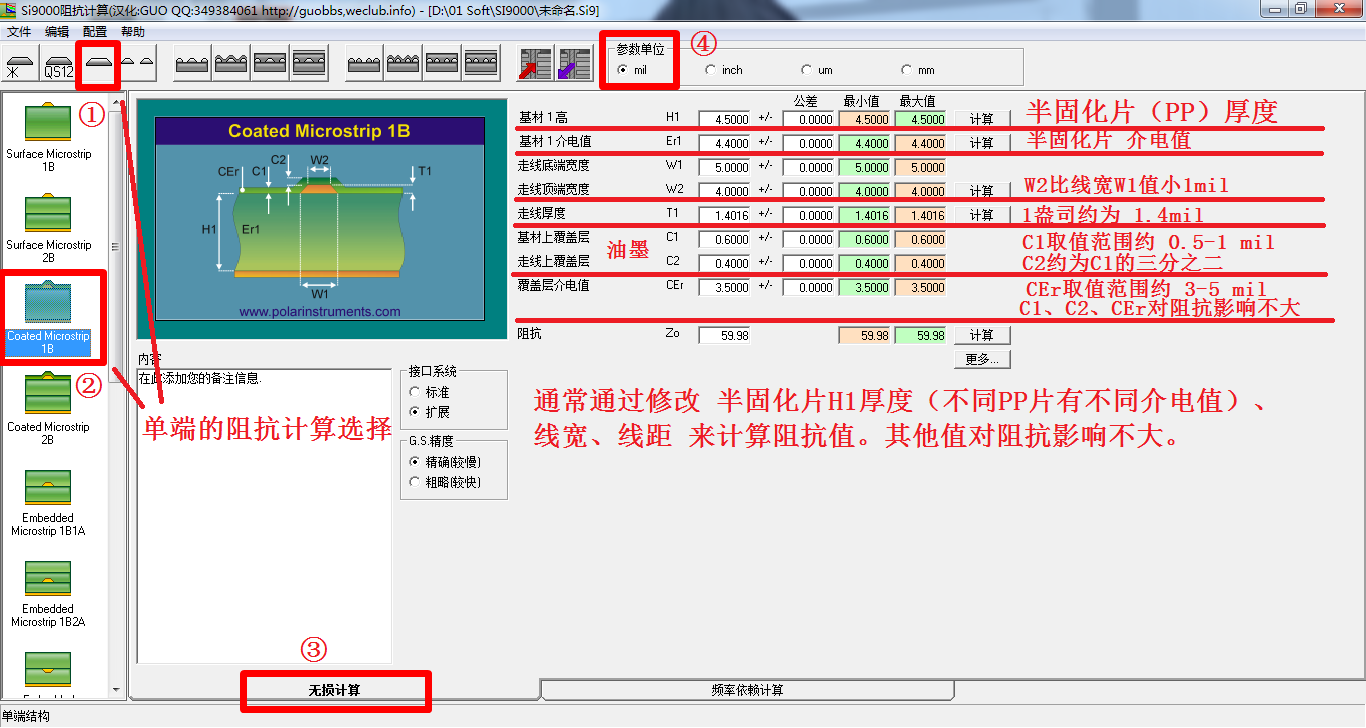

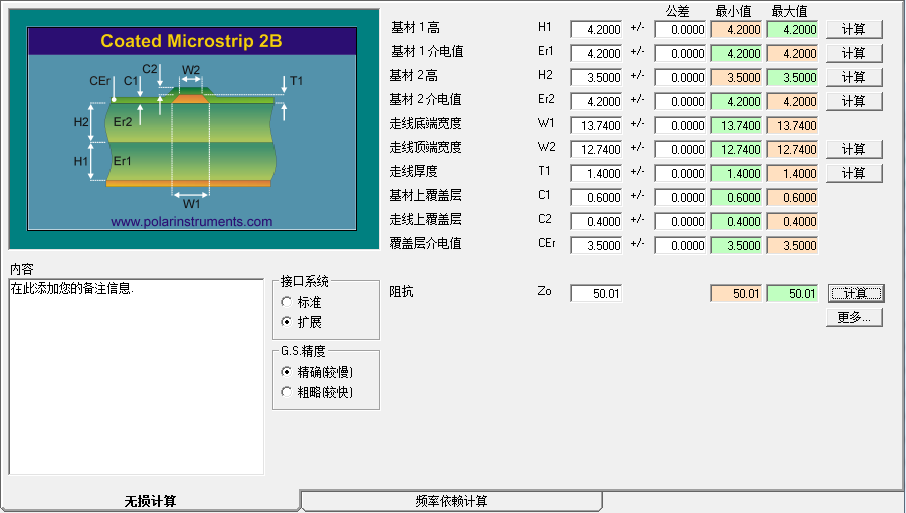

- 使用工具:SI9000。

- 制程误差:阻抗计算误差可在±10Ω。

- 叠层设计:

- 通常通过调整“半固化片PP介质厚度、介电常数、线宽、线距”来控制阻抗。

- 叠层厚度上下最好对称,否则板子容易变形。

- 高频板子,其介电常数越小越好。

- 类比理解:

- 半固化片PP:胶水

- 芯板CORE:双面板

- 共面阻抗:当走线的两端有包地时使用的模型。

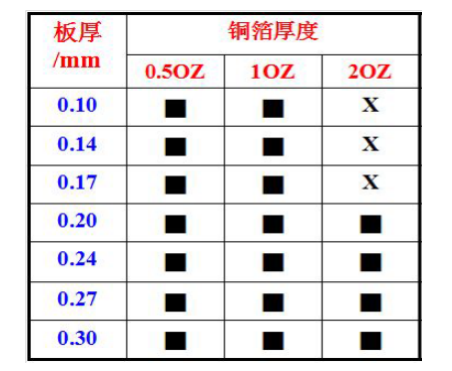

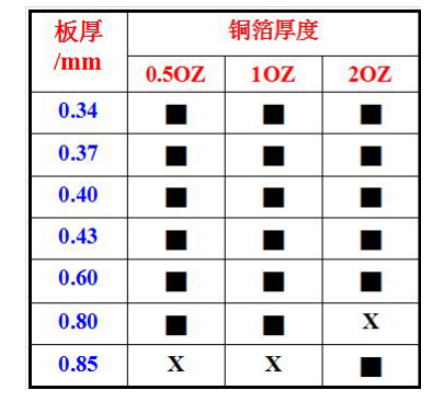

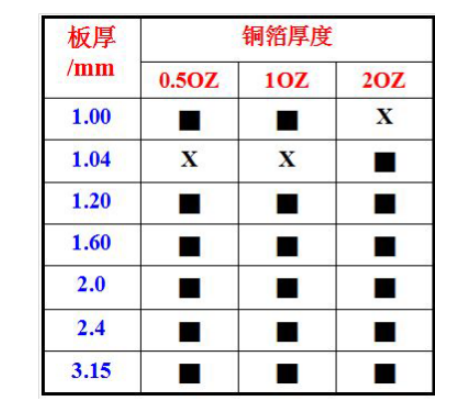

- 铜厚选择:TOP/BOTTOM通常用1OZ(≈35um≈1.4mil),内层0.5OZ,若VCC有大电流内层可考虑换成1OZ。

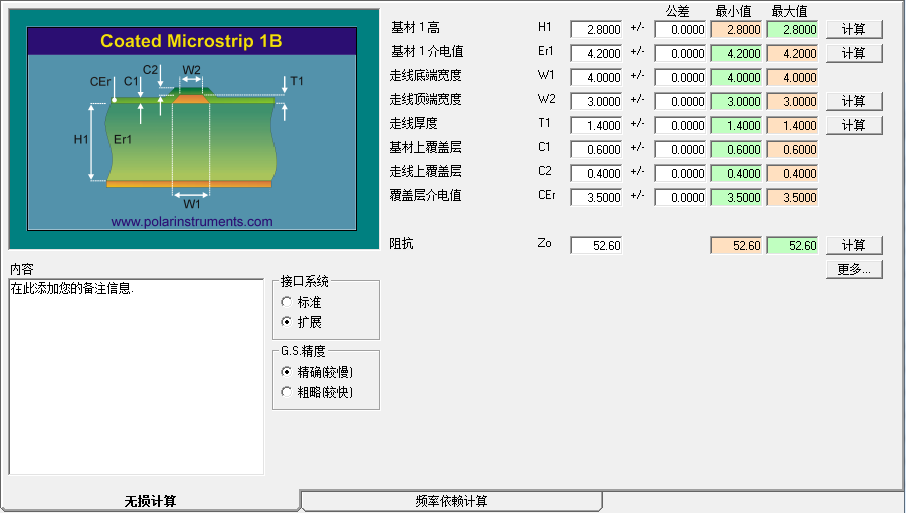

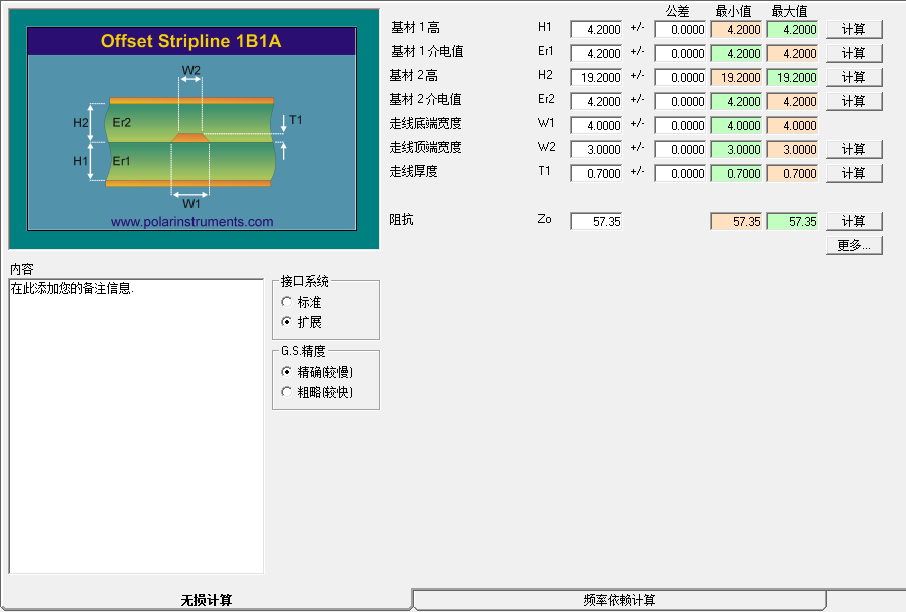

- 工具说明:

5. 示例场景

| 阻抗值 | 信号类型 | 应用 |

|---|---|---|

| 50Ω | 单端 | RF天线(建议 10mil 以上,防止信号衰减严重)、DDR(地址/控制) |

| 90Ω | 差分 | USB |

| 100Ω | 差分 | HDMI,LVDS,DP,MIPI,网口,DDR_CLK,DDR_DQS |

6. 常规板料(FR-4)的厚度规格、铜箔厚度选择参考

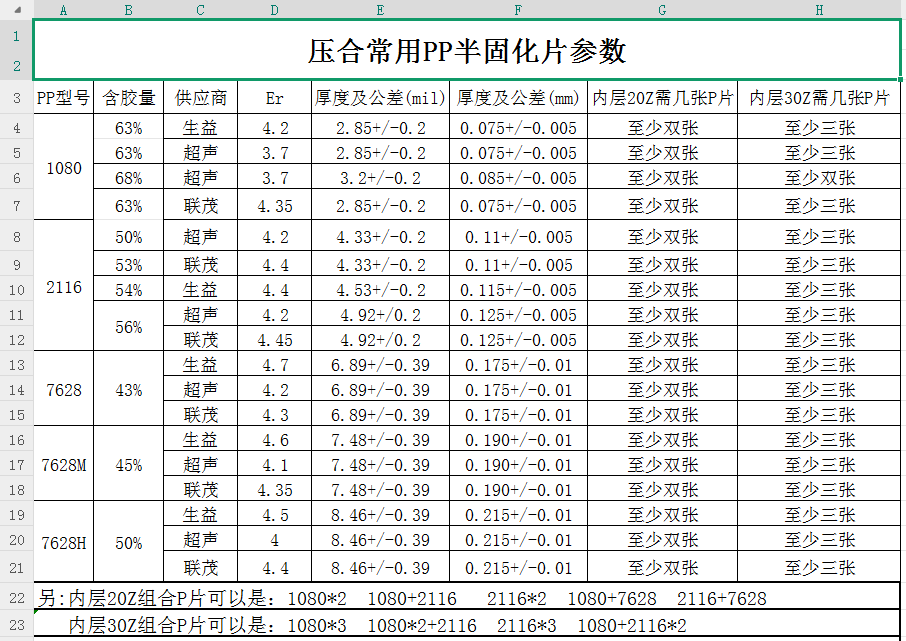

7. 常用PP半固化片参数参考

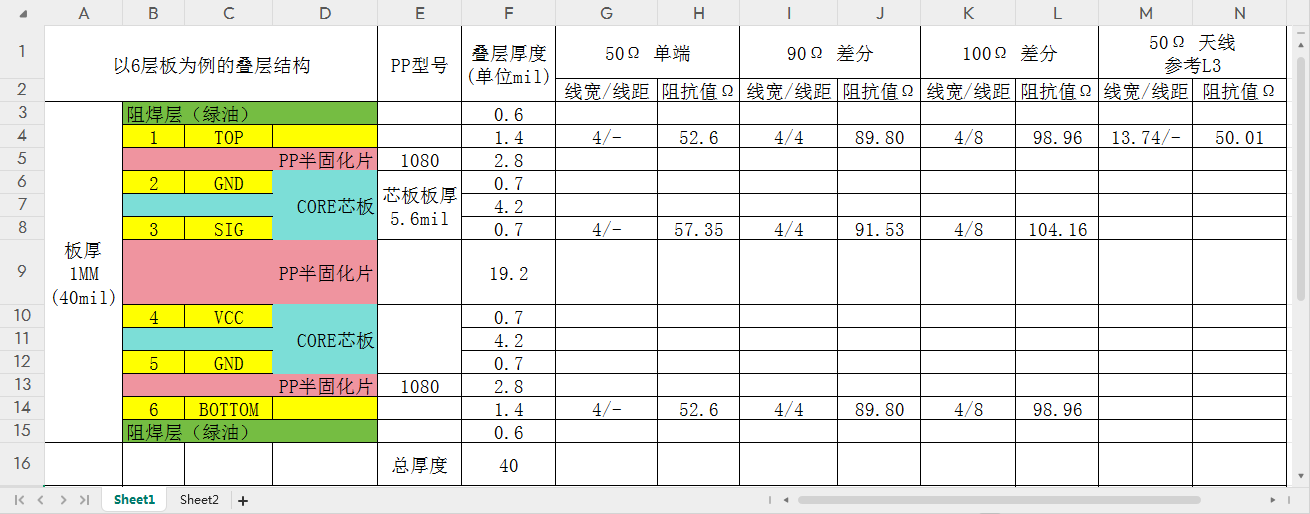

8. 以6层板为例的叠层结构

(1) 单端50Ω TOP/BOTTOM

(2) 单端50Ω SIG

- 注意:该模型中的“H1为芯板CORE,H2为半固化片PP”。

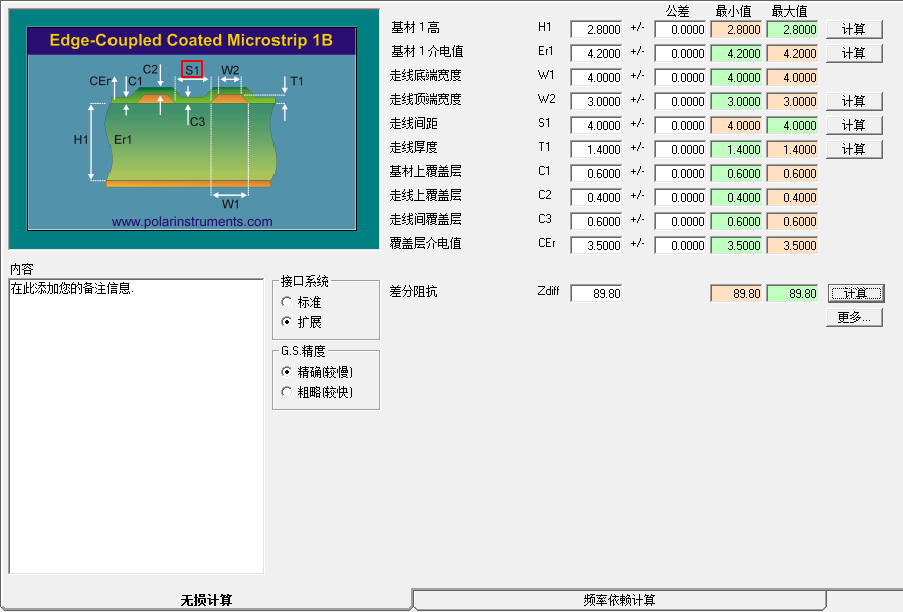

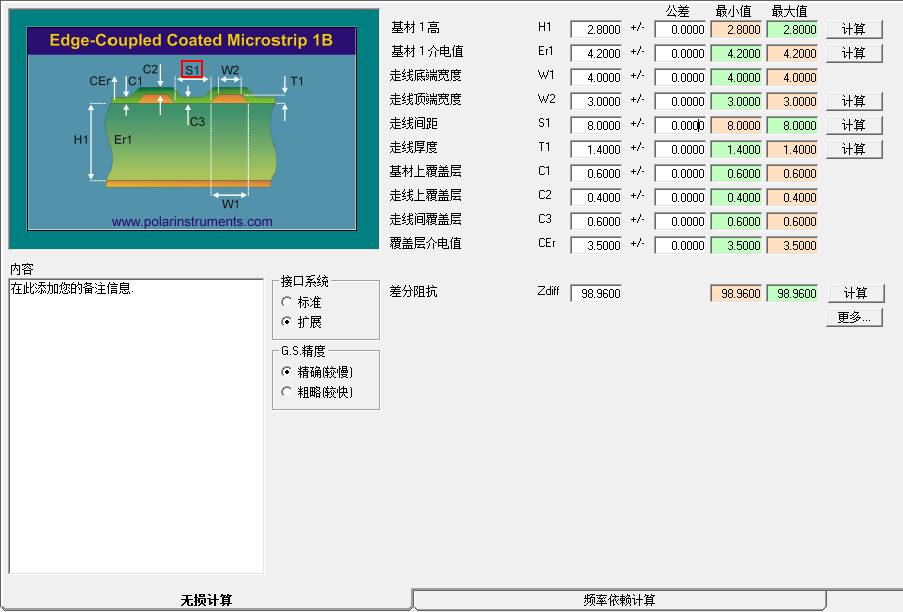

(3) 差分90Ω TOP/BOTTOM

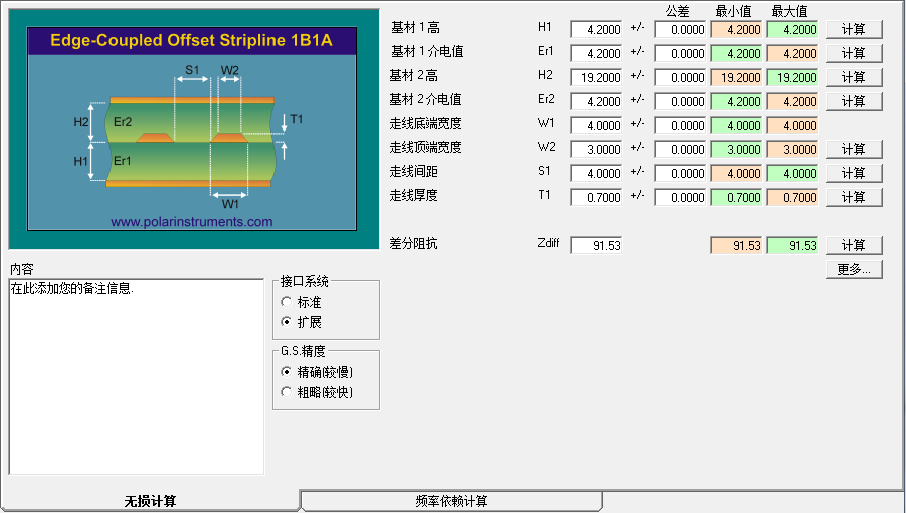

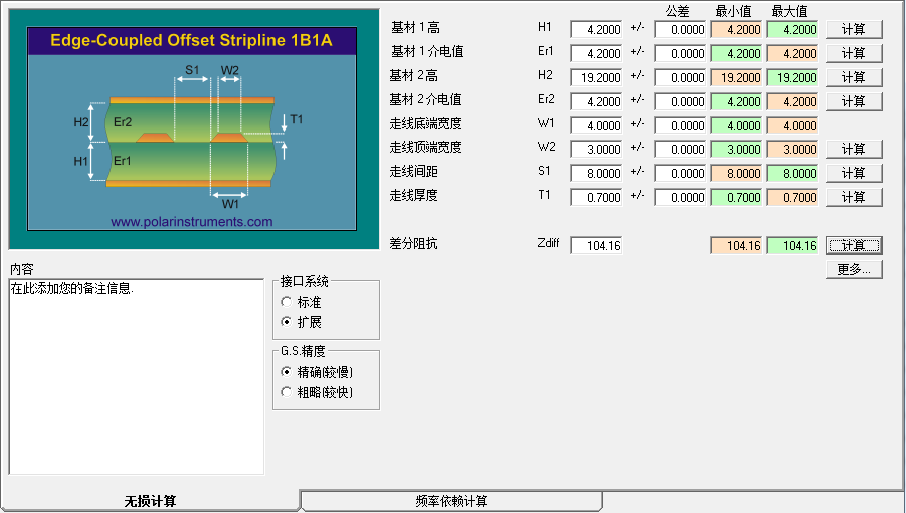

(4) 差分90Ω SIG

(5) 差分100Ω TOP/BOTTOM

(6) 差分100Ω SIG

(7) 天线50Ω 参考L3

总结

阻抗计算是高速PCB设计的核心,确保信号高效传输、减少噪声和兼容性问题的关键步骤。通过精确控制几何参数和材料特性,实现阻抗匹配,从而提升系统可靠性。

浙公网安备 33010602011771号

浙公网安备 33010602011771号