学习日记 - 9.11

PN结,MOS,体效应

PN结(拼凑网上大佬的笔记)

掺入Ⅲ族元素的硅是P(positive,正)型半导体,主要以空穴导电;掺入Ⅴ族元素的硅是N(negative,负)型半导体,主要以电子导电。

台湾清华的课件chapter 2 里有介绍,这课件做得确实好。

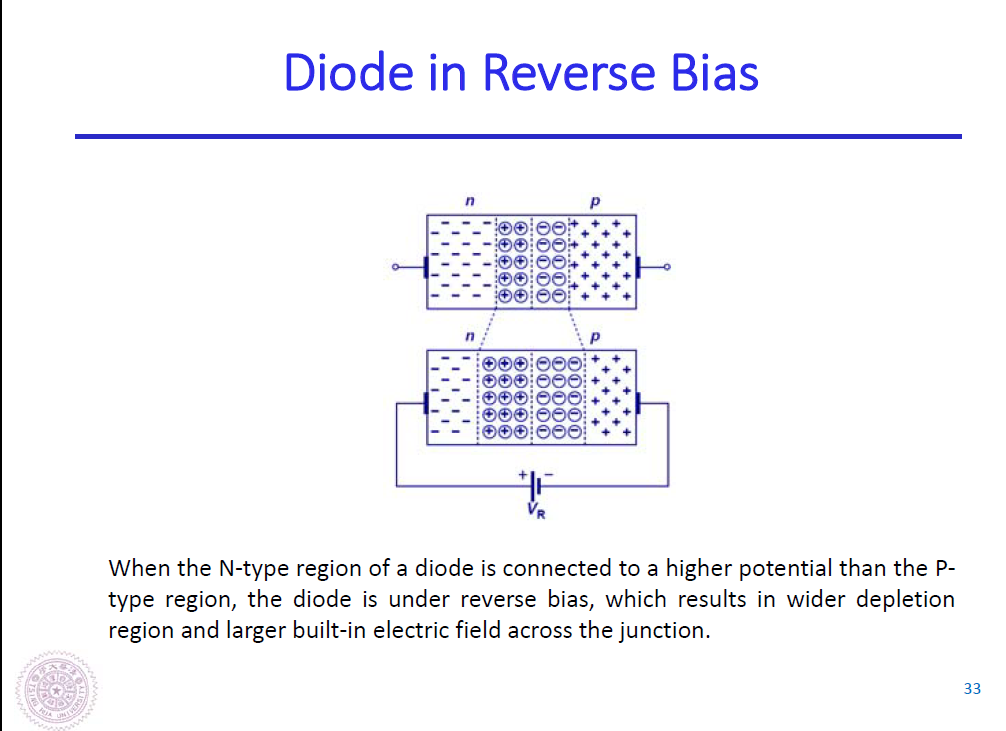

PN junction: 1) in equilibrium 2) under reverse bias 3) under forward bias;

MOS

nmos 制作在 p- substrate 上,两个重掺杂 n 区形成源端和漏端,重掺杂的导电多晶硅( poly silicon)为栅,下面有一层 SiO2 ,称为栅氧,作用是让栅和衬底隔离,沟道里的电子不会与栅极接触。

(pmos 制作在 n-substrate 上)

PMOS要做在局部衬底上,称为阱(well)。

n well 必须接一定电压,使得源/漏结二极管反偏(the S/D junction diodes),这个PN结也就是源与衬底,漏与衬底的PN结。

这些 PN结 需要反向偏置,以防止二极管导通,保证MOSFET正常工作。

一般n well 与最正的电源相连,这样妥妥地反偏 S/D junction。

体效应

正常来说,PMOS里和NMOS里,衬底都经常和源接在一起:① PMOS里衬底要维持高电压,因为是 n-substrate,接正可以维持S/D junction反向偏置。 ② NMOS里衬底要接低电压,因为是p - substrate,低过源和漏的电势就可以维持S/Djunction反向偏置;

在NMOS中,如果衬底电压低于源电压,即 Vsb>0,会发生什么?

源结和漏结维持反向偏置,Vb变得更负时,更多空穴被吸引到衬底电极,而留下大量负电荷。而阈值电压是耗尽层电荷总数的函数。

因此inversion layer形成之前,栅极电荷镜像Qd。Vb下降,Qd增加,Vth也增加。

考虑体效应以后的Vth计算公式为:

对NMOS,如果Vsb<0,那么Vth会减小吗?

- 是的。衬底电压高于源端,则 Vth < Vth0。人们可以偏置衬底来降低Vth。

但对NMOS来说不容易,因为NMOS都共享衬底,而PMOS制作在N-well 里,比较容易做到。

浙公网安备 33010602011771号

浙公网安备 33010602011771号