基本逻辑门与其Verilog描述方法

基本逻辑门

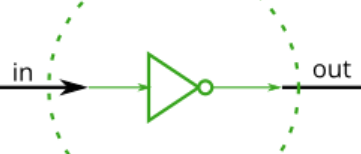

非门(NOT Gate)

- 描述方法:

module MyModule(input in, output out);

assign out = ~in;

//或者

assign out = !in;//逻辑非

endmodule

在其他逻辑门基础的末尾加圈可以达到取反效果(与或门):

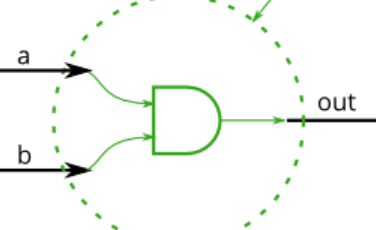

与门(AND Gate)

- 描述方法:

module MyModule(inout a, input b, output out);

assign out = a & b;

endmodule

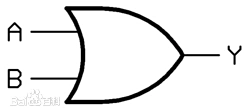

或门(OR Gate)

- 描述方法:

module MyModule(input a, input b, output y);

assign y = a | b;//按位取或

//或者

assign y = a || b;//逻辑或

endmodule

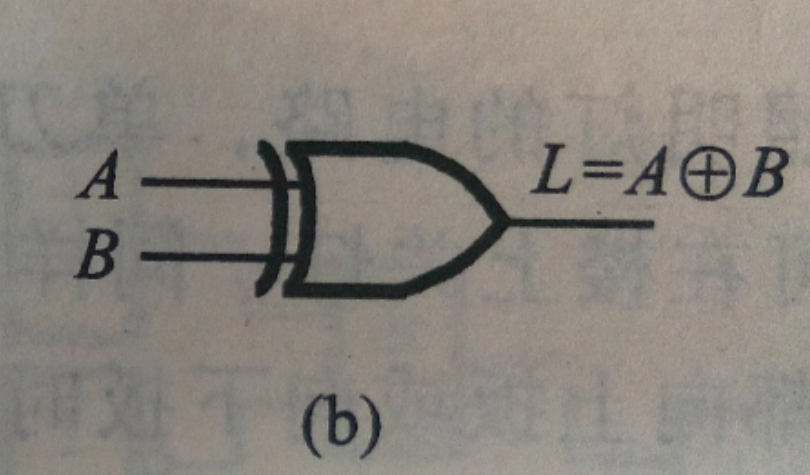

异或门(XOR Gate)

- 描述方法:

module MyModule(input A, input B, output L);

assign L = A ^ B;

endmodule

若

A与B的值相同,则返回TRUE(1),否则返回FALSE(0)

浙公网安备 33010602011771号

浙公网安备 33010602011771号