浅谈xilinx FPGA高速接口

1.1系列高速接口概述

1) XIlinx 7系列高速接口。

Xilinx最早在Virtex-II Pro系列上引入了高速接口。这个系列于2002年首次推出,并采用了Xilinx的RocketIO多协议高速串行收发器技术。

RocketIO:RocketIO是Xilinx FPGA中的收发器(SerDes)技术。它是Xilinx用于实现高速串行数据传输的特定硬件资源和IP核。RocketIO可以通过不同的协议和接口实现高速通信,如PCI Express(PCIe)、Serial RapidIO、XAUI等。RocketIO提供了灵活的配置选项和丰富的功能,包括数据编码、时钟管理、流控制等,以支持各种应用需求。

2) 高速接口的出现有什么意义。

高速接口的引入主要是为了满足不断增长的数据传输需求和应用的高性能要求。现在数据量数据越来越大,引入高速接口是必然的发展趋势。

从高速AD采集就可以看出,从一开始的并行接口,到LVDS接口再到JESD204接口,速率越来越高,采样率也是越来越高。

3) Xilinx高速接口支持的应用。

- PCIE

- JESD204B

- HDMI

- RapidIO

- SRIO

- aurora

.......等等

1.2系列高速接口解析

下面以7系列FPGA为例。

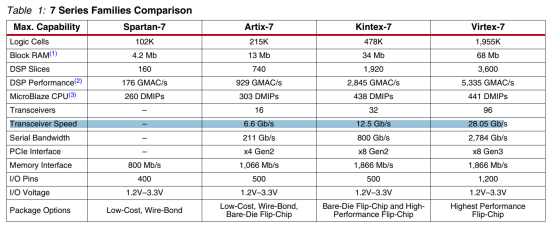

通过查阅XILINX官方数据手册DS180,我们可以知道以下几点信息:

1) Xilinx高速收发器分为GTP(最高支持6.6Gb/s),GTX(最高支持12.5Gb/s),GTH(最高支持13.1Gb/s),GTZ(28.05Gb/s)。如下图所示Artix7搭载的就是GTP最高支持6.6Gb/s,所以决定了Artix7实现不了万兆网。

2) GTP内部结构

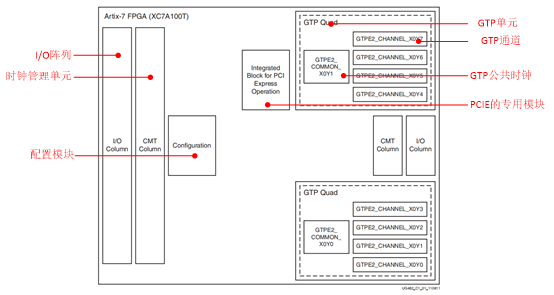

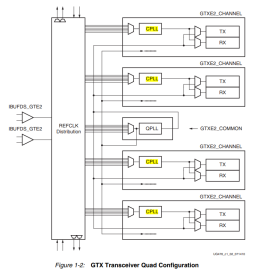

由于GTP,GTX,GTH内部结构基本一致,所以我们先对GTP进行讨论,以下先以XC7A75TA为例,Xilinx内部把高速接口单元用Quad来表示,如下框图所示,在XC7A100T中,分为以下几个硬件模块,IO阵列,CMT时钟管理单元,GTP Quad,PCIE专用模块。一个GTP Quad包含了4个GTP CHANNEL、一个GTP COMMON。

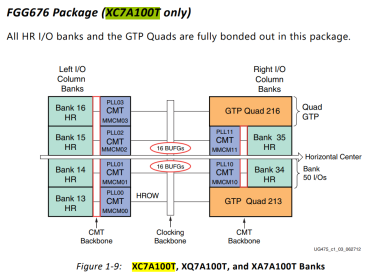

通过我们UG475看XC7A100T的bank分配可以知道,和我们上图是差不多的。

3) GTP QUAD内部结构

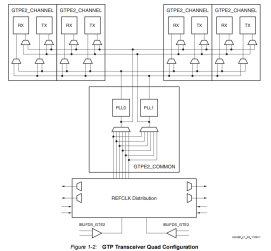

一个QUAD内部有一个GTPE2_COMMON,四个GTPE2_CHANNEL,一个时钟分配模块。一个GTPE2_COMMON里包含两个PLL。在GTX和GTH中还增加了QPLL和CPLL的区分。

4) GTP时钟分配和GTPE2_COMMON

一个Quad支持两个时钟输入,同时支持将输入的时钟输出给临近的QUAD。GTPE2_CONMMON内部集成了两路PLL用于给高速收发器提供时钟。

5) GTPE2_CHANNEL

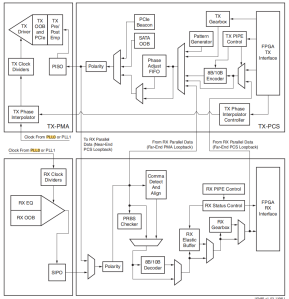

在GTP通道中,分为PMA和PCS两个部分,

PMA是GTP中的物理媒体适配器,负责与物理媒体进行通信和连接。物理媒体适配器主要包括物理层接口电路和信号调节电路,用于在GTP芯片和外部物理媒体(例如光纤、电缆等)之间传输数据。

PCS是GTP中的物理编码子层,是物理层协议的一部分。它负责将高层数据与物理信号之间进行转换和编码。物理编码子层会将输入的数据进行编码,以满足物理媒体的要求,并将编码后的数据传输到物理媒体适配器(PMA)进行发送。

PMA和PCS是GTP在物理层上的两个重要组件,它们协同工作,使GTP能够与外部物理媒体进行数据传输和通信。GTP内部集成了8B/10B,串并转换等硬件资源,我们可以正确的使用这些资源来实现我们需求,其内部主要结构如下图所示:

谢谢!

浙公网安备 33010602011771号

浙公网安备 33010602011771号