DFTC

DFTC

第一章

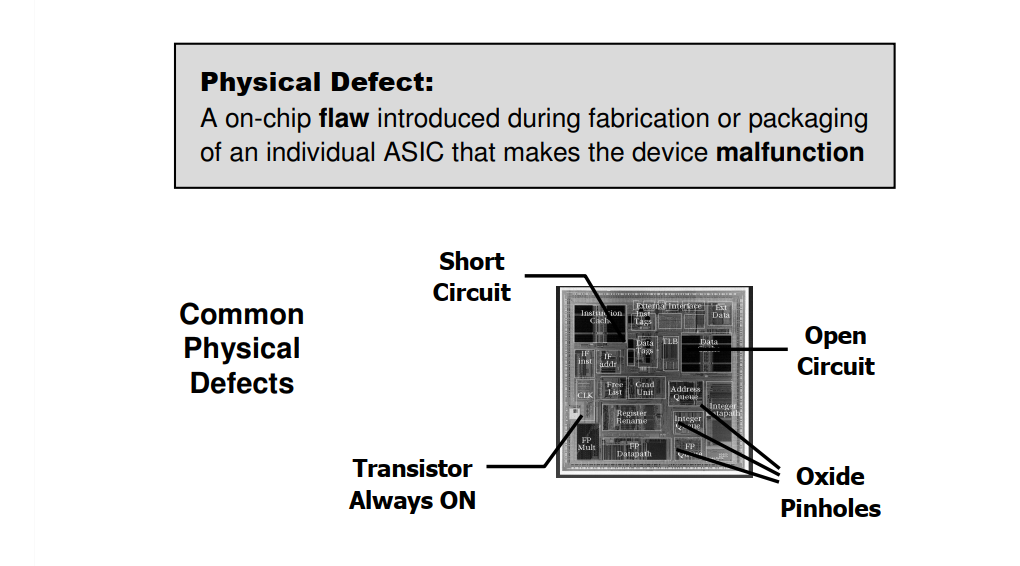

1.1 物理缺陷

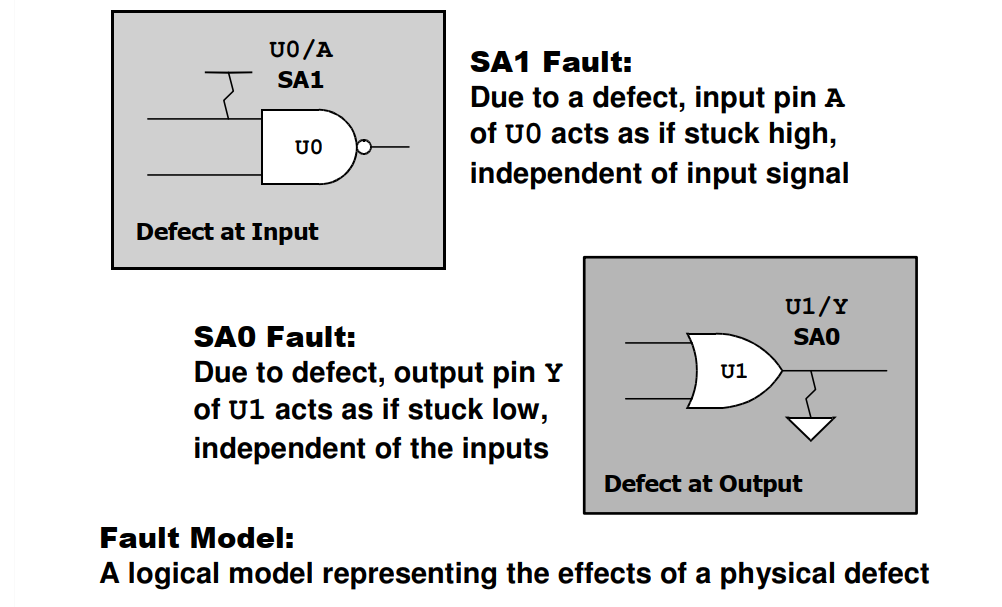

1.2 stuck-at缺陷

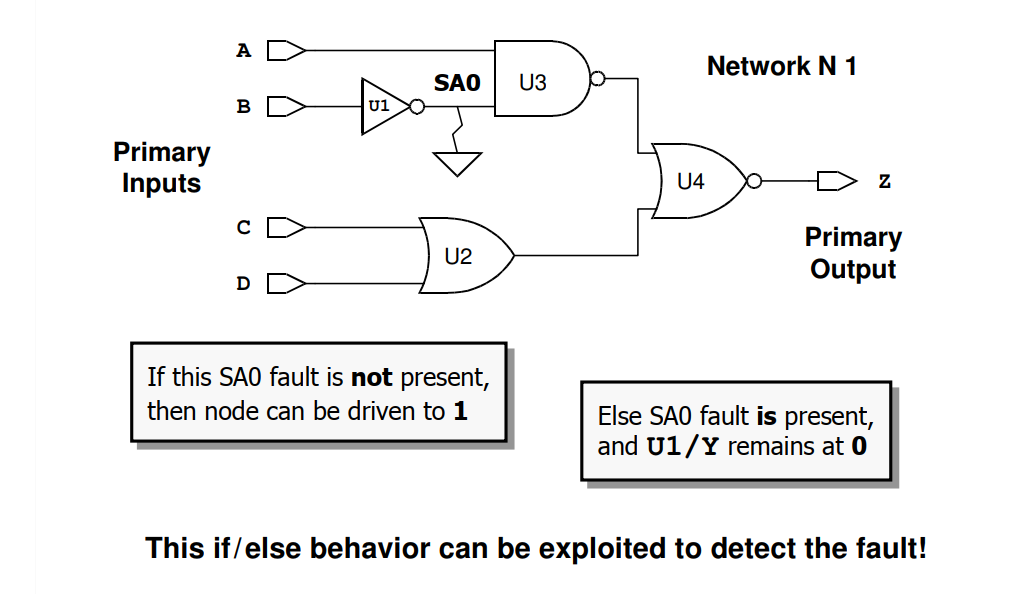

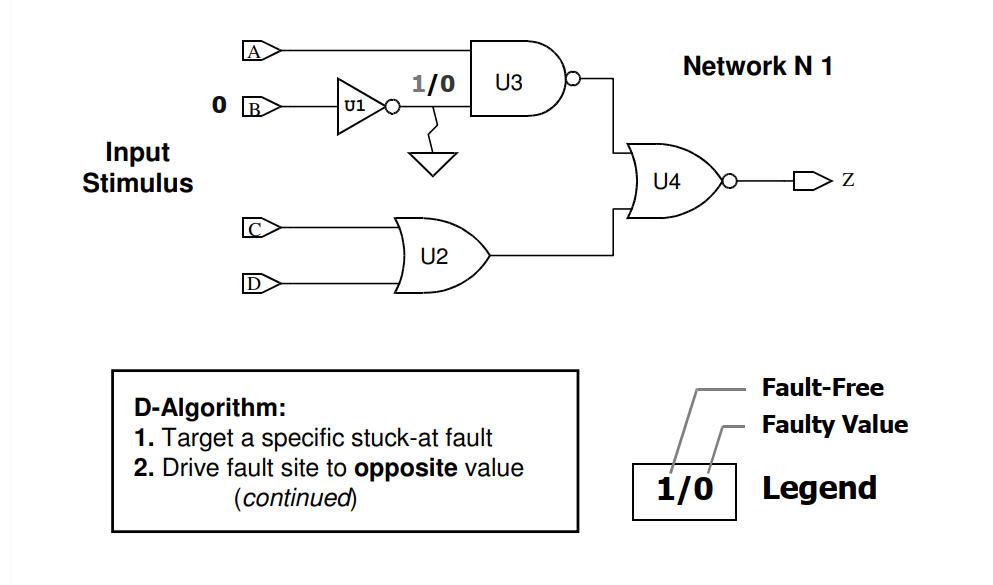

1.3 组合逻辑SA检测

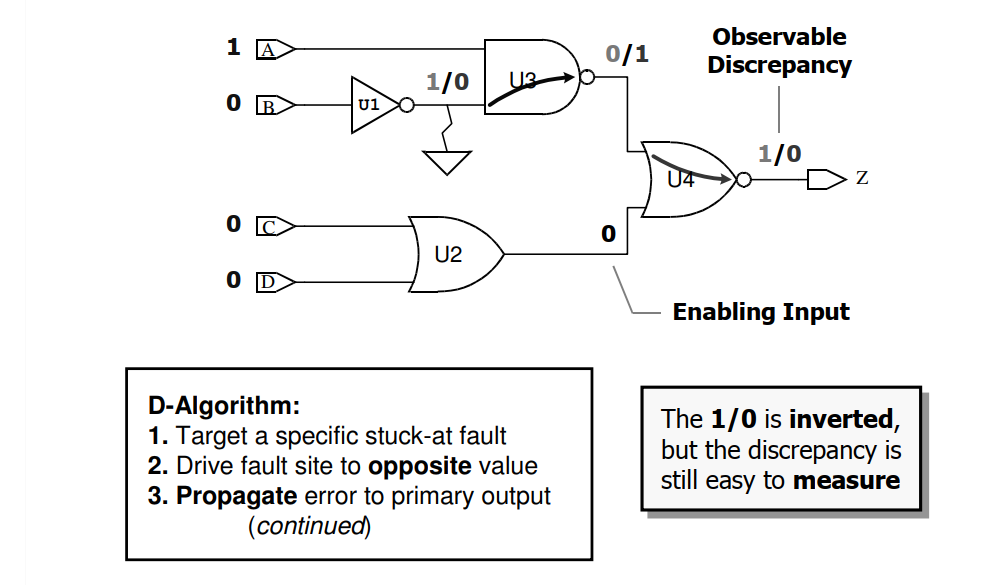

组合逻辑测试方法:

- 假设目标测试点出现某种缺陷

- 输入信号使得目标测试点值与假设值相反(activate the target fault by driving the node to the opposite value. )

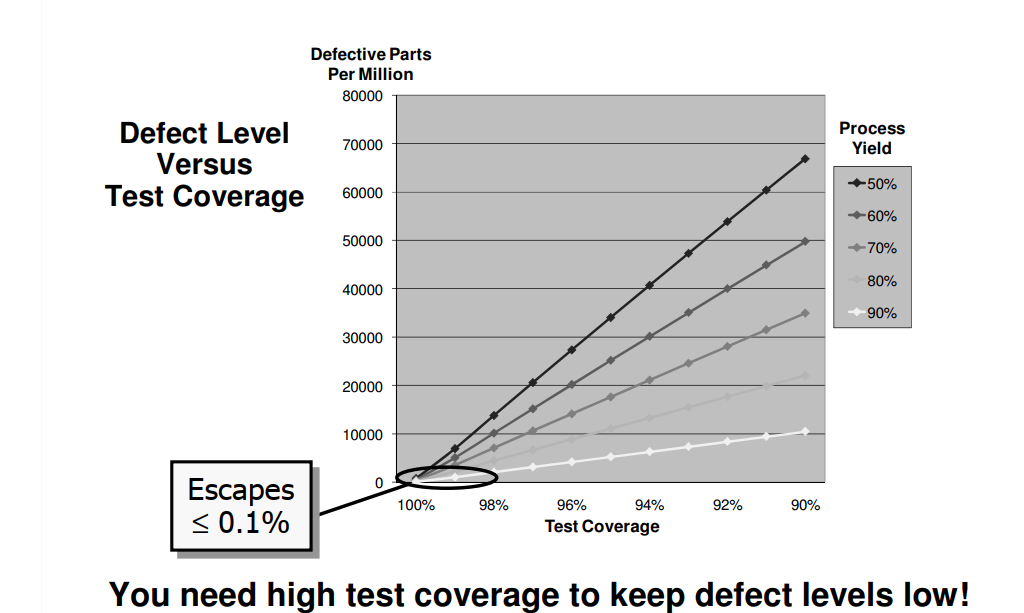

1.4 为什么需要高覆盖率

在无法保证良率的情况下,覆盖率的提升有利于提升测试的质量。通过测试的一些芯片中任然有可能有一些存在缺陷的芯片没有被检测出来,提升coverage可以有效地减少这种情况发生,以防次品流入市场。

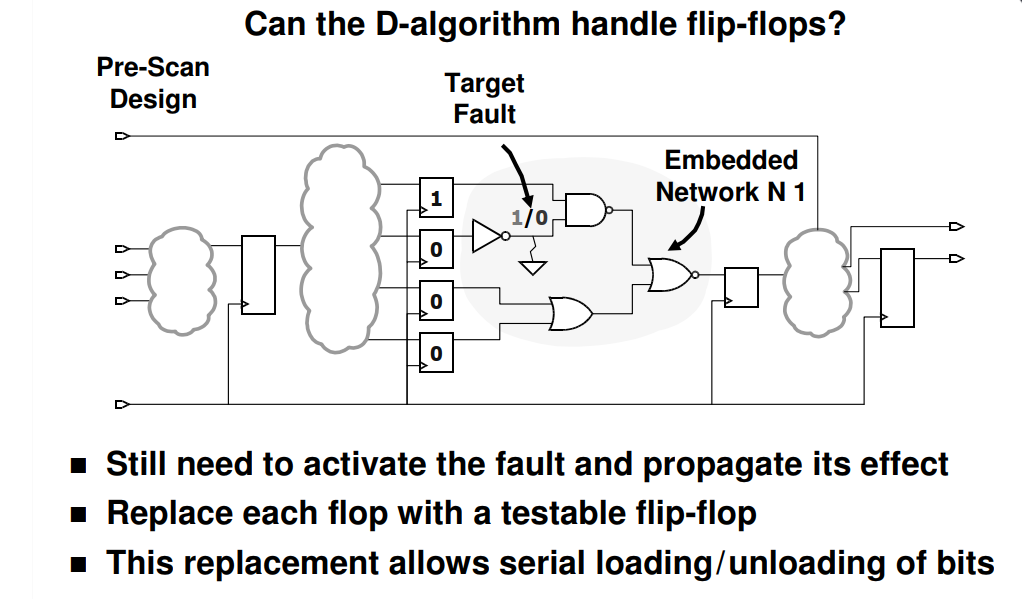

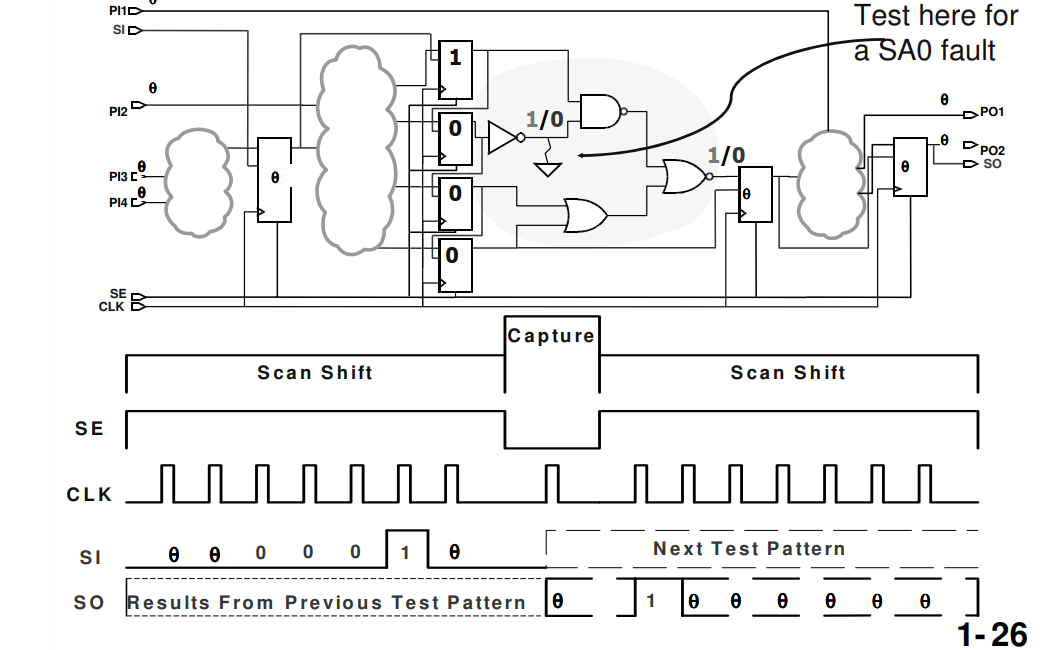

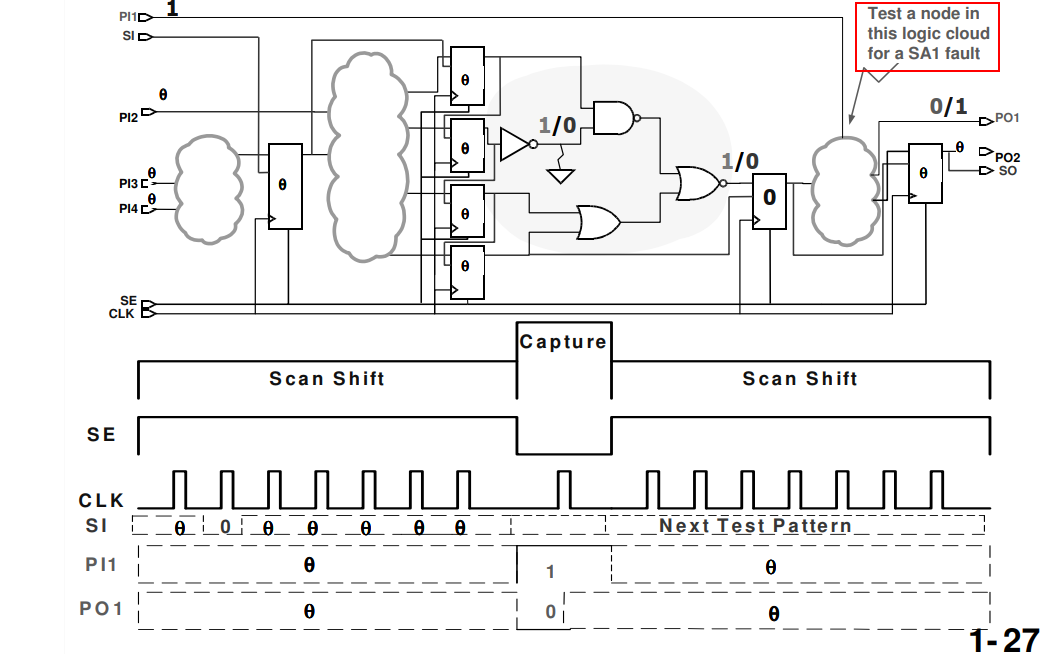

1.5 时序逻辑故障检测

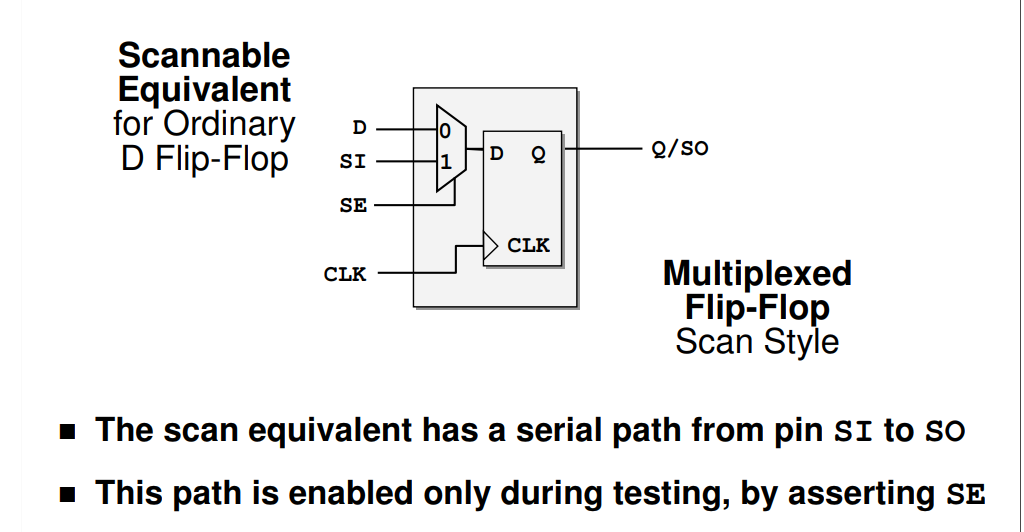

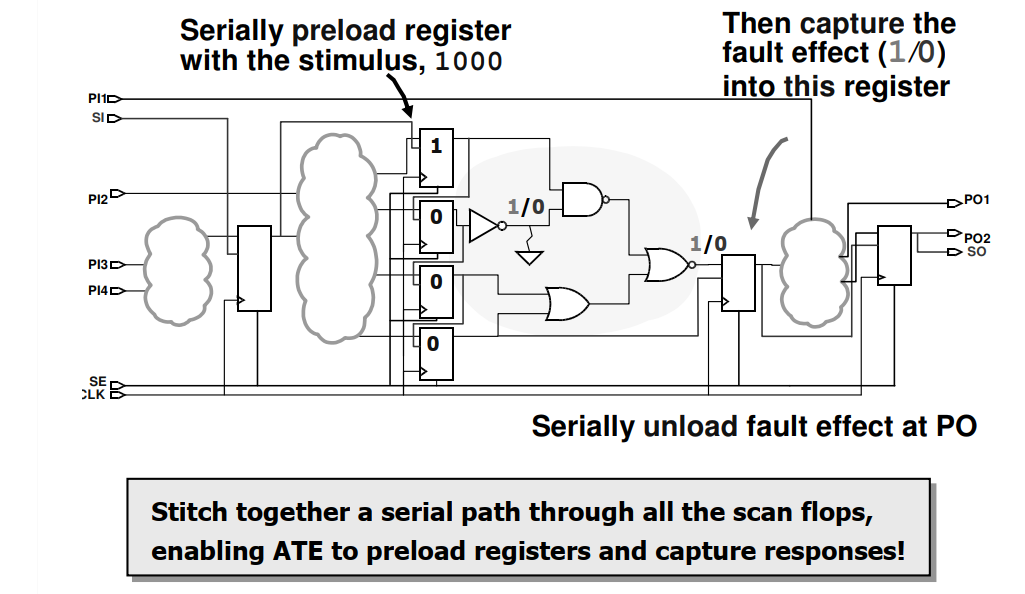

时序逻辑SA defect检测需要把普通的D触发器替换为MUX DFF

测试逻辑块中的故障

浙公网安备 33010602011771号

浙公网安备 33010602011771号