What is Fermi?(3)

GF100新单元,GPC架构

GPC架构解析

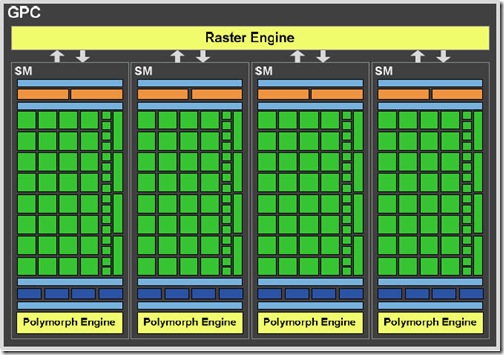

前面我们介绍了,GF100核心当中总共由四组GPC(Graphics Processing Clusters,图形处理集群)组成。那么,接下来我们就来仔细了解一下这个全新的GPC单元当中的内部架构是如何设计的。

在每个GPC当中,都会包括一个Raster Engine(光栅引擎,顶部黄色横条)以及最多四组SM(Streaming Multiprocessors,后文统一采用SM阵列简称,不再复述)阵列。注意,我们这里说到的是每个GPC内最多有四组SM阵列,NVIDIA会根据情况对GPC内的SM单元进行削减。例如在GTX480核心当中,就削减掉了一个GPC当中的一组SM阵列,也就是说其中三组GPC均有四个SM阵列,而另外一组GPC当中仅有三组SM阵列。

GPC是GF100当中的一个重要模块,也是NVIDIA在统一架构产品当中首次引入的概念。在每个GPC当中,都增加了一个Raster Engine(光栅引擎)。除此以外,每个GPC几乎都可以被看成是一个完整的GPU小核心,因为每个GPC当中均包括了能够对定点、几何、光栅、纹理以及像素处理的功能。可以说,除了ROP功能外,GPC几乎已经能够完成绝大部分的图形处理工作。如果NVIDIA对整体GPC进行削减,那么也将会是一件非常容易的事情。我们猜测这对产品线架构的划分,会非常有利。

GPC设计的优势

几乎等同于单个GPU的GPC部分,在每个GF100核心当中均拥有四组。如此一来,NVIDIA想要在中端、主流级以及入门级显卡当中重新调整核心架构就显得相当容易了。 因为NVIDIA仅需要对GPC数量进行调整,几乎就可以完成对不同等级显卡的划分。而在具体到每个系列产品的结构划分当中,NVIDIA又可以根据产品的良品率适时的削减SM阵列。这样一来,NVIDIA不仅能够将产品线划分得更细,同时对于晶圆的良品率也起到了间接的提升作用,可谓一举两得。

或许有读者会说,NVIDIA原有的SM阵列屏蔽方式不也一样能够起到等级划分的作用么?没错,如果NVIDIA的设计思路依然停留在GT200的时代,那么原有的等级划分方式确实有效,不过在引入了全新的Raster引擎以及Polymorph引擎之后,单纯屏蔽SM阵列的方法显然就不再那么合适了。

浙公网安备 33010602011771号

浙公网安备 33010602011771号