【RAM for Logisim】MIPS字节/高低字/双字访问RAM动态存储器设计(根据中国大学MOOC自己动手画cpu设计)

前言

1.logisim一般情况下突破了一些关于电子器件的实现细节,是一个不错的理论型自学平台。

2.在计算机工作原理中有些指令不可能只写在一个存储单元中,而且过高的存储单元位数可能造成内存空间的浪费,从而达不到较好的内存管理效果。

3.本章希望通过扩展8位内存单元的随机存储器,达到理解汇编语言中字节/字/双字的访问原理。

正文

要求:

1.(1)字节访问8位,字访问(高字/低字)16位,双字32位

(2)要求高16位从读出端口的低字部分读出(难点)

2.第一个要求数据的写入和存储

3.测试

实施

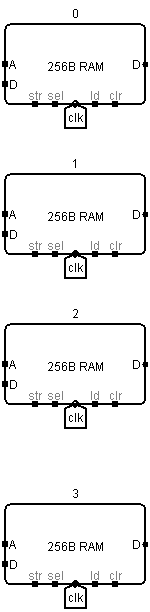

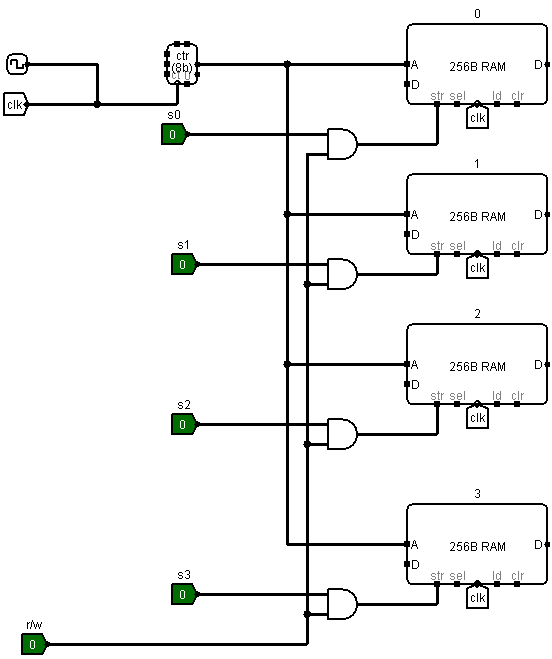

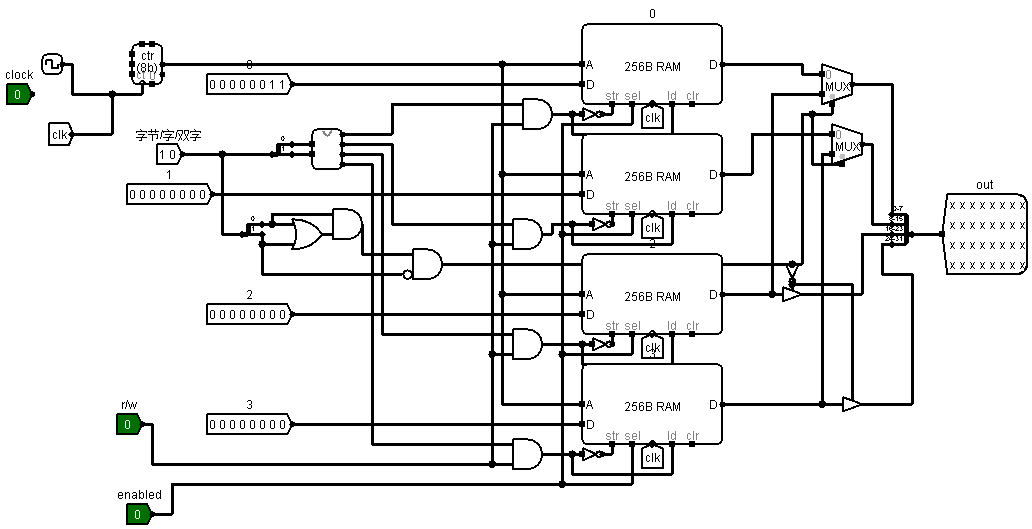

根据要求1知到需要4个存储位数相同的随机存储器填写标号

2.采用同一计数指针链接四个ram片的地址选择端

3.增加读写控制端和字节/字/双字选通信号端口

s0-s3未免太繁琐

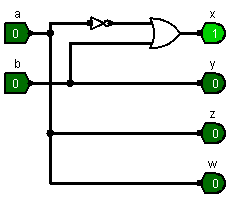

所以需要设计一个组合逻辑电路译码器选择s0-s3片选

| 输入 | s0 | s1 | s2 | s3 |

| 00(字节) | 1 | 0 | 0 | 0 |

| 01(高字) | 0 | 0 | 1 | 1 |

| 10(低字) | 1 | 1 | 0 | 0 |

| 11(双字) | 1 | 1 | 1 | 1 |

这样的存储器能工作,但高字访问的时候会从高位输出怎么办呢?

答案是根据01信号是高字访问这一特性,在组合逻辑基础上逐步加权.

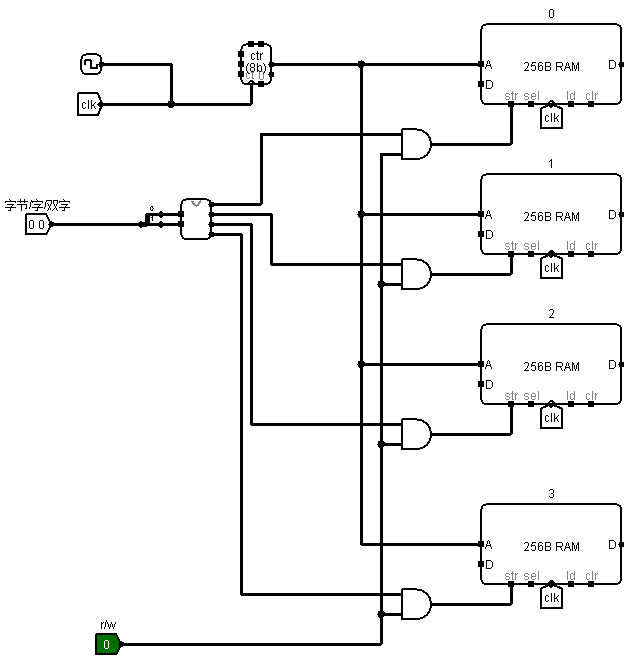

具体过程讲解有点复杂,直接上图

有些线路被存储器身体压住了,但不影响整体,要注意在输出口的一些三态门和二路选择器的关系。

浙公网安备 33010602011771号

浙公网安备 33010602011771号