Static Timing Analysis(静态时序分析)

- 前言:

时序分析在FPGA规范的设计中是必要的,在FPGA高速系统的设计中更是必不可少的,否则就会出现在RTL逻辑仿真完全正确,但是上板验证时时序不满足要求导致整个系统不能正常工作,所以在IC/FPGA设计中时序分析是非常重要的。

时序分析方法有两种:

- 静态时序分析:通过设计好电路中的已知参数利用EDA工具提供的模型分析出时钟和数据的关系,它是一个便捷高效的时序分析方法。

- 动态时序分析:把设计好的电路中的所有延时都考虑进来,在EDA仿真工具中把延时参数都加上,然后观察仿真的波形并测量Ts(T-setup,建立时间:数据起始位置到达采样时钟的上升沿的时间)、Th(T-hold,保持时间:采样时钟的上升沿到达数据结束位置的时间)是否满足时序要求,需要电路模拟跑起来才能测出来。

- 模型分析

首先是给出一些名词的解释

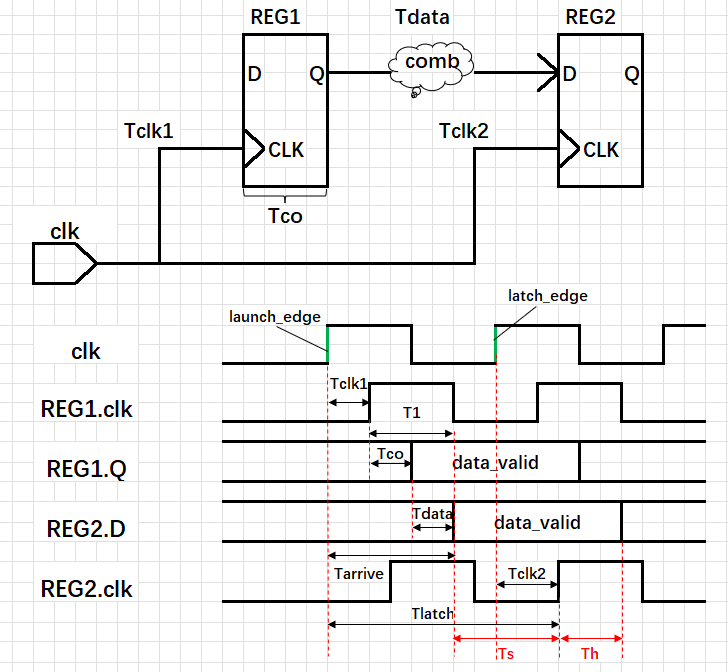

- launch edge:即发射数据的沿,是管脚传进来同步于数据的有效时钟clk的上升沿,也被认为是0时刻

- latch edge:即锁存数据的沿,是目的寄存器REG2锁存数据的沿,相对于发射沿延后1个clk时钟周期后的起始位置(不考虑时钟抖动jiter)

- Tclk1:时钟源clk扇出信号到寄存器1(REG1)的时钟端所需要的时间

- Tclk2:时钟源clk扇出信号到寄存器2(REG2)的时钟端所需要的时间(所以时钟源的布线很重要,这就是为什么FPGA推荐使用PLL输出时钟而不是自己进行时钟分频)

- Tco:寄存器时钟输出延时,有效时钟输入CLK到寄存器输出Q之间的延时

- Tdata:2个寄存器之间组合路径延时和布局布线延时,即如图所示REG1的输出Q到REG2的输入D之间的延时

- Tc:clk的时钟周期

- Ts:建立时间

- Th:保持时间

- Tsetup_slack:建立时间余量,要大于0

- Thold_slack:保持时间余量,要大于0

计算Ts也就是计算在REG2采样沿(即上升沿)到达之前数据需要提前建立的时间,我们引入几个中间量:

- REG1输入数据到REG2输入路径之间的延时T1 = Tco + Tdata

- REG2采样沿到达时间Tlatch = Tc + Tclk2

- REG2数据第一次到达时间Tarrive = Tclk1 + Tco + Tdata = Tclk1 + T1

根据图引入的中间量和图示,可以得出建立时间大小Ts = Tlatch - Tarrive = Tc + Tclk2 - Tclk1 - Tco - Tdata = Tc + Tclk2 - Tclk1 -T1

- Tclk2一般大于Tclk1,它们之间的差值可以记作Tdelta,为原时钟到达两个寄存器时钟之间的时钟偏移Tskew,所以可以将建立时间进一步改写为:Ts = Tc - T1 +Tdelta

- 从公式中不难看出,Tc越大Ts越大,对于设计越有利;关键路径延时T1越大,Ts越小,对于设计越不利。所以可以说建立时间Ts决定了最大时钟频率,关键组逻辑径延时T1决定了建立时间是否违例

计算Th也就是计算在REG2采样沿(即上升沿)到达之后到下一次数据到来之前,本次数据采样需要保持的时间

- 第二次数据到来的时间Tdata2 = Tclk1 + Tco + Tdata + Tc(Tdata_valid)

- 保持时间Th = Tdata2 - Tlatch = Tclk1 + Tco +Tdata - Tclk2 =T1 - Tdelta

- 从公式可见,保持时间和时钟频率无关,关键路径T1越长反而越有利,Tdelta越小越好

- 可以发现Ts + Th = Tc - T1 +Tdelta + T1 - Tdelta = Tc,即建立时间和保持时间之和为单个时钟周期的时间。

时间余量的建立即把时序要求的数值与上述计算结果做差就可知道,即我们在设计时将Ts 和Th设计的比计算出来的值偏大:

- Tsetup_slack = Tsreal - Ts >=0

- Thold_slack = Threal - Th >=0

以上的所有关于时序分析的计算在时序分析工具中都会给我们自动算好,其中还会加入时钟的不确定度和时钟的悲观度等参数信息。我们根据公式中参数和计算的结果就可以确定通过什么方式来优化才能使我们的时序达到最优 。

浙公网安备 33010602011771号

浙公网安备 33010602011771号