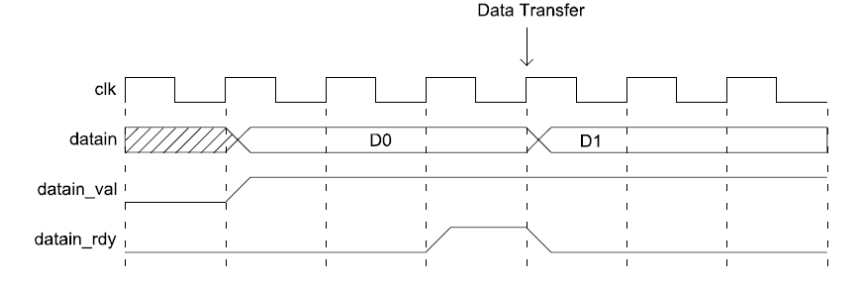

Verilog设计Valid-Ready握手协议

Handshake Protocol握手协议: 为了保证数据传输过程中准确无误,我们需要加上握手信号来控制信号的传输。握手协议的原则是:当Valid和Ready信号同时高有效时,数据在时钟上升沿传输。

本篇文章使用Verilog设计一个简单的Valid-Ready握手协议电路。

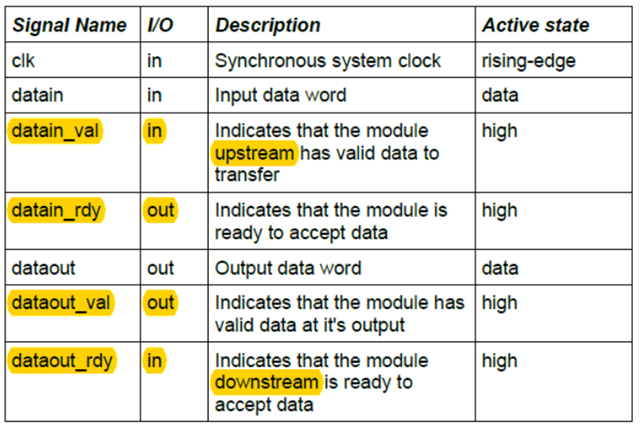

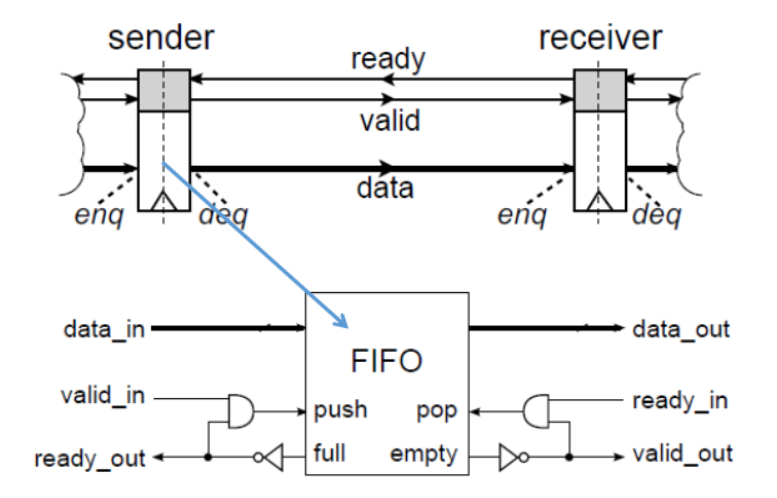

本设计可以实现数据的流入和数据的流出,这样一个双端口握手协议通道传输。Valid和Ready信号的原理类似于FIFO的读写和空满信号,就好像FIFO外边包了一层。

在FIFO的端口信号上加上如上图所示反相器,也可达到握手的效果。

Valid-Ready信号产生有两种情况。

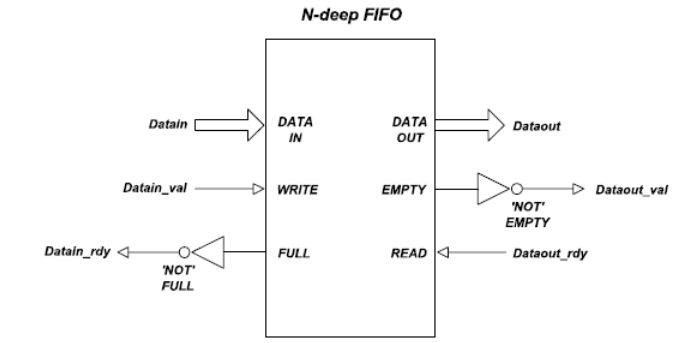

Ready-Before-Valid

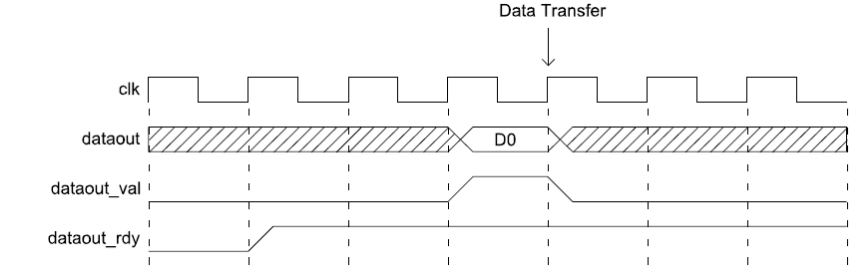

Ready-Before-Valid是Ready信号在Valid信号之前有效。如下时序图。

这样设计使得在数据来临之前,通道已准备好接收数据,可以保持通道的最大吞吐量,因为Ready先产生,这个通道保持刷新等待数据。通道作为接受数据端采用这样的设计。

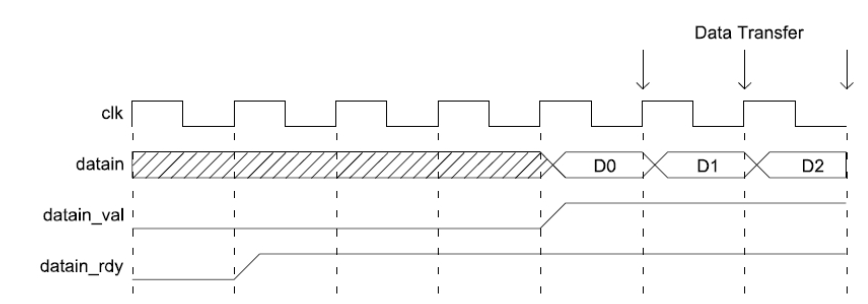

Valid-before-Ready

Valid-before-Ready是Valid信号在Ready信号之前有效。通道作为数据输出端采用这样的设计。收到下游接收端的准备接收信号,才开始传输数据。

Valid-Ready协议Stalemate情况

Stalemate可以理解为“锁住”。假设我们不遵守上面两种接收端和输出端的设计规则。

输出端用Ready-Before-Valid而接受端使用Valid-before-Ready,就会出现输出端等待接受端给出的Ready来输出数据,但是接收端也在等待输出端给出Valid信号来接受数据。两者都在等待却没有一方先给,所以这个时候这个通道就是无效的,被“锁住”了。

管道停止传输的情况

管道传输空的情况

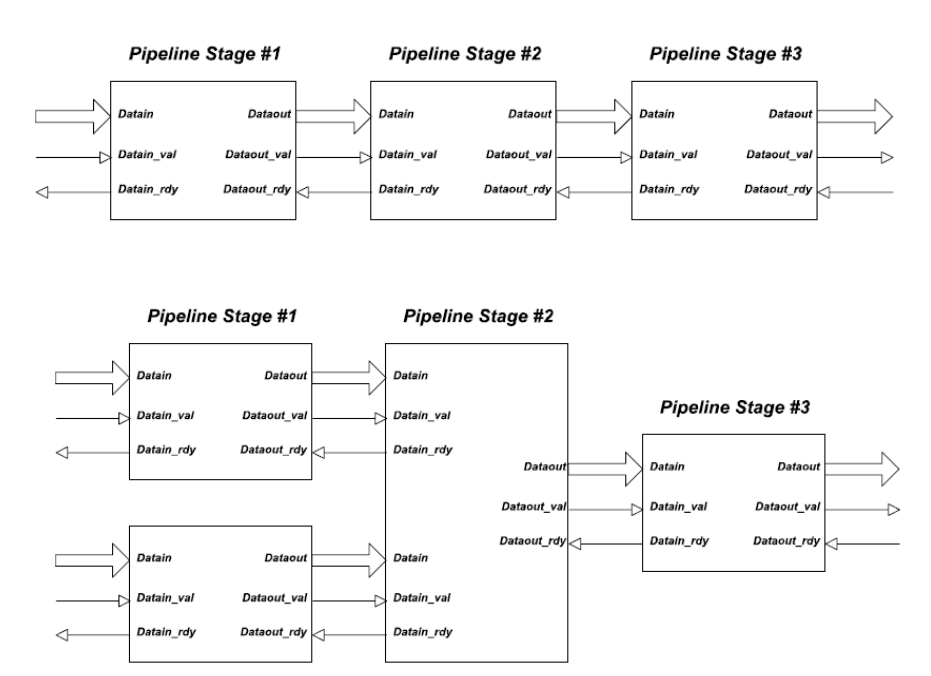

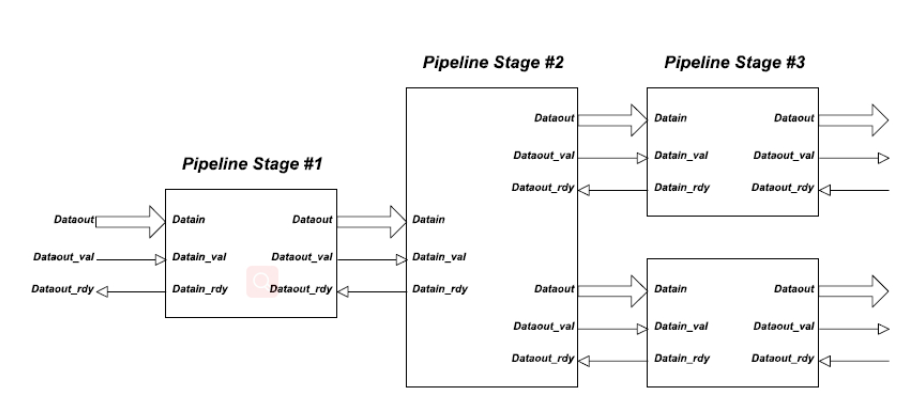

握手协议的几种连接情况

灵活连接

Verilog设计

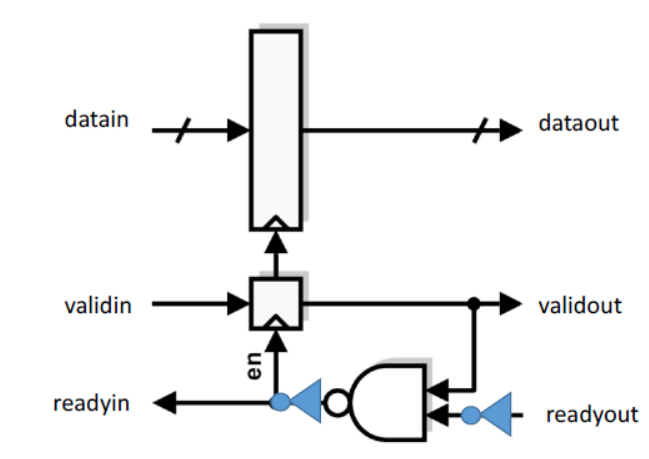

前面说过握手协议的接口可以在同步FIFO的基础上加以修改,修改电路如图

assign valid_o = ~fifo_empty; assign ready_i = ~fifo_full; assign wr_en = ready_o & valid_i; assign rd_en = ready_i & valid_o

这是加了缓存后的设计,也可以直接传输不加缓存直出。电路如下图。

verilog实现代码:

module Handshake_Protocol( input clk, input rst_n, input valid_i, //from pre-stage input data_i, //from pre-stage input ready_i, //from post-stage output ready_o,//to pre-stage output valid_o, //to post-stage output data_o //to post-stage ); reg valid_o_r; reg data_o_r; always @(posedge clk) if(~rst_n) valid_o_r <= 1'b0; else if(valid_i) valid_o_r <= 1'b1; else if(~valid_i) valid_o_r <= 1'b0; always @(posedge clk) if(~rst_n) data_o_r <= 1'b0; else if(valid_i) data_o_r <= data_i; assign ready_o = ready_i; assign valid_o = valid_o_r; assign data_o = data_o_r; endmodule

Reference

Using the Valid-Ready pipeline protocol ——ZIPcores.com

Data Transfers Synchronous handshake ——Giorgos Dimitrakopoulos

https://stackoverflow.com/questions/53583946/valid-ready-handshake-in-verilog

https://filebox.ece.vt.edu/~athanas/4514/ledadoc/html/pol_cdc.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号