E203总线接口单元

一、片上总线协议概述

1、AXI

2、AHB

3、APB

二、自定义总线协议

1、ICB简介

该总线协议和AHB和AXI协议比较类似,最主要的特性如下(括号内注明和哪个协议类似):

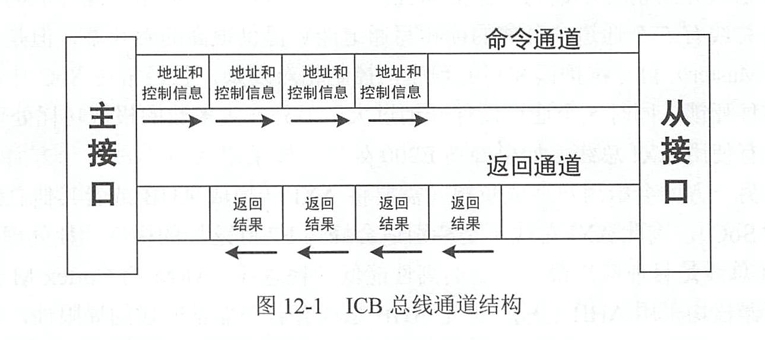

- 具有两个独立的通道,读写操作共用地址通道,返回结果共用返回通道

- 地址和数据传输阶段分离(AXI)

- 地址区间寻址,支持任意主从数目和拓扑结构,支持多个滞外传输(AXI)

- 使用字节掩码控制写操作(AXI)

- 支持非对齐地址的数据访问(AXI)

- 每个读写操作都会在地址通道上产生地址(AHB)

- 不支持乱序返回乱序完成,必须顺序反馈结果(AHB)

- 实现简单,易于桥接到其他总线(其实没什么用,因为桥接花的时间大于学习并实现这个总线接口的时间)

- 易于添加流水线获得更高频率的时序(俗称体质好,能超频,但如果用蜂鸟E203在FPGA上实现的话并没有什么用)

ICB总线通道结构

2、ICB协议信号

3、ICB协议的时序

三、ICB的硬件实现

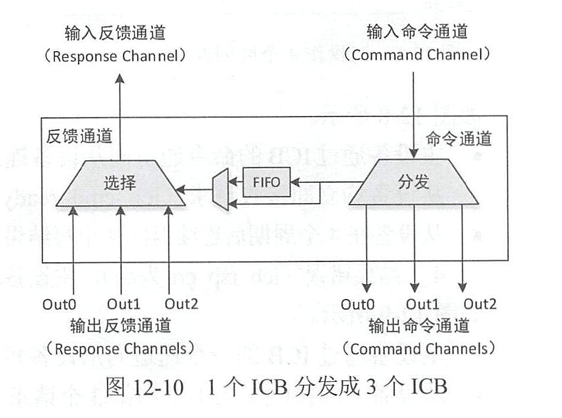

1、一主多从

该模块没有引入任何的周期延迟,即输入ICB和输出ICB在一个周期内接通

支持多个涉外交易,反馈通道返回的结果需要多个周期才能返回,并且返回的时间点可能不一致,需要仲裁。从FIFO缓存中按顺序弹出之前压入的分发信息作为仲裁标准;因此FIFO的深度决定了该模块能够支持的的涉外交易的个数。

若FIFO为空,表示没有涉外交易,则当前分发的ICB交易可由从设备在同一个周期内立即返回结果。

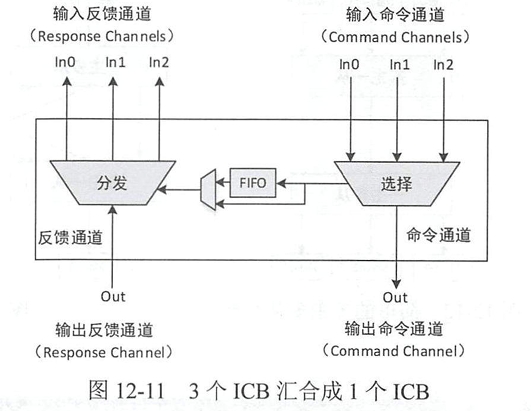

2、多主一从

和一主多从的规则基本相同

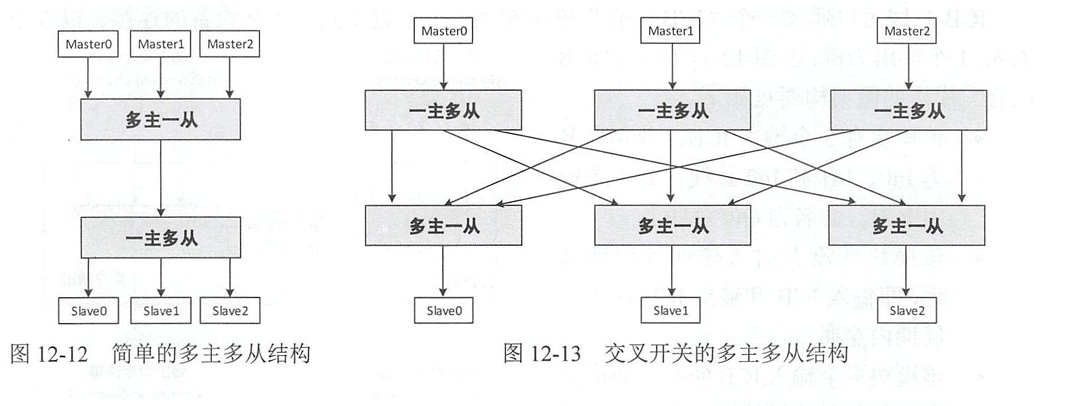

3、多主多从

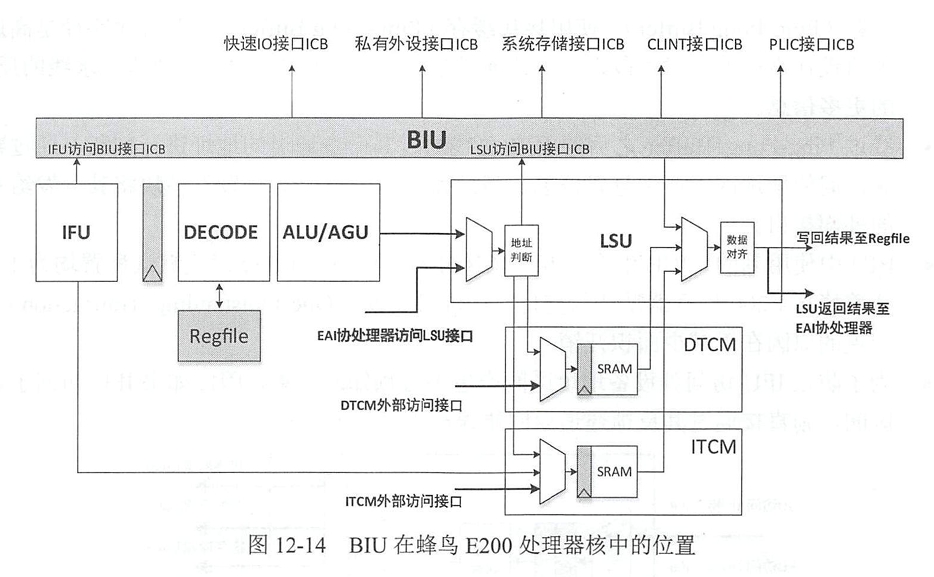

四、蜂鸟E203处理器核BIU

1、BIU在E203处理器核中的位置

系统存储总线用于访问SoC中的ROM、OTP、FLASH只读区间等外设存储器

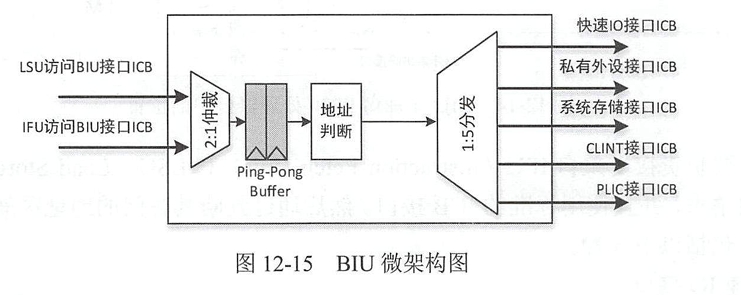

2、BIU的微架构

BIU有两组输入ICB接口,分别来自IFU和LSU,通过一个ICB汇合模块合成一组ICB总线,采用优先级仲裁,LSU具有更高的优先级

为了截断外界和处理器内核之间的时序路径,在汇合的ICB总线处额外插入了一组乒乓缓存

ICB汇合、分发两个模块的FIFO深度默认配置为1,它默认只支持一个滞外交易,用于减少面积开销

3、BIU的源代码

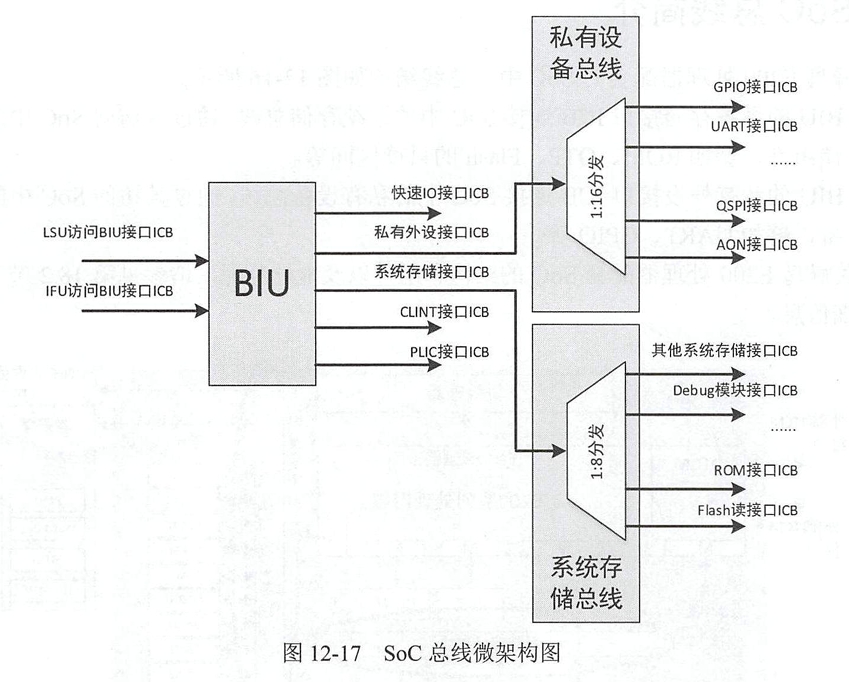

五、蜂鸟E203处理器SOC总线

1、SOC总线简介

系统存储总线用于访问SoC中的ROM、OTP、FLASH只读区间等外设存储器

2、SOC总线微架构

- 如果任何ICB路径中存在着时序的关键路径,可以插入一组乒乓缓冲区以切断前后的时序路径

- 需要跨越异步时钟域或者整数倍分频时钟域,也可以插入相应的异步FIFO缓存或者流水线级数。

浙公网安备 33010602011771号

浙公网安备 33010602011771号