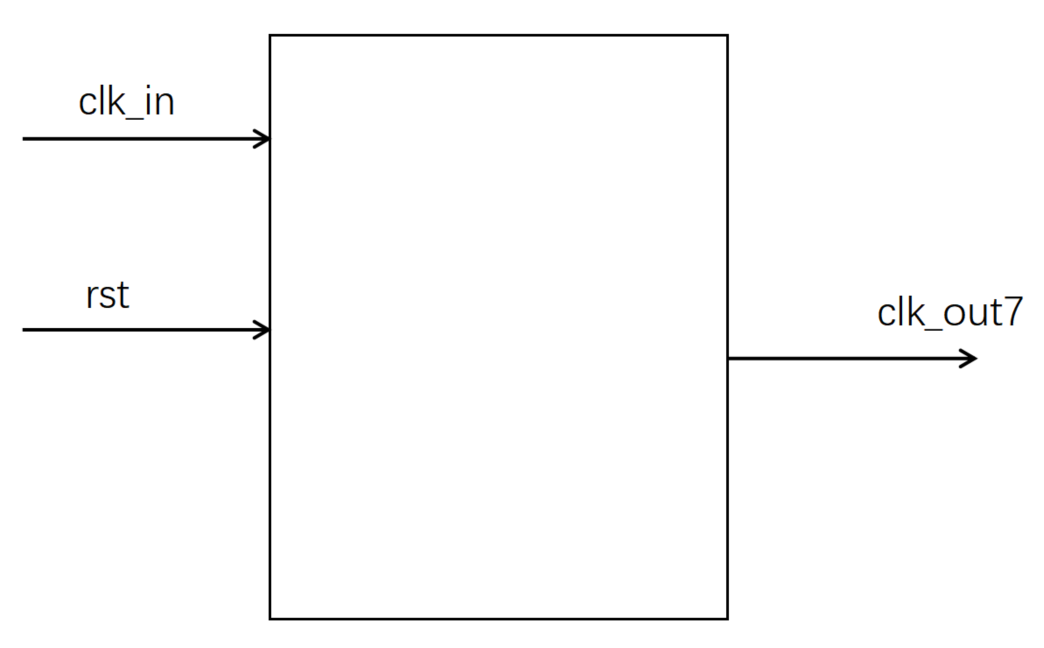

【FPGA学习笔记】VL40 占空比50%的奇数分频

设计一个同时输出7分频的时钟分频器,占空比要求为50%

注意rst为低电平复位

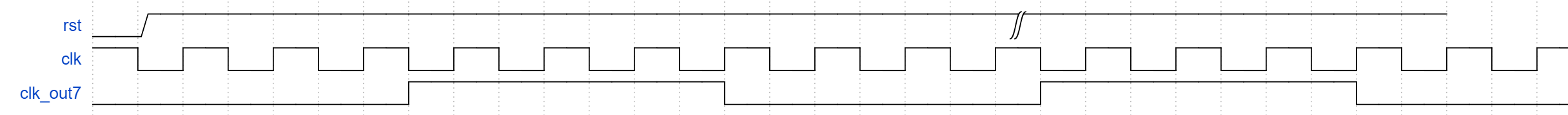

信号示意图:

clk_pos是周期为7且在clk_in上升沿翻转的信号, clk_neg是周期为7且在clk_in下降沿翻转的信号。

代码

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

|

`timescale 1ns/1nsmodule odo_div_or ( input wire rst , input wire clk_in, output wire clk_out7 );//*************code***********// reg clk_neg, clk_pos; reg [2:0] cnt; always@(posedge clk_in or negedge rst) begin if(~rst) cnt <= 0; else cnt <= cnt==6? 0: cnt+1; end always@(posedge clk_in or negedge rst) begin if(~rst) clk_pos <= 0; else clk_pos <= cnt==3||cnt==6? ~clk_pos: clk_pos; end always@(negedge clk_in or negedge rst) begin if(~rst) clk_neg <= 0; else clk_neg <= cnt==3||cnt==6? ~clk_neg: clk_neg; end assign clk_out7 = clk_neg|clk_pos;//*************code***********//endmodule |

浙公网安备 33010602011771号

浙公网安备 33010602011771号